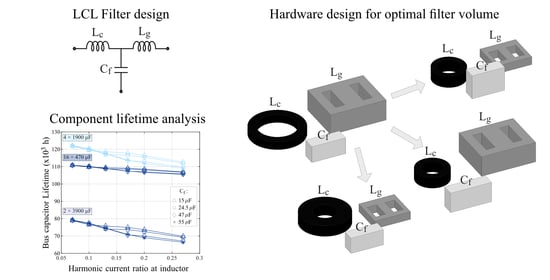

LCL Filter Parameter and Hardware Design Methodology for Minimum Volume Considering Capacitor Lifetimes

Abstract

:1. Introduction

2. Filter Parametric Design

2.1. Converter-Side Inductor

2.2. Grid-Side Inductor

3. Filter Hardware Design

3.1. Inductor Sizing

3.2. Capacitor Losses and Lifetime

4. Application of the Proposed Methodology

4.1. Filter Inductors and

4.2. Filter Capacitor

4.3. Bus Capacitors

5. Experimental Results

6. Conclusions

Author Contributions

Funding

Institutional Review Board Statement

Informed Consent Statement

Data Availability Statement

Conflicts of Interest

Nomenclature

| A | Dowell’s equation term for winding geometry |

| area of the winding conductor | |

| core cross-section area | |

| core area product (window and cross-section area product) | |

| area occupied by the wire turns | |

| core window area | |

| maximum magnetic flux density attributed to the core | |

| high frequency peak magnetic flux density of the gth minor loop | |

| low frequency peak magnetic flux density | |

| base capacitance | |

| bus capacitor | |

| total bus capacitance | |

| lower-half bus capacitance | |

| upper-half bus capacitance | |

| LCL filter capacitance | |

| energy processing capability of an inductor | |

| equivalent series resistance of a capacitor at the ith frequency | |

| f | frequency for which the conductor is designed |

| fringing flux factor for a center gap | |

| fringing flux factor for a side gap | |

| low frequency (60 Hz) | |

| resonant frequency | |

| switching frequency | |

| G | number of high frequency loops present on a low frequency period |

| H | last harmonic multiple considered in the summation |

| h | harmonic multiple of the fundamental frequency |

| frequency domain amplitude of the converter-side inductor current | |

| root mean square value of a bus capacitor current | |

| root mean square current of the filter capacitor | |

| frequency domain amplitude of the converter-side inductor current at the | |

| switching frequency | |

| ratio between the switching frequency and low frequency amplitudes of the | |

| converter-side inductor currents in the frequency domain | |

| frequency domain amplitude of the capacitor current, at the ith frequency | |

| frequency domain amplitude of the converter-side inductor current at the | |

| fundamental frequency | |

| frequency domain amplitude of the grid-side inductor current | |

| frequency domain amplitude of the grid-side inductor current at the | |

| switching frequency | |

| ratio between the switching frequency and low frequency amplitudes of the | |

| grid-side inductor currents in the frequency domain | |

| frequency domain amplitude of the grid-side inductor current at the | |

| fundamental frequency | |

| peak current value of an inductor | |

| rated current of a bus capacitor | |

| root mean square value of the current flowing through the inductor | |

| J | current density |

| zero order Bessel function | |

| high frequency Steinmetz coefficient k | |

| low frequency Steinmetz coefficient k | |

| temperature coefficient | |

| core window utilization factor | |

| converter-side inductor | |

| length of the winding | |

| magnetic path length | |

| grid-side inductor | |

| gap length | |

| specified or required inductance (either grid-side or converter-side) | |

| estimated lifetime of an bus capacitor | |

| estimated lifetime of the filter capacitor | |

| rated lifetime of a bus capacitor | |

| rated lifetime of the filter capacitor | |

| modulation index | |

| N | number of turns |

| temperature stress coefficient of a bus capacitor | |

| voltage stress factor of a bus capacitor | |

| voltage stress coefficient of the filter capacitor | |

| number of winding layers | |

| number of parallel wire strands | |

| exponential temperature coefficient | |

| p | winding pitch, or spacing between conductors |

| capacitor losses | |

| total core losses | |

| total bus capacitor losses | |

| filter capacitor losses | |

| high frequency core losses | |

| low frequency core losses | |

| copper losses | |

| power measured at the input | |

| estimated losses at the converter-side inductor | |

| estimated losses at the grid-side inductor | |

| total measured power loss | |

| total inductor losses | |

| estimated MOSFET losses | |

| power measured at the output | |

| damping resistor losses | |

| core reluctance | |

| winding AC resistance | |

| damping resistance | |

| thermal resistance of the capacitor | |

| ambient temperature | |

| capacitor core temperature | |

| temperature of the filter capacitor | |

| inductor temperature | |

| temperature limit of a magnetic material | |

| rated temperature of a bus capacitor | |

| rated temperature of the filter capacitor | |

| frequency domain amplitude of the converter-side voltage | |

| time domain converter-side voltage | |

| voltage over a bus capacitor | |

| voltage over the filter capacitor | |

| frequency domain amplitude of the converter-side voltage at the switching frequency | |

| DC bus voltage | |

| core volume | |

| grid voltage (root mean square value) | |

| rated voltage of a bus capacitor | |

| rated voltage of the filter capacitor | |

| wire gauge to be used for stranding | |

| low frequency steinmetz coefficent | |

| high frequency steinmetz coefficent | |

| low frequency steinmetz coefficent | |

| high frequency steinmetz coefficent | |

| skin depth | |

| inductor temperature rise | |

| temperature difference between iterations | |

| temperature rise of a bus capacitor at | |

| magnetic permeability of the air | |

| relative magnetic permeability of the core | |

| copper resistivity |

Appendix A. Inductor Hardware Design: Step-by-Step

References

- Channegowda, P.; John, V. Filter optimization for grid interactive voltage source inverters. IEEE Trans. Ind. Electron. 2010, 57, 4106–4114. [Google Scholar] [CrossRef]

- Gurrola-Corral, C.; Segundo, J.; Esparza, M.; Cruz, R. Optimal LCL-filter design method for grid-connected renewable energy sources. Int. J. Electr. Power Energy Syst. 2020, 120, 105998. [Google Scholar] [CrossRef]

- IEEE Std 519-2014; IEEE Recommended Practice and Requirements for Harmonic Control in Electric Power Systems. IEEE: New York, NY, USA, 2014; pp. 1–29.

- IEEE 1547-2018; IEEE Standard for Interconnection and Interoperability of Distributed Energy Resources with Associated Electric Power Systems Interfaces. IEEE: New York, NY, USA, 2018.

- IEC TS 61000-3-4:1998; Electromagnetic Compatibility (EMC)—Part 3-4: Limits—Limitation of Emission of Harmonic Currents in Low-Voltage Power Supply Systems for Equipment with Rated Current Greater Than 16 A. IEC: Geneva, Switzerland, 1998; pp. 1–29.

- Reznik, A.; Simões, M.G.; Al-Durra, A.; Muyeen, S. LCL filter design and performance analysis for grid-interconnected systems. IEEE Trans. Ind. Appl. 2013, 50, 1225–1232. [Google Scholar] [CrossRef]

- Liserre, M.; Blaabjerg, F.; Hansen, S. Design and control of an LCL-filter-based three-phase active rectifier. IEEE Trans. Ind. Appl. 2005, 41, 1281–1291. [Google Scholar] [CrossRef]

- Pena-Alzola, R.; Liserre, M.; Blaabjerg, F.; Ordonez, M.; Yang, Y. LCL-filter design for robust active damping in grid-connected converters. IEEE Trans. Ind. Inform. 2014, 10, 2192–2203. [Google Scholar] [CrossRef] [Green Version]

- Sanatkar-Chayjani, M.; Monfared, M. Design of LCL and LLCL filters for single-phase grid connected converters. IET Power Electron. 2016, 9, 1971–1978. [Google Scholar] [CrossRef] [Green Version]

- Subroto, R.K.; Tsai, C.H.; Lian, K.L.; Karimi, H. Active Resonance Damping for an Ultra Weak Grid-Connected Voltage Source Inverter with LCL Filter based on an Optimization and Sliding Mode Control. In Proceedings of the 2022 IEEE/IAS 58th Industrial and Commercial Power Systems Technical Conference (I&CPS), Las Vegas, NV, USA, 2–5 May 2022; pp. 1–10. [Google Scholar]

- Zeng, G.; Rasmussen, T.W.; Teodorescu, R. A novel optimized LCL-filter designing method for grid connected converter. In Proceedings of the 2nd International Symposium on Power Electronics for Distributed Generation Systems, Hefei, China, 16–18 June 2010; pp. 802–805. [Google Scholar]

- Jalili, K.; Bernet, S. Design of LCL filters of active-front-end two-level voltage-source converters. IEEE Trans. Ind. Electron. 2009, 56, 1674–1689. [Google Scholar] [CrossRef]

- Said-Romdhane, M.B.; Naouar, M.W.; Belkhodja, I.S.; Monmasson, E. An improved LCL filter design in order to ensure stability without damping and despite large grid impedance variations. Energies 2017, 10, 336. [Google Scholar] [CrossRef] [Green Version]

- Ahn, H.M.; Oh, C.Y.; Sung, W.Y.; Ahn, J.H.; Lee, B.K. Analysis and design of LCL filter with passive damping circuits for three-phase grid-connected inverters. In Proceedings of the 2015 9th International Conference on Power Electronics and ECCE Asia (ICPE-ECCE Asia), Seoul, Korea, 1–5 June 2015; pp. 652–658. [Google Scholar]

- Lee, K.J.; Park, N.J.; Kim, R.Y.; Ha, D.H.; Hyun, D.S. Design of an LCL filter employing a symmetric geometry and its control in grid-connected inverter applications. In Proceedings of the 2008 IEEE Power Electronics Specialists Conference, Rhodes, Greece, 15–19 June 2008; pp. 963–966. [Google Scholar]

- Kang, H.H.; Jo, H.R.; Lee, K.B. Analysis of LCL-Filter Performance in Three-level Full SiC NPC Inverters with Inductor Core Materials. J. Electr. Eng. Technol. 2022, 2022, 1–8. [Google Scholar] [CrossRef]

- Sun, W.; Chen, Z.; Wu, X. Intelligent optimize design of LCL filter for three-phase voltage-source PWM rectifier. In Proceedings of the 2009 IEEE 6th International Power Electronics and Motion Control Conference, Wuhan, China, 17–20 May 2009; pp. 970–974. [Google Scholar]

- Muhlethaler, J.; Schweizer, M.; Blattmann, R.; Kolar, J.W.; Ecklebe, A. Optimal design of LCL harmonic filters for three-phase PFC rectifiers. IEEE Trans. Power Electron. 2012, 28, 3114–3125. [Google Scholar] [CrossRef]

- Liu, Y.; Lai, C.M. LCL filter design with EMI noise consideration for grid-connected inverter. Energies 2018, 11, 1646. [Google Scholar] [CrossRef] [Green Version]

- Zhou, D.; Song, Y.; Liu, Y.; Blaabjerg, F. Mission profile based reliability evaluation of capacitor banks in wind power converters. IEEE Trans. Power Electron. 2018, 34, 4665–4677. [Google Scholar] [CrossRef]

- Cupertino, A.F.; Lenz, J.M.; Brito, E.M.; Pereira, H.A.; Pinheiro, J.R.; Seleme, S.I., Jr. Impact of the mission profile length on lifetime prediction of PV inverters. Microelectron. Reliab. 2019, 100, 113427. [Google Scholar] [CrossRef]

- Wang, H.; Li, C.; Zhu, G.; Liu, Y.; Wang, H. Model-Based Design and Optimization of Hybrid DC-Link Capacitor Banks. IEEE Trans. Power Electron. 2020, 35, 8910–8925. [Google Scholar] [CrossRef]

- Busquets-Monge, S.; Crebier, J.C.; Ragon, S.; Hertz, E.; Boroyevich, D.; Gurdal, Z.; Arpilliere, M.; Lindner, D.K. Design of a boost power factor correction converter using optimization techniques. IEEE Trans. Power Electron. 2004, 19, 1388–1396. [Google Scholar] [CrossRef]

- Helali, H.; Bergogne, D.; Slama, J.B.H.; Morel, H.; Bevilacqua, P.; Allard, B.; Brevet, O. Power converter’s optimisation and design. Discrete cost function with genetic based algorithms. In Proceedings of the 2005 European Conference on Power Electronics and Applications, Dresden, Germany, 11–14 September 2005; p. 7. [Google Scholar]

- De León-Aldaco, S.E.; Calleja, H.; Aguayo Alquicira, J. Metaheuristic Optimization Methods Applied to Power Converters: A Review. IEEE Trans. Power Electron. 2015, 30, 6791–6803. [Google Scholar] [CrossRef]

- Jabr, R. Application of geometric programming to transformer design. IEEE Trans. Magn. 2005, 41, 4261–4269. [Google Scholar] [CrossRef]

- Dai, M.; Marwali, M.N.; Jung, J.W.; Keyhani, A. A Three-Phase Four-Wire Inverter Control Technique for a Single Distributed Generation Unit in Island Mode. IEEE Trans. Power Electron. 2008, 23, 322–331. [Google Scholar] [CrossRef]

- Wang, X.; Blaabjerg, F.; Loh, P.C. Grid-current-feedback active damping for LCL resonance in grid-connected voltage-source converters. IEEE Trans. Power Electron. 2015, 31, 213–223. [Google Scholar] [CrossRef] [Green Version]

- Parker, S.G.; McGrath, B.P.; Holmes, D.G. Regions of active damping control for LCL filters. IEEE Trans. Ind. Appl. 2013, 50, 424–432. [Google Scholar] [CrossRef]

- DI-MAX M-13 Non-Oriented Electrical Steel; AK Steel Corporation: West Chester, OH, USA, 2019.

- Iron Powder Catalog; Magnetics Inc.: Pittsburgh, PA, USA, 2020.

- Soft Ferrites and Accessories Data Handbook; Ferroxcube: San Diego, CA, USA, 2013.

- Ma, K.; Wang, H.; Blaabjerg, F. New approaches to reliability assessment: Using physics-of-failure for prediction and design in power electronics systems. IEEE Power Electron. Mag. 2016, 3, 28–41. [Google Scholar] [CrossRef]

- Wang, H.; Blaabjerg, F. Reliability of capacitors for DC-link applications in power electronic converters—An overview. IEEE Trans. Ind. Appl. 2014, 50, 3569–3578. [Google Scholar] [CrossRef] [Green Version]

- C4AF Printed Circuit Board Mount Power Film Capacitors; KEMET Electronics Corporation: New Taipei City, Taiwan, 2021.

- Type DCMC 85 °C High Capacitance, Screw Terminal, Aluminum; Cornell Dubilier—CDE: Liberty, SC, USA, 2021.

- Matsumori, H.; Shimizu, T.; Blaabjerg, F.; Wang, X.; Yang, D. Stability Influence of Filter Components Parasitic Resistance on LCL-Filtered Grid Converters. In Proceedings of the 2018 International Power Electronics Conference (IPEC-Niigata 2018-ECCE Asia), Niigata, Japan, 20–24 May 2018; pp. 3357–3362. [Google Scholar]

- Lai, Y.S.; Su, Z.J.; Chen, W.S. New hybrid control technique to improve light load efficiency while meeting the hold-up time requirement for two-stage server power. IEEE Trans. Power Electron. 2013, 29, 4763–4775. [Google Scholar] [CrossRef]

- Prado, E.O.; Bolsi, P.C.; Sartori, H.C.; Pinheiro, J.R. Simple analytical model for accurate switching loss calculation in power MOSFETs using non-linearities of Miller capacitance. IET Power Electron. 2022, 15, 594–604. [Google Scholar] [CrossRef]

- Graovac, D.; Purschel, M.; Kiep, A. MOSFET power losses calculation using the data-sheet parameters. Infineon Appl. Note 2006, 1, 1–23. [Google Scholar]

- McLyman, C.W.T. Transformer and Inductor Design Handbook; CRC Press: Boca Raton, FL, USA, 2014. [Google Scholar]

- Wojda, R.P.; Kazimierczuk, M.K. Winding resistance and power loss of inductors with litz and solid-round wires. IEEE Trans. Ind. Appl. 2018, 54, 3548–3557. [Google Scholar] [CrossRef]

| Parameter | Value |

|---|---|

| Rated power | 15 kW |

| Switching frequency | 20 kHz |

| AC side voltage | 127 V/60 Hz |

| DC side voltage | 450 V |

| Parameter | Value |

|---|---|

| Rated power | 1 kW |

| Switching frequency | 20 kHz |

| AC side voltage | 127 V/60 Hz |

| DC side voltage | 430 V |

Publisher’s Note: MDPI stays neutral with regard to jurisdictional claims in published maps and institutional affiliations. |

© 2022 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Bolsi, P.C.; Prado, E.O.; Sartori, H.C.; Lenz, J.M.; Pinheiro, J.R. LCL Filter Parameter and Hardware Design Methodology for Minimum Volume Considering Capacitor Lifetimes. Energies 2022, 15, 4420. https://doi.org/10.3390/en15124420

Bolsi PC, Prado EO, Sartori HC, Lenz JM, Pinheiro JR. LCL Filter Parameter and Hardware Design Methodology for Minimum Volume Considering Capacitor Lifetimes. Energies. 2022; 15(12):4420. https://doi.org/10.3390/en15124420

Chicago/Turabian StyleBolsi, Pedro C., Edemar O. Prado, Hamiltom C. Sartori, João Manuel Lenz, and José Renes Pinheiro. 2022. "LCL Filter Parameter and Hardware Design Methodology for Minimum Volume Considering Capacitor Lifetimes" Energies 15, no. 12: 4420. https://doi.org/10.3390/en15124420