Abstract

In this work, a conventional HfO2 gate dielectric layer is replaced with a 3-nm ferroelectric (Fe) HZO layer in the gate stacks of advanced fin field-effect transistors (FinFETs). Fe-induced characteristics, e.g., negative drain induced barrier lowering (N-DIBL) and negative differential resistance (NDR), are clearly observed for both p- and n-type HZO-based FinFETs. These characteristics are attributed to the enhanced ferroelectricity of the 3-nm hafnium zirconium oxide (HZO) film, caused by Al doping from the TiAlC capping layer. This mechanism is verified for capacitors with structures similar to the FinFETs. Owing to the enhanced ferroelectricity and N-DIBL phenomenon, the drain current (IDS) of the HZO-FinFETs is greater than that of HfO2-FinFETs and obtained at a lower operating voltage. Accordingly, circuits based on HZO-FinFET achieve higher performance than those based on HfO2-FinFET at a low voltage drain (VDD), which indicates the application feasibility of the HZO-FinFETs in the ultra-low power integrated circuits.

Graphical abstract

摘要

由于铁电(Fe)栅介质的铁电场效应晶体管(FeFET)可以诱导出负电容效应且通过材料介电常数提升来获得更强的栅控作用,因而在器件开关中具有超陡的亚阈值摆幅(SS),有望实现超低功耗集成电路应用。其中,基于铪(Hf)基高k介质进行元素掺杂(锆(Zr)、硅(Si)、镧(La)等)的Fe材料由于可以在较薄尺寸(<20nm)下获得稳定铁电性并具有较高的CMOS兼容性从而近来获得较多关注。目前,研究人员已经报道了通过集成铪锆氧(HZO)薄膜所形成的FeFET技术,获得了较明显的负电容效应,如负漏极诱导势垒降低(N-DIBL)、负微分电阻(NDR)、突破玻尔兹曼极限的超陡亚阈值斜率(<60 mV·dec-1)等,进而促使器件性能得到显著提升。然而,由于在先进CMOS技术节点中存在栅堆叠层需小于5nm的厚度限制,并且现有小于5nm的超薄HZO薄膜表现出明显的铁电性退化现象,因此基于超薄常规HZO 薄膜的Fe-FinFET器件性能难以获得提升,这阻碍了FeFET在先进CMOS逻辑器件及电路中的应用。研究人员提出一种通过Al掺杂技术提升超薄3nm HZO薄膜铁电性的方案,并通过TiAlC金属栅功函数盖帽层扩散方法实现该技术在先进CMOS FinFET器件中的集成,进一步完成基于该器件的环振电路设计与制备。由于Al掺杂3-nm HZO铁电性的增强,该研究工作在较低操作电压下获得FinFET驱动电流增加,并在55阶环振电路上实现了19.9%的振荡频率提升。

Similar content being viewed by others

1 Introduction

Ferroelectric field-effect transistors (FeFETs) have the potential to achieve super-steep subthreshold swing (SS) or high driving currents suitable for ultra-low power consumption due to Fe dielectric layer induced negative capacitance and a high dielectric constant [1,2,3,4]. The most readily available Si complementary metal oxide semiconductor (CMOS)-compatible field-effect (FE) material is HfxZr1-xO2 (HZO), which has robust ferroelectricity and can be formed into thin films (< 20 nm), which may benefit scaling down of CMOS [5,6,7].

Recently, experimental evidence of performance enhancement and typical FE-induced characteristics, e.g., negative drain induced barrier lowering (N-DIBL), negative differential resistance (NDR), sub-60 mV·dec−1 of SSs, and improved on-state current have been reported for devices with thick HZO layers [8,9,10,11,12,13]. However, most typical characteristics are not obvious in advanced technology node logic devices based on ultra-thin HZO films in gate stacks, due to the weak ferroelectricity of thinner films. This effect has obstructed further exploration of super steep SS technology applied to advanced technology nodes [14,15,16,17,18]. Furthermore, although many experimental devices with HZO dielectrics have been reported, circuits based on FeFETs have rarely been demonstrated, and may yield improved performances on a circuit level [19,20,21].

In this work, ferroelectric fin field-effect transistors (Fe FinFETs) and circuits using the main-stream “gate-last process” were fabricated with integration of a 3 nm ultra-thin HZO layer into the gate stacks. The enhanced ferroelectricity of the 3 nm HZO film caused by Al doping from the TiAlC capping layer contributed to obvious performance improvements in Fe FinFETs-based CMOS devices and circuits.

2 Experimental

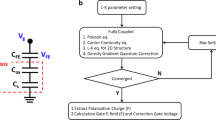

The process flow that was used to fabricate FinFET devices and circuits with HZO and HfO2 is illustrated in Fig. 1a. This basic process is similar to that used for developing n- and p-type devices on separate wafers [22, 23]. The FinFETs featuring a replacement metal gate were developed on the 200-mm Si (100) wafers. Initially, a self-aligned spacer image transfer technique was employed to pattern the fin morphology. Subsequently, standard procedures for punch-through stop doping (PTSD) and fin shallow trench isolation (STI) were adopted. Dummy gates constructed from amorphous silicon were fabricated using direct-write electron beam and dry etching techniques. After procedures for dummy gate planarization and removal had been carried out, atomic layer deposition (ALD) was applied to produce dual-work-function metal gates, which were used to set the threshold voltages (VT) of the n- and p-type FETs after fabrication of the interfacial layer (IL) and high-k dielectric layer. The diagrams in Fig. 1b demonstrate the intricate layered films of the n- and p-type devices. The uniform 3 nm thick HZO and HfO2 dielectric layers were produced through alternate incorporation of organic precursors based on Hf or Zr. The device contact processes for the source and drain (SD) W-plug and gate were applied to form the contact holes. Forming gas annealing (FGA) at 450 °C for 30 min was applied to the Al electrode of both devices with HZO crystallization.

Transmission electron microscope (TEM) imaging was used to examine the cross-sectional profiles of FinFETs. The electrical characterization was conducted using semiconductor parameter analyzers Keithley 4200 and Agilent 4156 C.

3 Results and discussion

3.1 Ferroelectricity enhancement of 3 nm HZO film

Figure 1c–e shows a schematic diagram, TEM images (cut across AA′), and energy dispersive X-ray spectroscopy (EDX) mappings of HZO-based FinFETs, respectively. Figure 1d shows that the fin had a top thickness of 4 nm and a height of approximately 70 nm. The interfacial layer (IL) and HZO layers were 1 and 3 nm thick, respectively, which gave superior gate control over the channel. Figure 1e shows the elements distribution of a p-type device, revealing the conformal work function metal layers around the entire 3D fins channel. Hf and Zr atoms concentrated in the medium layer, but Al diffused into the adjacent layers.

To verify the elemental diffusion, the distribution of the elements in the devices is shown in Fig. 2a. Elemental line scans (along BB′ in Fig. 1d) indicate obvious diffusion of Al into the TiN layer to form Al-doped TiN due to the strong diffuse tendency of Al atoms (especially considering the annealing process at 450 °C).

a Corresponding line scan for N, Al, Ti and Zr, respectively; b PUND results of current signals of HZO-based capacitor with Al-doped TiN; c comparison of Pr from capacitors with HZO/Al-TiN, HZO/TiN, and HfO/TiN; d XRD patterns of samples with and without Al-doped TiN; e schematic diagram of interactions between HZO films and Al-doped TiN and TiN capping layers

Figure 2b shows positive-up-negative-down (PUND) results measured using a voltage pulse (1 V, 50 μs) on an HZO-based capacitor with a similar structure to the gate stacks of the HZO-based FinFETs. The polarization switching current (Ips) and the non-switching current (Ins), which was measured during the application of the second voltage pulse, constitute the transient current (Is) arising from the application of the first voltage pulse [24]. By integrating the Ips signal, which is the difference between Is and Ins, the remnant polarization values are obtained. Accordingly, a comparison of the capacitances based on 3 nm HZO with Al-doped TiN and TiN electrodes is identified, as shown in Fig. 2c. Compared with the capacitance of the device with a TiN electrode, an improvement in the Pr value of approximately 20% was obtained with the Al-doped TiN electrode. Figure 2d shows XRD patterns of the 3 nm HZO films with Al-doped TiN and TiN capping layers. The orthorhombic phase was confirmed in both films. Furthermore, consistent with the PUND results, for the Al-doped TiN capping layers, the (111) peak was sharp and intense, indicating good crystallinity and chemical ordering [25,26,27]. This result is mainly attributed to the presence of AlOx at the interface that may facilitate HZO film crystallization, as shown in Fig. 2e, and has also been reported for other elemental oxides [28,29,30].

3.1.1 HZO-based devices results

The electrical characteristics of the FinFETs with 3-nm HfO and HZO were subsequently investigated. Figure 3a, c shows the transfer curves of both types of CMOS FinFETs at VDS of |100| mV (LIN) and |800| mV (SAT), respectively. Unlike the devices based on HfO2 as the dielectric layer, an obvious N-DIBL phenomenon was observed for the FinFET with 3-nm HZO due to its enhanced ferroelectricity. Importantly, owing to the N-DIBL effect, the IDS in the subthreshold region of the HZO-based devices was much larger than that of the FinFETs with HfO2.

a IDS-VGS curves of p-type HZO-based FinFET at various VDS; b extracted VT as a function of IDS of device in a; c IDS-VGS curves of n-type HZO-based FinFET at various VDS; d extracted VT as a function of IDS of device in c; measured IDS-VDS curves and NDR phenomenon of e n-type and f p-type FinFETs with 3-nm HZO; g, h extracted GDS as a function of VDS under various VGS for p- and n-type HZO-based FinFETs in e, f

To investigate the N-DIBL effects further, dual-sweep IDS-VGS curves were obtained over a range of VDS, and the extracted VT values for p- and n-type HZO-based FinFETs at various VDS biases are shown in Fig. 3b, d, respectively. The values of the VT@FOR and VT@REV decreased (increased) as VDS steadily increased for p-type (n-type) HZO-based FinFET, indicating the presence of the N-DIBL over almost the whole VDS range. In addition, the hysteresis (defined as VT@FOR − VT@REV) was negligible and very stable. Specifically, the hysteresis was stable at ~ 90 and ~ 110 mV for the n- and p-type HZO-based FinFETs with different VDS, respectively, which was much smaller than values of previously reported devices [21]. Furthermore, a clear negative differential resistance (NDR) stemming from the N-DIBL effect was also observed in the output curves of HZO-based CMOS devices (Fig. 3e, f for n- and p-type devices, respectively). In addition, the NDR phenomenon became more obvious at higher VGS, which was consistent with the conclusions of previous theoretical predictions [9, 10]. The extracted differential resistance, defined as GDS, as a function of VDS curves is illustrated in Fig. 3g, h, indicating that HZO-FinFETs with 3 nm ultra-thin HZO have a negative GDS. Specifically, for the p-type HZO-FinFET shown in Fig. 3g, when VGS is less than − 0.5 V, a low negative GDS occurs. As VGS increases to − 0.6 V, partial GDS values change from positive to negative. Notably, unlike the smooth GDS–VDS curves previously reported [9, 10], the GDS values appeared to fluctuate around 0 at higher VGS, which might indicate that the NC effect in this work was dynamic rather than static as previously reported [31–32]. Figure 3h shows that as VGS increases to 0.9 V, the partial GDS values also change from positive to negative in n-type devices which is consistent with the behavior of a p-type transistor.

Figure 4a shows the distribution of DIBLs for the HZO-based and HfO-based FinFETs over 60 devices. There are few N-DIBL characteristics for FinFETs based on conventional HfO2 films. However, The N-DIBL phenomenon was observed for almost all HZO-based FinFETs, indicating good uniformity and stability of the devices. The median values of DIBLs were − 0.003 and 0.012 V for HZO- and HfO2-FinFET devices, respectively. In addition to N-DIBL and NDR, the ferroelectric effect was also reflected in the improved SS, as shown in Fig. 4b. Although the SSs of FinFETs with a 3 nm ultra-thin HZO layer did not exceed the limit of 60 mV·dec−1, the subthreshold voltage switching characteristics of HfO2-based FinFETs were improved compared with those of the HfO2-FinFETs. The SS distribution in Fig. 4b indicates that the median SS was approximately 67.5 mV·dec−1 for the HZO-based FinFETs and 79.7 for the HfO2-based FinFETs mV·dec−1. Therefore, a decrease in the average SS of ∼12.2 mV·dec−1 was achieved for the Fe FinFETs.

Figure 4c, d shows ION-IOFF distributions of HZO- and HfO2-based FinFETs at 0.8 and 0.4 V VDD, respectively. The performance of the two types of devices was almost the same when VDD = 0.8 V. However, when VDS was decreased to 0.4 V, the off-current of the HZO-based FinFET decreased by an order of magnitude compared to that of the FinFET with a 3-nm HZO at the same level of on-current. This result is attributed to the obvious FE effects.

3.1.2 HZO-based FinFET circuits results

Figure 5a shows typical voltage transfer curves (VTC) of HZO- and HfO-based FinFETs CMOS inverters in a series of supply voltages. The maximum voltage gain of the two CMOS inverters exhibited little difference under high supply voltages. However, the voltage gain of the HZO-based FinFET inverter was greater than that of the controlled inverter when the supply voltage was lower than 0.6 V, which might have been caused by the higher IDS at lower VDDs due to N-DIBL phenomenon (Fig. 5b). These characteristics indicate the potential for the application of these devices in low-power integrated circuits. Additionally, Fig. 5d shows the output waveforms of 55-stage ring oscillators (ROs, Fig. 5c) for the HZO- and HfO-based FinFETs. The oscillation frequencies of the HfO-based and HZO-based FinFETs were 178 and 222 kHz, respectively. Owing to the performance of the HZO-based FinFETs, a 19.9% increase in oscillation frequency and a 16% reduction in delay per stage were achieved for the HZO-based FinFET circuits compared with those of circuits based on FinFET with 3 nm HZOs.

4 Conclusion

The ferroelectricity of ultra-thin 3-nm Hf0.5Zr0.5O2 film is increased by our proposed approach that involves the use of an Al-doped TiN electrode. The CMOS HZO-based FinFETs with Al-doped stacks show clear N-DIBL and NDR characteristics. Furthermore, the IDS values of HZO-based FinFETs were improved compared with those of a FinFET with 3 nm HfO2. Enhanced performance (i.e., higher gain of inverters at low VDD) was also confirmed in circuits based on HZO-based FinFETs, demonstrating the feasibility of these devices in ultra-low power applications.

References

Salahuddin S, Datta S. Use of negative capacitance to provide voltage amplification for low power nanoscale devices. Nano Lett. 2008;8(2):405. https://doi.org/10.1021/nl071804g.

Böscke TS, Müller J, Bräuhaus D, Schröder U, U. Böttger. Ferroelectricity in hafnium oxide: CMOS compatible ferroelectric field effect transistors. In: IEEE International Electron Devices Meeting. Washington; 2011;24.5.1. https://doi.org/10.1109/IEDM.2011.6131606.

Li YD, Zhang ZH, Yan J, Tang B, Zhang QZ, Luo J. Fabrication of ultra-thin Hf0.5Zr0.5O2 film and its application on ETSOI devices. Chin J Rare Met. 2022;46(4):480. https://doi.org/10.13373/j.cnki.cjrm.XY20020023.

Zhang MH, Qi JL, Liu YQ, Lan S, Luo ZX, Pan H, Lin YH. High energy storage capability of perovskite relaxor ferroelectrics via hierarchical optimization. Rare Met. 2022;41(3):730. https://doi.org/10.1007/s12598-021-01869-z.

Zhang Z, Li Y, Xu J, Tang B, Xiang J, Li J, Wang W. Improved subthreshold characteristics by back-gate coupling on ferroelectric ETSOI FETs. Nanoscale Res Lett. 2022;17:124. https://doi.org/10.1186/s11671-022-03767-4.

Zhang Z, Gan W, Li KZ, Han Y, Liu Y, Wang G, Wu Z, Yu J, Zhang Q, Xu G, Zhang Y, Xiang J, Yin H, Luo J, Wang W. Scallop-shaped p-type FinFETs with improved short-channel effects immunity and driving current. Mater Sci Semiconductor Process. 2022;140(8):106337. https://doi.org/10.1016/j.mssp.2021.106337.

Zhang Q, Gu J, Xu R, Cao L, Li J, Wu Z, Wang G, Yao J, Zhang Z, Xiang J, He X, Kong Z, Yang H, Tian J, Xu G, Mao S, Radamson HH, Yin H, Luo J. Optimization of structure and electrical characteristics for four-layer vertically-stacked horizontal gate-all-around Si nanosheets devices. Nanomaterials. 2021;11(3):646. https://doi.org/10.3390/nano11030646.

Zhang Z, Xu G, Zhang Q, Hou Z, Li JJ, Kong Z, Zhang Y, Xiang Ji XuQ, Wu Z, Zhu H, Yin HX, Wang W, Ye TC. FinFET with improved subthreshold swing and drain current using 3 nm FE Hf0.5Zr0.5O2. IEEE Electron Device Lett. 2019;40(3):367. https://doi.org/10.1109/LED.2019.2891364.

Zhou J, Han G, Li J, Liu Y, Peng Y, Zhang J, Sun QQ, Zhang DW. Negative differential resistance in negative capacitance FET. IEEE Electron Device Lett. 2018;39(4):622. https://doi.org/10.1109/LED.2018.2810071.

Zhou J, Han G, Li Q, Peng Y, Lu X, Zhang C, Zhang J, Sun QQ, Zhang DW, HaoY. Ferroelectric HfZrOx Ge and GeSn PMOSFETs with Sub-60 mV·dec-1 subthreshold swing, negligible hysteresis, and improved Ids. In: the 62nd IEEE International Electron Devices Meeting. San Francisco; 2016. 2.2.1. https://doi.org/10.1109/IEDM.2016.7838401.

Li KS, Chen PG, Lai TY, Lin CH, Cheng CC, Wei YJ, Hou YF, Liao MH, Lee MH, Chen MC, Yeh WK, Yang FL, Salahuddin S, Hu C. In: the 61st IEEE International Electron Devices Meeting. Washington; 2015. 22.6.1. https://doi.org/10.1109/IEDM.2015.7409760.

Lee MH, Chen PG, Liu C, Chu KY, Cheng CC, Xie MJ, Liu SN, Lee JW, Huang SJ, Liao MH, Tang M, Li KS, Chen M.-C. Prospects for ferroelectric HfZrOx FETs with experimentally CET=0.98nm, SSfor=42mV·dec-1, SSrev=28mV·dec-1, switch-off <0.2V, and hysteresis-free strategies. In: the 61st IEEE International Electron Devices Meeting. Washington; 2015. 22.5.1. https://doi.org/10.1109/IEDM.2015.7409759.

Lee MH, Fan ST, Tang CH, Chen PG, Chou YC, Chen HH, Kuo JY, Xie MJ, Liu SN, Liao MH, Jong CA, Li KS, Chen MC, Liu CW. Physical thickness 1.x nm ferroelectric HfZrOx negative capacitance FETs. In: the 62nd IEEE International Electron Devices Meeting. San Francisco; 2016. 12.1.1. https://doi.org/10.1109/IEDM.2016.7838400.

Zhang Z, Luo Y, Cui Y, Yang H, Zhang Q, Xu G, Wu Z, Xiang J, Liu Q, Yin H, Mao S, Wang X, Li J, Zhang Y, Luo Q, Gao J, Xiong W, Liu J, Li Y, Li J, Luo J, Wang W. A polarization-switching, charge-trapping, modulated arithmetic logic unit for in-memory computing based on ferroelectric fin field-effect transistors. ACS Appl Mater Interfaces. 2022;14(5):6967. https://doi.org/10.1021/acsami.1c20189.

Hu V P H, Chiu P C, Sachid A B. Negative capacitance enables FinFET and FDSOI scaling to 2 nm node. In: 63rd IEEE International Electron Devices Meeting. San Francisco; 2017. 23.1.1. https://doi.org/10.1109/IEDM.2017.8268443.

Li YD, Zhang QZ, Liu FY, Zhang ZH, Zhang FY, Zhao HB, Yan J. X-ray irradiation-induced degradation in Hf0.5Zr0.5O2 fully depleted silicon-on-insulator n-type metal oxide semiconductor field-effect transistors. Rare Met. 2021;40(11):3299. https://doi.org/10.1007/s12598-020-01586-z.

Chouprik A, Chernikova A, Markeev A, Mikheev V, Negrov D, Spiridonov M, Zarubin S, Zenkevich A. Electron transport across ultrathin ferroelectric Hf0.5Zr0.5O2 films on Si. Microelectr Eng. 2017;178:250. https://doi.org/10.1016/j.mee.2017.05.028.

Lyu X, Si M, Sun X, Capano M. A, Wang H. Ye P. D. Ferroelectric and anti-ferroelectric hafnium zirconium oxide: scaling limit, switching speed and record high polarization density. In: the 39th Symposium on VLSI Technology. Kyoto; 2019. T44. https://doi.org/10.23919/VLSIT.2019.8776548.

Chung W, Si M, Ye PD. Hysteresis-free negative capacitance germanium CMOS FinFETs with Bi-directional Sub-60 mV·dec-1. In: the 63rd IEEE International Electron Devices Meeting. San Francisco; 2017. 15.3.1. https://doi.org/10.1109/IEDM.2017.8268395.

Krivokapic Z, Rana U, Galatage R, Razavieh A, Aziz A, Liu J, Shi J, Kim HJ, Sporer R, Serrao C, Busquet A, Polakowski P, Müller J, Kleemeier W, Jacob A, Brown D, Knorr A, Carter R, Banna S. 14nm Ferroelectric FinFET technology with steep subthreshold swing for ultra-low power applications. In: the 63rd IEEE International Electron Devices Meeting. San Francisco; 2017. 15.1.1. https://doi.org/10.1109/IEDM.2017.8268393.

Li KS, Wei YJ, Chen YJ, Chiu WC, Chen HC, Lee MH, Chiu YF, Hsueh FK, Wu BW, Chen PG, Lai TY, Chen CC, Shieh JM, Yeh WK, Salahuddin S, Hu C. Negative-capacitance FinFET inverter, ring oscillator, SRAM cell, and Ft. In: the 64th Annual IEEE International Electron Devices Meeting. San Francisco; 2018. 31.7.1. https://doi.org/10.1109/IEDM.2018.8614521.

Zhang Q, Yin H, Luo Jun, Yang H, Meng L, Li Y, Wu Z, Zhang Y, Zhang Y. FOI FinFET with ultra-low parasitic resistance enabled by fully metallic source and drain formation on isolated bulk-fin. In: the 62th Annual IEEE International Electron Devices Meeting. San Francisco; 2016. 17.3.1. https://doi.org/10.1109/IEDM.2016.7838438.

Zhang Q, Yin H, Meng L, Yao J, Li J, Wang G, Li Y, Wu Z, Xiong W, Yang H, Tu H, Li J, Zhao C, Wang W, Ye T. Novel GAASi nanowire p-MOSFETs with excellent short-channel effect immunity via an advanced forming process. IEEE Electron Device Lett. 2018;39(4):464. https://doi.org/10.1109/LED.2018.2807389.

Chernikova A, Kozodaev M, Markeev A, Negrov D, Spiridonov M, Zarubin S, Bak O, Buragohain P, Lu H, Suvorova E, Gruverman A, Zenkevich A. Ultrathin Hf0.5Zr0.5O2 ferroelectric films on Si. ACS Appl Mater Interfaces. 2016;8(11):7232. https://doi.org/10.1021/acsami.5b11653.

Zhang X, Qin PX, Feng ZX, Yan H, Wang XN, Zhou XR, Wu HJ, Chen HY, Meng ZA, Liu ZQ. Epitaxial integration of a perpendicularly magnetized ferrimagnetic metal on a ferroelectric oxide for electric-field control. Rare Met. 2022;41(5):1554. https://doi.org/10.1007/s12598-021-01898-8.

Li Y, Tang MY, Zhang ZG, Yan H, Wang XN, Zhou XR, Wu HJ, Chen HY, Meng ZA, Liu ZQ. BaTiO3-based ceramics with high energy storage density. Rare Met. 2023;42(4):1261. https://doi.org/10.1007/s12598-022-02175-y.

Yao MC, Wu XJ, Xu LL, Meng FZ, Yang Q, Meng J, Liu XJ. Beta-CuGaO2: a ferroelectric semiconductor with narrow band gap as degradation catalyst for wastewater environmental remediation. Rare Met. 2022;41(3):972. https://doi.org/10.1007/s12598-021-01832-y.

Tian G, Xu G, Yin H, Yan G, Zhang Z, Li L, Wang W. Improved ferroelectricity and endurance of Hf0.5Zr0.5O2 thin films in low thermal budget with novel bottom electrode doping technology. Adv Mater Interfaces. 2022;9(24):2102351. https://doi.org/10.1002/admi.202102351.

Gougousi T. Low-temperature dopant-assisted crystallization of HfO2 thin films. Cryst Growth Des. 2021;21:11. https://doi.org/10.1021/acs.cgd.1c00875.

Gougousi T, Hackley JC, Demaree JD, Lacis JW. Growth J interface evolution of HfO2 films on GaAs (100) surfaces. Electrochem Soc. 2010;157:55. https://doi.org/10.1149/1.3353166.

Li X, Toriumi A. Direct relationship between sub-60 mV dec-1 subthreshold swing and internal potential instability in MOSFET externally connected to ferroelectric capacitor. In: the 64th Annual IEEE International Electron Devices Meeting. San Francisco; 2018. 31.3.1. https://doi.org/10.1109/IEDM.2018.8614703.

Acknowledgements

This work was financially supported by the Science and Technology Program of Beijing Municipal Science and Technology Commission (No. Z201100006820084), the National Natural Science Foundation of China (Nos. 92064003, 91964202 and 61904194) and the Youth Innovation Promotion Association, Chinese Academy of Sciences under grant (Nos. 2023130 and Y9YQ01R004).

Author information

Authors and Affiliations

Corresponding authors

Ethics declarations

Conflict of interests

The authors declare that they have no conflict of interest.

Rights and permissions

Open Access This article is licensed under a Creative Commons Attribution 4.0 International License, which permits use, sharing, adaptation, distribution and reproduction in any medium or format, as long as you give appropriate credit to the original author(s) and the source, provide a link to the Creative Commons licence, and indicate if changes were made. The images or other third party material in this article are included in the article's Creative Commons licence, unless indicated otherwise in a credit line to the material. If material is not included in the article's Creative Commons licence and your intended use is not permitted by statutory regulation or exceeds the permitted use, you will need to obtain permission directly from the copyright holder. To view a copy of this licence, visit http://creativecommons.org/licenses/by/4.0/.

About this article

Cite this article

Zhang, ZH., Luo, YN., Xu, GB. et al. Performance improvements in complementary metal oxide semiconductor devices and circuits based on fin field-effect transistors using 3-nm ferroelectric Hf0.5Zr0.5O2. Rare Met. (2024). https://doi.org/10.1007/s12598-024-02674-0

Received:

Revised:

Accepted:

Published:

DOI: https://doi.org/10.1007/s12598-024-02674-0