Abstract

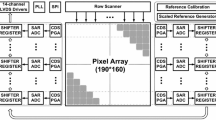

This paper presents an adderless feed-forward incremental \(\varDelta \varSigma \) (I\(\varDelta \varSigma \)) with asynchronous SAR (ASAR) that removes the need for in-column calibration by using global references, eliminates an additional summing amplifier and reduces the conversion time by using a multi-bit ASAR quantizer. The proposed I\(\varDelta \varSigma \) ADC is designed in 40 nm CMOS technology and is laid out compactly in a 5 \(\upmu \)m × 466 \(\upmu \)m column. According to post-layout simulations, the ADC achieves an input-referred noise of 85 \(\upmu \)V\(_{ rms }\), a conversion time of 3.2 \(\upmu \)s (with DCDS) and a power consumption of 230 \(\upmu \)W. This results in a Walden FoM\(_{\textrm{W}}\) of 234 fJ/conv.step and a FoM\(_{\textrm{A}}\) = FoM\(_{\textrm{W}} \times \text {A}_{\text {ADC}}\) of 0.54 fJ\(\cdot \)mm\(^2\)/conv.step, which demonstrates the feasibility of using the proposed architecture in CMOS image sensors.

Similar content being viewed by others

References

Callens, N., & Gielen, G. G. (2021). Analysis and comparison of readout architectures and analog-to-digital converters for 3D-stacked CMOS image sensors. IEEE Transactions on Circuits and Systems I: Regular Papers, 68, 3117–3130.

Nitta, Y., Muramatsu, Y., Amano, K., Toyama, T., Mishina, K., Suzuki, A., Taura, T., Kato, A., Kikuchi, M., Yasui, Y., others. (2006). High-speed digital double sampling with analog CDS on column parallel ADC architecture for low-noise active pixel sensor. In 2006 IEEE International Solid State Circuits Conference-Digest of Technical Papers (pp. 2024–2031).

Funatsu, R., Huang, S., Yamashita, T., Stevulak, K., Rysinski, J., Estrada, D., Yan, S., Soeno, T., Nakamura, T., Hayashida, T., others. (2015). 133Mpixel 60fps CMOS image sensor with 32-column shared high-speed column-parallel SAR ADCs. In 2015 IEEE International Solid-State Circuits Conference-(ISSCC) Digest of Technical Papers (pp. 1–3).

Furuta, M., Nishikawa, Y., Inoue, T., & Kawahito, S. (2007). A high-speed, high-sensitivity digital CMOS image sensor with a global shutter and 12-bit column-parallel cyclic A/D converters. IEEE Journal of Solid-State Circuits, 42(4), 766–774.

Chae, Y., Cheon, J., Lim, S., Kwon, M., Yoo, K., Jung, W., Lee, D.-H., Ham, S., & Han, G. (2010). A 2.1 MPixels, 120 frame/s CMOS image sensor with column-parallel \(\Delta \Sigma \) ADC architecture. IEEE Journal of Solid-State Circuits, 46(1), 236–247.

Lee, I., Kim, B., & Lee, B.-G. (2015). A low-power incremental \(\Delta \Sigma \) ADC for CMOS image sensors. IEEE Transactions on Circuits and Systems II: Express Briefs, 63(4), 371–375.

Liu, Y., Bonizzoni, E., Maloberti, F. (2013). High-order multi-bit incremental converter with smart-DEM algorithm. In 2013 IEEE International Symposium on Circuits and Systems (ISCAS) (pp. 157–160). IEEE.

Xhakoni, A. (2015). High-frame-rate and high-dynamic-range imager readout circuits for CIS and stacked technology.

Gharbiya, A., & Johns, D. A. (2006). On the implementation of input-feedforward \(\Delta \Sigma \) modulators. IEEE Transactions on Circuits and Systems II: Express Briefs, 53(6), 453–457.

Tan, Z., Chen, C.-H., Chae, Y., & Temes, G. C. (2020). Incremental delta-sigma ADCs: A tutorial review. IEEE Transactions on Circuits and Systems I: Regular Papers, 67(12), 4161–4173.

Jung, Y., Roh, H., & Roh, J. (2013). An input-feedforward multibit adder-less \(\Delta \Sigma \) modulator for ultrasound imaging systems. IEEE Transactions on Instrumentation and Measurement, 62(8), 2215–2227.

Honarparvar, M., De La Rosa, J., Nabki, F., & Sawan, M. (2017). SMASH \(\Delta \Sigma \) modulator with adderless feed-forward loop filter. Electronics Letters, 53(8), 532–534.

González, C. A. (2019). Digital background self-calibration technique for compensating transition offsets in reference-less flash ADCs. Ph.D. dissertation, Universidad de Sevilla.

Chen, S.-W.M., & Brodersen, R. W. (2006). A 6-bit 600-MS/s 5.3-mW asynchronous ADC in 0.13-\(\upmu \)m CMOS. IEEE Journal of Solid-State Circuits, 41(12), 2669–2680.

Malcovati, P., Brigati, S., Francesconi, F., Maloberti, F., Cusinato, P., & Baschirotto, A. (2003). Behavioral modeling of switched-capacitor sigma-delta modulators. IEEE Transactions on Circuits and Systems I: Fundamental Theory and Applications, 50(3), 352–364.

Agah, A., Vleugels, K., Griffin, P. B., Ronaghi, M., Plummer, J. D., & Wooley, B. A. (2010). A high-resolution low-power incremental \(\Delta \Sigma \) ADC with extended range for biosensor arrays. IEEE Journal of Solid-State Circuits, 45(6), 1099–1110.

Wu, B., Zhu, S., Xu, B., & Chiu, Y. (2016). A 24.7 mW 65 nm CMOS SAR-assisted CT \(\Delta \Sigma \) modulator with second-order noise coupling achieving 45 MHz bandwidth and 75.3 dB SNDR. IEEE Journal of Solid-State Circuits, 51(12), 2893–2905.

Márkus, J., Silva, J., & Temes, G. C. (2004). Theory and applications of incremental \(\Delta \Sigma \) converters. IEEE Transactions on Circuits and Systems I: Regular Papers, 51(4), 678–690.

Xhakoni, A., Le-Thai, H., Geurts, T., Chapinal, G., & Gielen, G. (2014). PTC-based sigma-delta ADCs for high-speed, low-noise imagers. IEEE Sensors Journal, 14(9), 2932–2933.

Jo, Y.-R., Hong, S.-K., & Kwon, O.-K. (2015). A multi-bit incremental ADC based on successive approximation for low noise and high resolution column-parallel readout circuits. IEEE Transactions on Circuits and Systems I: Regular Papers, 62(9), 2156–2166.

Jo, Y.-R., Hong, S.-K., & Kwon, O.-K. (2015). A low-noise and area-efficient PWM-\(\Delta \Sigma \) ADC using a single-slope quantizer for CMOS image sensors. IEEE Transactions on Electron Devices, 63(1), 168–173.

Jo, Y.-R., Hong, S.-K., & Kwon, O.-K. (2021). A 12 bit 4.7-MS/s 260.5-\(\upmu \)W digital feed-forward incremental-\(\Sigma \Delta \)-SAR ADC in 0.13-\(\upmu \)m CMOS for image sensors. IEEE Sensors Journal, 21(19), 21653–21666.

Xie, S., Ge, X., Theuwissen, A. (2019). Temperature sensors incorporated into a CMOS image sensor with column zoom ADCs. In 2019 IEEE International Symposium on Circuits and Systems (ISCAS) (pp. 1–5).

Lee, S., Jeong, J., Kim, T., Park, C., Kim, T., & Chae, Y. (2020). A 5.2-Mpixel 88.4-dB DR 12-in CMOS X-ray detector with 16-bit column-parallel continuous-time incremental \(\Delta \Sigma \) ADCs. IEEE Journal of Solid-State Circuits, 55(11), 2878–2888.

Funding

This work is supported by the VLAIO HENESIS project in collaboration with ams OSRAM (Belgium).

Author information

Authors and Affiliations

Contributions

Nicolas Callens and Georges Gielen wrote the main manuscript.

Corresponding author

Ethics declarations

Conflict of interest

The authors declare no competing interests.

Additional information

Publisher's Note

Springer Nature remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

Rights and permissions

Springer Nature or its licensor (e.g. a society or other partner) holds exclusive rights to this article under a publishing agreement with the author(s) or other rightsholder(s); author self-archiving of the accepted manuscript version of this article is solely governed by the terms of such publishing agreement and applicable law.

About this article

Cite this article

Callens, N., Gielen, G. A compact adderless feed-forward incremental \(\varDelta \varSigma \) with multiple global references for CMOS image sensors. Analog Integr Circ Sig Process 118, 1–13 (2024). https://doi.org/10.1007/s10470-023-02186-4

Received:

Revised:

Accepted:

Published:

Issue Date:

DOI: https://doi.org/10.1007/s10470-023-02186-4