Abstract

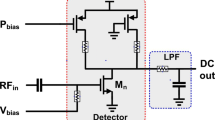

In this paper we present two designs of CMOS blocks suitable for integration with RF frontend blocks for test purposes. Those are a programmable RF test attenuator and a reconfigurable low noise amplifier (LNA), optimized with respect to their function and location in the circuit. We discuss their performances in terms of the test- and normal operation mode. The presented application model aims at a transceiver under loopback test with enhanced controllability and detectability. The circuits are designed for 0.35μm CMOS process. Simulation results of the receiver frontend operating in 2.4 GHz band are presented showing tradeoffs between the performance and test functionality.

Similar content being viewed by others

References

L. Milor, “A tutorial introduction to research on analog and mixed-signal circuit testing.” IEEE Transactions on CAS-II: Analog and Digital Signal Proceeding, vol. 45, no. 10, pp. 1398–1407, 1997.

A. Grochowski, et al., “Integrated circuits testing for quality assurance in manufacturing: History.” IEEE Transacstion on CAS-II: Analog and Digital Signal Proceeding, vol. 44, no. 8, pp. 610–633, 1997.

M. Heutmaker and D. Le, “An architecture for self-test of a wireless communication system using sampled IQ modulation and boundary scan.” IEEE Communication Mag., pp. 98–102, 1999.

D. Lupea, et al., “RF Bist: Loopback spectral signature analysis.” Proc. DATE’03, pp. 6.

G. Srinivasan et al., “Loopback test of RF transceivers using periodic bit sequences.” Proc. IMSTW’04, pp. 6

J. Dabrowski and J. Gonzalez Bayon, “Mixed loop-back BIST for RF digital transceivers.” Proc. DFT’04, pp. 220–228.

J.-S. Yoon and W.R. Eisenstadt, “Embedded loop-back test for RF Ics.” IEEE Transaction on Instrumentation and Measurement, vol. 54, no. 5, 2005.

Y. Xing, “Defect-oriented testing of mixed-signal Ics.” Proc. ITC’98, pp. 678–687.

“Using error vector magnitude measurements.” Agilent PN 89400-14.

B. Razavi, RF Microelectronics, Prentice Hall, 1998.

B.G. Yoo, J.H. Huh, and S.W. Kim, “A design of DC-2 GHz linear-controlled CMOS attenuator.” Proc. EDMO’2002, pp. 107–110.

R. Kaunisto et al., “A linear-control wide-band CMOS attenuator.” Proceeding of ISCAS, vol. 4, pp. 458–461, 2001.

T. Kantasuwan, R. Ramzan, and J. Dąbrowski, “Programmable RF attenuator for on-chip loop-back test.” Proc. ETS’2005, pp. 6.

R.M. Ramzan and J. Dąbrowski, “CMOS blocks for on-chip RF test.” Proc MIXDES’05, Krakow, Poland, pp. 403–408.

P. Leroux and M. Steyaert “High-performance 5.2 GHz LNA with on-chip inductor to provide ESD protection.” Electronics Letters, vol. 37, no. 7, pp. 467–469, 2001.

Thomas H. Lee, The Design of CMOS Radio-Frequency Integrated Circuits, 2nd Ed, Cambridge University Press, 2004.

Author information

Authors and Affiliations

Corresponding author

Additional information

Rashad M. Ramzan did his graduation in Electrical Engineering with Honors from University of Engineering and Technology Lahore, Pakistan in 1994. After Graduation he joined Advanced Engineering Research Organization and worked on low noise electronics, micro-processors, micro-controller, SMPS and PCB design for more than four years. In 1999 he joined Enabling Technology Islamabad, a branch office of the same company in Irvine CA. At Enabling Technology, he was a part of the team who designed a media processing ASIC for VoIP application for future IP enabled exchanges. He did his masters in SoC design from Royal Institute of Technology (KTH), Stockholm. Currently he is working toward his Ph.D degree in testable and reconfigurable RF circuits. His reaserch interests are mainly focused on RF circuits, fully integrated transceivers, design for testability and high speed PCB design.

Jerzy J. Dąbrowski received the Ph.D. and D.S. degrees form Silesian University of Technology (SUT), Gliwice, Poland, in 1987 and 2001, respectively. He has specialized in macromodeling and simulation of analog and mixed-signal circuits. Currently, he is an Associate Professor at Linköping University, Sweden, and at SUT, Gliwice. His recent research interests are also in RF ICs design and design-for-testability for analog/RF circuits. He has published over 70 research papers in international journals and conference proceedings. He holds 12 patents (as a coauthor) in switched-mode power supplies and instrumentation circuits. He is a member of IEEE, PTETiS and the Commission of Electronics PAN (Poland).

Rights and permissions

About this article

Cite this article

Ramzan, R., Dąbrowski, J. CMOS blocks for on-chip RF test. Analog Integr Circ Sig Process 49, 151–160 (2006). https://doi.org/10.1007/s10470-006-9615-2

Received:

Revised:

Accepted:

Published:

Issue Date:

DOI: https://doi.org/10.1007/s10470-006-9615-2