Abstract

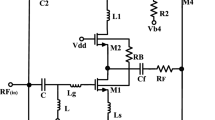

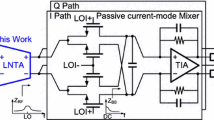

This study presents a wideband low-noise amplifier (LNA) chip that covers the frequency range of 2.8–10 GHz using UMC’s 0.18 μm complementary metal–oxide–semiconductor technology. The LNA adopts a current reuse architecture to reduce power consumption. This study improves linearity using multiple gated transistors and inductance degeneration techniques. In addition to enhancing linearity, the proposed technique also achieves high gain and broadband. The DC power dissipation of this LNA was 18 mW with a 1.5 V supply voltage. The measured minimum noise figure was 4.5 dB. Furthermore, the gain, input third-order intercept point, and total chip size of the LNA were 10.8–13.8 dB, 2 dBm, and 1.18 × 1.19 mm2, respectively. The proposed LNA measurements exhibit high linearity, high gain, an optimal reflection coefficient, and a low supply voltage.

Similar content being viewed by others

References

S. Ali, J. Sobhi, Z.D. Koozehkanani, Linearity improvement of gm-boosted common gate LNA: analysis to design. Microelectron. J. 56, 156–162 (2016)

A. Alizadeh, M. Meghdadi, M. Yaghoobi, A. Medi, Design of a 2–12-GHz bidirectional distributed amplifier in a 0.18-μm CMOS technology. IEEE Trans. Microw. Theory Tech. 67(2), 754–764 (2018)

M. Cen, S. Song, A high gain, low-power low-noise amplifier for ultra-wideband wireless systems. Circuits Syst. Signal Process. 33(10), 3251–3262 (2014)

C.P. Chang, H.R. Chung, 018-μm 3–6 GHz CMOS broadband LNA for UWB radio. IEE Electron. Lett. 41(12), 696–698 (2005)

J.F. Chang, Y.S. Lin, 3–9 GHz CMOS LNA using body floating and self- bias technique for sub-6 GHz 5G communications. IEEE Microwave Wirel. Compon. Lett. 31(6), 608–611 (2021)

J.F. Chang, Y.S. Lin, Complementary current-reused 3.7–11.9 GHz LNA using body-floating and self-bias technique for sub-6 Ghz 5g communications. Circuits Syst Signal Process 25, 87 (2022)

Y.E. Chen, Y.I. Huang, Development of integrated broad-band CMOS low-noise amplifiers. IEEE Trans. Circuits Syst. I., Reg Papers 54(10), 2120–2126 (2007)

L. Chen, C. Shi, R. Zhang, Y. Ruan, Z. Lai, An ultra-wide-band 3.1–10.6 GHz LNA design in 0.18 μm SiGe BiCMOS. AEU-Int. J. Electron. Commun. 66(2), 157–161 (2012)

C.C. Chen, Y.C. Wang, A dual-wideband CMOS LNA using gain-bandwidth product optimization technique. Circuits Syst. Signal Process. 36(2), 495–510 (2017)

C.C. Chen, Y.C. Wang, 24/52/58 GHz triple-band common-gate cascode CMOS low-noise amplifier. Circuits Syst. Signal Process. 36(9), 3477–3490 (2017)

J.D. Chen, M.K. Jian, 15–7 GHz wideband low-voltage low-power switched transconductor up-conversion mixer. AEU-Int. J. Electron. Commun. 134, 153681 (2021)

J.G. Cheng, Z. Li, L. Luo, Z. Wang, A 2–3 GHz high gain and high linearity current-reused LNA with wideband input matching, in International Conference On Communication Problem-Solving (2016), pp.1–2.

G. Cheng, Z. Li, L. Luo, Z. Wang, X. He, B. He, A low power and high gain current-reused LNA using cascaded L-type input matching network. Microelectron. J. 75, 15–26 (2018)

B.C. Chye, D.M. Anh, Y.K. Seng, A 3–8 GHz Low-Noise CMOS Amplifier. IEEE Microw. Wireless Compon. Lett. 19(4), 245–247 (2009)

X. Guan, C. Nguyen, Low-power-consumption and high-gain CMOS distributed amplifiers using cascade of inductively coupled common-source gain cells for UWB systems. IEEE Trans. Microw. Theory Tech. 4(8), 3278–3283 (2006)

M.T. Hsu, Y.C. Chang, Y.Z. Huang, Design of low power UWB LNA based on common source topology with current-reused technique. Microelectron. J. 44(12), 1223–1230 (2013)

A. Jha, J. Zheng, C. Masse, P. Hurwitz and S. Chaudhry, A 5.4GHz 0.65dB NF 6dBm IIP3 MGTR LNA in 130nm SOI CMOS, in IEEE 20th Topical Meeting on Silicon Monolithic Integrated Circuits in RF Systems (2021), pp. 19–21.

J. Jung, K. Chung, T. Yun, J. Choi, H. Kim, Ultra-Wideband low noise amplifier using a cascode feedback topology. IEEE Microw. Wireless Compon. Lett. 48(6), 1102–1104 (2006)

T.W. Kim, B. Kim, K. Lee, Highly linear receiver front-end adopting MOSFET transconductance linearization by multiple gated transistors. IEEE J. Solid-State Circuits 39(1), 223–229 (2004)

Y.M. Kim, H. Han, T.W. Kim, A 06-V +4 dBm IIP3 LC folded cascode CMOS LNA with gm linearization. IEEE Trans. Circuits Syst. II: Expr. Briefs 60(3), 122–126 (2013)

Y.J. Lin, S.S.H. Hsu, J.D. Jin, C.Y. Chan, A 3.1–106 GHz Ultra-Wideband CMOS low noise amplifier with current-reused technique. IEEE Microw Wireless Compon. Lett. 17(3), 232–234 (2007)

B. Razavi, RF microelectronics. Prentice hall, 2012.

Z.S. M. Salim, M. Muhamad, H. Hussin and N. Ahmad, CMOS LNA Linearization Employing Multiple Gated Transistors. in IEEE 13th International Conference on Telecommunication Systems, Services, and Applications (2019), pp. 137–140.

Q. Wan, C. Wang, Design of 3.1–10.6GHz ultra-wideband CMOS low noise amplifier with current reuse technique. AEU – Int. J. Electron. Commun. 65(12), 1006–1011 (2011)

X. Wang, A. Dinh, D. Teng, A 3–10 GHz ultra wideband receiver LNA in 0.13 μm CMOS. Circuits Syst. Signal Process. 33(6), 1669–1687 (2014)

T.P. Wang, Design and analysis of simultaneous wideband input/output matching technique for ultra-wideband amplifier. IEEE Access 9, 46800–46809 (2021)

K. Yousef, H. Jia, R. Pokharel, A. Allam, M. Ragab, K. Yoshida, A 2–16 GHz CMOS current reuse cascaded ultra-wideband low noise amplifier, in, 2011. Saudi Int. Electron. Commun. Photonics Conf. 2011, 1–5 (2021)

Acknowledgements

This work was supported in part by the Ministry of Science and Technology of Taiwan, R.O.C., under Grant MOST 111-2221-E-507-003. National Applied Research Laboratories Taiwan semiconductor research institute (TSRI) for its technical support and measurement. Taiwan.

Funding

Ministry of Science and Technology, Taiwan, MOST 111-2221-E-507-003, Jun-Da Chen

Author information

Authors and Affiliations

Corresponding author

Ethics declarations

Conflict of interest

The authors have no conflicts of interest, financial or otherwise. All authors declare that: (i) they have not received any support, financial or otherwise, from any organization that may be interested in the submitted work; (ii) have no other relationship or activity that might affect the submitted work.

Data Availability Statement

All data generated or analyzed during this study are included in this published article.

Additional information

Publisher's Note

Springer Nature remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

Rights and permissions

Springer Nature or its licensor (e.g. a society or other partner) holds exclusive rights to this article under a publishing agreement with the author(s) or other rightsholder(s); author self-archiving of the accepted manuscript version of this article is solely governed by the terms of such publishing agreement and applicable law.

About this article

Cite this article

Chen, JD., Chen, ZX. A 2.8–10-GHz CMOS Current Reuse Cascaded Linearity Improving Ultra-Wideband Low-Noise Amplifier. Circuits Syst Signal Process 42, 5091–5107 (2023). https://doi.org/10.1007/s00034-023-02355-w

Received:

Revised:

Accepted:

Published:

Issue Date:

DOI: https://doi.org/10.1007/s00034-023-02355-w