### International Journal of Emerging Technology and Advanced Engineering Website: www.ijetae.com (E-ISSN 2250-2459, Scopus Indexed, ISO 9001:2008 Certified Journal, Volume 11, Issue 11, November 2021)

Manuscript Received: 02 October 2021, Received in Revised form: 04 November 2021, Accepted: 10 November 2021 DOI: 10.46338/ijetae1121\_19

# Digital System Design for Traffic Light Controller System: A Systematic Approach

To-Nhi Ho. T<sup>1,3\*</sup>, Giao N. Pham<sup>2\*</sup>, Quang-Hung Nguyen<sup>1,3</sup>, Binh A. Nguyen<sup>4</sup>, Ngoc T. Le<sup>4</sup>, and Hoanh-Su Le<sup>1,3\*\*</sup>

<sup>1</sup>University. of Economics and Law, Ho Chi Minh City, Vietnam <sup>2</sup>Dept. of Computing Fundamentals, <sup>4</sup>ICT Department, FPT University, Hanoi, Vietnam <sup>3</sup>Vietnam National University, Ho Chi Minh City, Vietnam

\*Co-first author, \*\*Corresponding author

*Abstract*—In this paper, we are going to present the finite state machine, how to implement it via hardware description language (HDL), and how to use it in a real application. At first, the specification and requirements of traffic light controller are stated. Then, the system architecture based on finite state machine (FSM) are conducted. Finally, the way of using HDL as well as the test-bench simulation are given in detail.

*Keywords--* Digital system design, System on chip, Finite State Machine, Digital Design Education, Smart Classroom.

#### I. INTRODUCTION

Nowadays, everyone believes that excessive use of modern technologies such as computers, smartphones, cars, telecommunication systems, cloud computing, is affecting the human living [1]. And the technological equipment is changing day by day thanks to the contribution of scientist and engineers on their effort on digital system designs [2].

Finite state machine or finite state automation, or simply state machine, is a mathematical model of computation, an abstract machine that can be in exactly one of a finite number of states at any given time. In digital circuit, an FSM could be implemented by using programmable logic devices, a programmable logic controller, logic gates and flip flops or relays [3]. Thanks for the contribution of hardware description languages such as Verilog HDL, VHDL, we can make the synthesizable programs like software coding to make the digital circuits. As the consequence, the roads to real application or system are shorter [4]. In addition, the education of digital application design is more convenient with the simulation and implementation test-bed in the smart classroom environment [5-6].

In this paper, by considering the application of FSM (in section II) on traffic light controller, we will steps by steps (in section III) give the problem statements, algorithms designs, Hardware description language implementation, and test-bench simulation.

#### II. FINITE STATE MACHINE FUNDAMENTALS

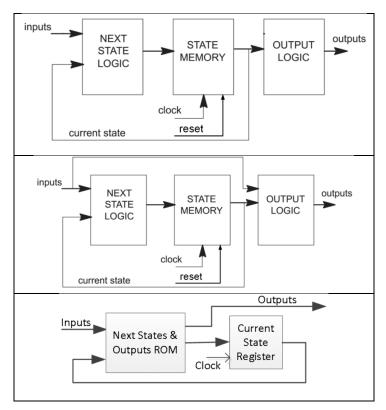

Figure I. Famous Architectures Of FSM System

#### International Journal of Emerging Technology and Advanced Engineering Website: www.ijetae.com (E-ISSN 2250-2459, Scopus Indexed, ISO 9001:2008 Certified Journal, Volume 11, Issue 11, November 2021)

Finite State Machine (FSM) is a basic but very important digital model, which is popularly used in digital designs due to its advantages on system debug, easy operational tracking. FIGURE 1 shows two FSM architectures: FSM Moore and FSM Mealy, the first part is for Moore and the second & third parts are for Mealy. The differences between Mealy and Moore models are the output values are determined both by its current state and the current inputs.

#### III. DIGITAL SYSTEM DESIGN FOR TRAFFIC LIGHT CONTROLLER SYSTEM

A. Problem statement

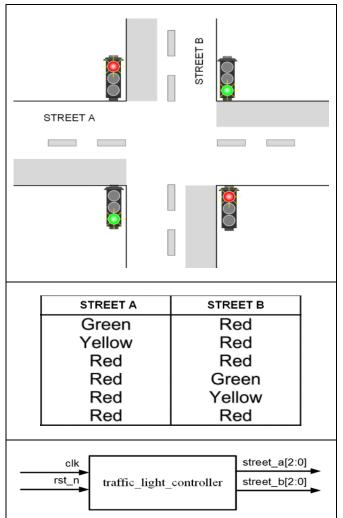

Figure III. Requirements For Traffic Light System

We will consider the traffic light in a crossroad where the considered system includes two traffic lights for street A and street B. Each light has three types of light signals: RED, YELLOW, and GREEN. The light state is summarized as the table in FIGURE II. In addition, the overall design of proposed traffic light controller is also given in FIGURE II where *clk* is the main clock system assumed 1Hz frequency; *rst\_n* is the reset signal to initialize our system; *street\_a* and *street\_b* are the output signals for light control.

B. FSM modules analysis

Website: www.ijetae.com (E-ISSN 2250-2459, Scopus Indexed, ISO 9001:2008 Certified Journal, Volume 11, Issue 11, November 2021)

| State  | street_a[2:0] | street_b[2:0] | fsm_g | fsm_y | fsm_r | ] |

|--------|---------------|---------------|-------|-------|-------|---|

| AG_BR  | 100           | 001           | 1     | 0     | 0     | 1 |

| AY_BR  | 010           | 001           | 0     | 1     | 0     |   |

| AR_BR1 | 001           | 001           | 0     | 0     | 1     |   |

| AR_BG  | 001           | 100           | 1     | 0     | 0     |   |

| AR_BY  | 001           | 010           | 0     | 1     | 0     |   |

| AR_BR2 | 001           | 001           | 0     | 0     | 1     |   |

|        |               |               |       |       |       | - |

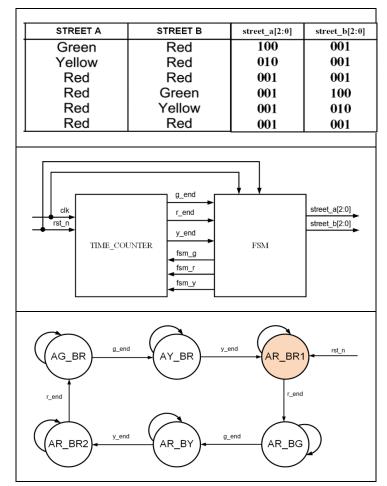

#### Figure IV. Expected output signals with corresponding light states

Based on the requirement analysis in section A, the expected outputs of proposed controller for *street\_a* and *street\_b* are given in the table of FIGURE III. And we divide the controller into two smaller units: TIME\_COUNTER and FSM.

TIME\_COUNTER is for timing, which count the predefined clocks such as 29 clocks for GREEN\_TIME, 4 clocks for YELLOW\_TIME, and 2 clocks for RED\_TIME. FSM shows the transition between finite states, we will have six states: AG\_BR (*street\_a* is red and *street\_b* is red), AY\_BR (*street\_a* is yellow and *street\_b* is red), and so on. The transitions between those states, and the condition of transitions are also given, and a note for an assumption is that the reset state is AR\_BR1 (both lights are red).

#### C. System implementations via HDL

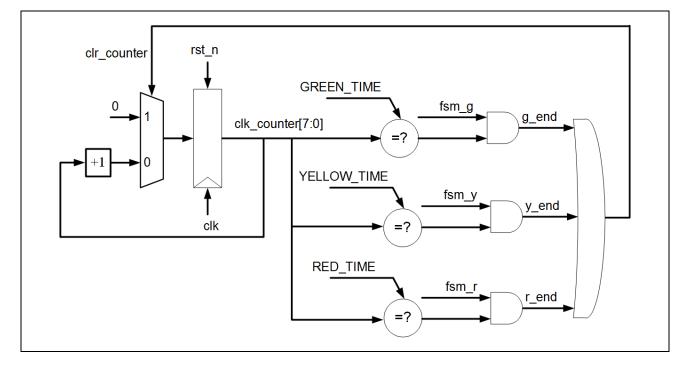

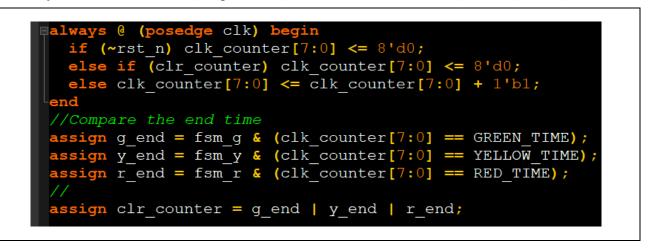

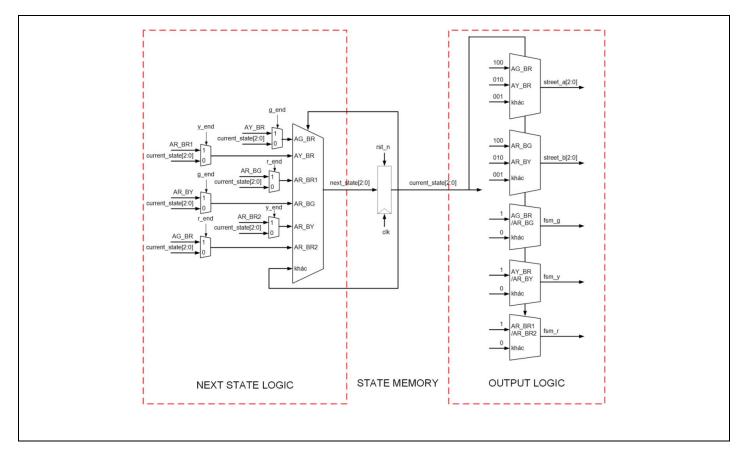

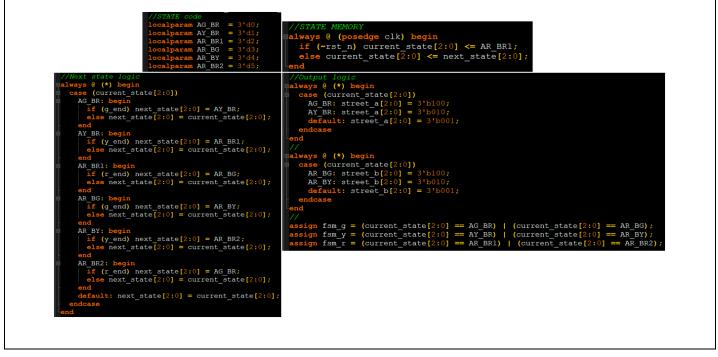

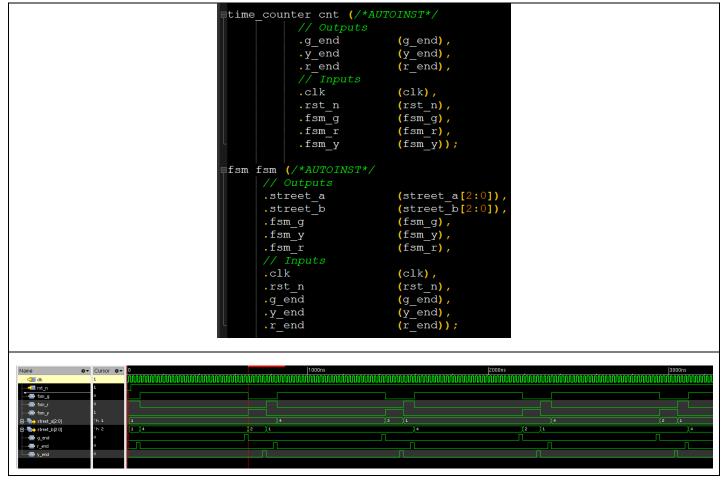

Our system will be implemented based on Verilog hardware description language for synthesizable and the design is tested in FPGA board. The whole designs include TIME\_COUNTER unit (as FIGURE IV), FSM unit (as FIGURE V), TOP system module, and a test-bench simulation as FIGURE VI.

International Journal of Emerging Technology and Advanced Engineering Website: www.ijetae.com (E-ISSN 2250-2459, Scopus Indexed, ISO 9001:2008 Certified Journal, Volume 11, Issue 11, November 2021)

Figure IV: Implementation of time\_counter unit using Verilog hardware description language.

Website: www.ijetae.com (E-ISSN 2250-2459, Scopus Indexed, ISO 9001:2008 Certified Journal, Volume 11, Issue 11, November 2021)

Figure V: Implementation Of Finite-State-Machine Unit Using Verilog Hardware Description Language.

Website: www.ijetae.com (E-ISSN 2250-2459, Scopus Indexed, ISO 9001:2008 Certified Journal, Volume 11, Issue 11, November 2021)

Figure VI: Top Simulation Of Traffic Light Controller Using Verilog Hardware Description Language.

#### IV. CONCLUSION

In this paper, the fundamental concepts of finite state machine have been introduced. In addition, we have analyzed an outstanding project named traffic light controller steps by steps from requirement collections, digital system design, RTL coding, Test-Bench simulation. We believe that in digital design education, it is convenient and for simulation and implement test-bench for students to practice in a smart classroom or a laboratory. We also hope that digital design engineer will have a good reference for their job. In the future, will implement this application in a smart classroom environment to help students experiment digital design, smart transportation simulation projects. All the source codes are open and will be shared as requirement.

#### Acknowledgement

This research is funded by Vietnam National University Ho Chi Minh City (VNU-HCM) under grant number: C2020-34-01.

#### Website: www.ijetae.com (E-ISSN 2250-2459, Scopus Indexed, ISO 9001:2008 Certified Journal, Volume 11, Issue 11, November 2021)

#### REFERENCES

- [1] Nguyen, D. M. et. al. "New constructions of quantum stabilizer codes based on difference sets". Symmetry 10 (11), 655, 2018.

- [2] Nguyen, D. M. et. al. "A novel construction for quantum stabilizer codes based on binary formalism". International Journal of Modern Physics B 34 (8), 2050059, 2020.

- [3] Giao, N. P. et. al. "Palm rejection algorithms on touch screen communication system". World Journal of Advanced Engineering Technology and Sciences 2021, 02(02), 052-057

- [4] Giao, N. P. et. al. "Implementation of Differential Sensing Scheme to Remove Panel Noise in Touchscreen Controller". International Journal of Emerging Technology and Advanced Engineering, 2021, 11(10), 104-108

- [5] Cebrian, Gisela, Ramon Palau, and Jordi Mogas. "The smart classroom as a means to the development of ESD methodologies". Sustainability 12.7, 2020.

- [6] Zhang, Mingbao, and Xiang Li. "Design of Smart Classroom System Based on Internet of Things Technology and Smart Classroom". Mobile Information System, 2021.