# NANOSTENCIL FABRICATION WITH DOUBLE EXPOSURE OPTICAL LITHOGRAPHY FOR SCALABLE RESIST-FREE PATTERNING OF METAL ON POLYMERS

Joseph S. Katz<sup>1</sup>, Woosung Park<sup>2</sup>, Michael T. Barako<sup>3</sup>, Aditya Sood<sup>4</sup>, Mehdi Asheghi<sup>2</sup>, and Kenneth E. Goodson<sup>2\*</sup> <sup>1</sup>Department of Electrical Engineering, Stanford University, Stanford, California, USA <sup>2</sup>Department of Mechanical Engineering, Stanford University, Stanford, California, USA <sup>3</sup>NG Next Basic Research laboratory, Northrop Grumman Corporation, Redondo Beach, CA <sup>4</sup>Department of Materials Science and Engineering, Stanford University, Stanford, California, USA

# ABSTRACT

Engineers require scalable processes for patterning nanoscale features on sensitive substrates to enable widespread manufacturability of advanced nanoelectronics. Nanostencils have shown promise, but prior work has relied on electron-beam (e-beam) and focused ion beam (FIB) processes. Nanostencils also frequently exhibit significant edge roughness. Here, we present a fabrication process for nanostencils using double exposure optical lithography and a novel capillary-driven lamination technique to reduce edge blurring, demonstrating sub-diffraction limit features of ~200nm on poly(methyl methacrylate) films. We demonstrate the utility of these stencils by generating metal patterns for use with the  $3\omega$  thermal conductivity measurement technique. We find a thermal conductivity of 0.24 Wm<sup>-1</sup>K<sup>-1</sup> and an anisotropy ratio of 9.7. This work demonstrates that nanostencils can be used for scalable, resist-free patterning of nanoscale features on sensitive substrates.

# **INTRODUCTION**

Traditional photolithography and patterning often requires exposure to caustic chemicals, high temperatures, and/or plasmas, which can damage non-traditional materials for heterogeneous integration applications, such as gate dielectrics [1], organic materials [2] (e.g. BEOL processes [3]), and 2D materials [4]. In particular, organic materials are commonly used in electronics packaging but are often thermally limiting, leading the research community to seek polymers with increased thermal conductivity. The 3 $\omega$  method, a common thermal characterization technique, is well suited for studying polymers because it can be used on thin films and can distinguish between thermal conduction in multiple directions [5-6]. Although useful, the 3 $\omega$  method has been difficult to implement with polymers due to the requirement of metal patterning and the incompatibility of many polymers with standard microfabrication techniques.

Nanostencils have shown promise as a method of decoupling damaging fabrication processes from sensitive materials by evaporating metals and other materials through nanoscale apertures in contact with the surface [7-8]. Stencils with sub-micron features are generally fabricated using FIB or e-beam lithography, which are slow and costly, so it is valuable to improve manufacturability.

Another key issue for nanostencils is that the gap between the substrate and membrane causes edge blurring. Ingle used a magnetic shadow mask and a magnet to pull the mask closer to the substrate to reduce the size of the penumbra [9]. Sidler *et al.* reported that compliant membranes showed reduced penumbra due to the ability of the membrane to follow the surface topography, including non-ideal roughness [10].

Here, we describe a scalable fabrication platform for nanostencil devices using double exposure optical lithography. We employ a novel capillary-driven lamination technique to bring the membranes into intimate contact with the substrates.

We have used these stencils to fabricate platinum features as

small as 200 nm on poly(methyl methacrylate) (PMMA) films without e-beam or FIB patterning, offering the first demonstration of manufacturing sub-diffraction limit stencils with double exposure optical lithography. We have also used the stencils to fabricate test structures for  $3\omega$  thermal conductivity measurements. Our measurements of a 170nm thin spin-cast PMMA sample show a through-plane thermal conductivity of 0.24 Wm<sup>-1</sup>K<sup>-1</sup>, and nearly an order of magnitude anisotropy. The strong anisotropy, favoring inplane thermal conduction, is due to the alignment of polymer chains during viscous shearing while spin coating. Kurabayashi et al. observed this phenomenon in spin-cast polyimide films [11]. This work extends prior work by Kurabayashi et al. by reporting a higher anisotropy ratio in a thinner film. Due to the high anisotropy ratio, heaters nearly an order of magnitude wider than the film thickness demonstrate significant sensitivity to anisotropy.

# FABRICATION

### **Stencil Fabrication**

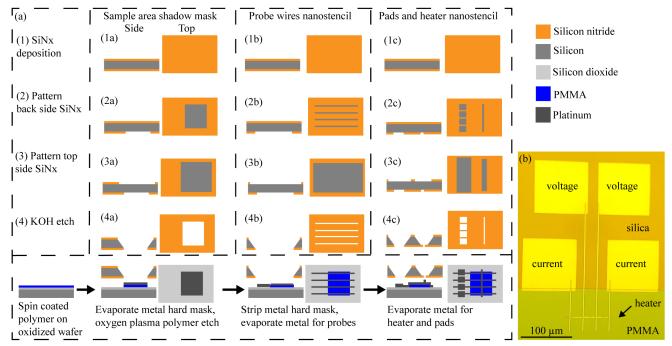

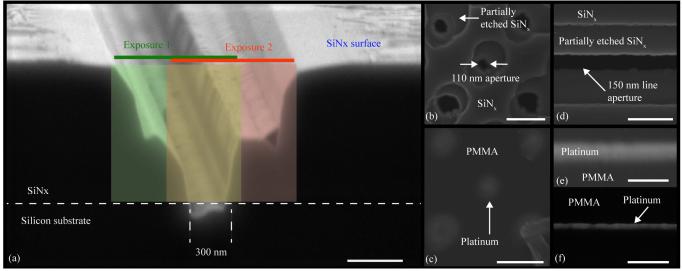

The process for fabricating the nanostencils is shown in fig. 1, from top to bottom. First, silicon wafers are coated with 500 nm low stress LPCVD silicon nitride and annealed at 1100°C for three hours to further reduce film stress. Next, the back side is coated with 0.7  $\mu$ m SPR-955 photoresist, exposed in an ASML PAS5500 stepper, and developed with MF-26A developer. The nitride is partially etched in CF<sub>4</sub> plasma using a PlasmaTherm Versaline LL ICP etcher. The resist is then stripped, and the lithography process repeated with a shift in the exposed features depending on the desired final aperture size. The exposed nitride is etched such that only the part of the film that was etched both times is completely removed. Fig. 2a shows a cross sectional SEM of a trench patterned with this double exposure technique. The top-side nitride is similarly patterned with contact lithography and no double exposure due to the coarse features.

The silicon is etched from the top side using KOH, and the membranes are left suspended with patterned apertures. In some cases, a thin nitride layer remains at the bottom of the features if the etch did not penetrate deep enough into the narrow gaps. In these cases, another  $CF_4$  etching step is done after the KOH etch, with the membranes facing a carrier wafer, to fully open the apertures.

### **Stencil-Based Device Fabrication**

The process for fabricating  $3\omega$  thermal conductivity measurement devices is shown in fig. 1, from left to right along the bottom. PMMA is spin coated from an anisole solution onto an oxidized silicon substrate and baked to remove the solvent.

The first stencil layer is used to pattern the polymer film such that there are areas for contact pads to be placed directly on the oxidized silicon substrate; this is done because metal pads for electrical contact are damaged by probes scratching through them when the pads are on a soft polymer film. To protect the desired sample area, an aluminum hard mask layer is deposited through the

978-1-940470-03-0/HH2018/\$25©2018TRF DOI 10.31438/trf.hh2018.80 280

Solid-State Sensors, Actuators and Microsystems Workshop Hilton Head Island, South Carolina, June 3-7, 2018

Figure 1: (a) process flow to produce stencils (top to bottom, three separate columns for three different stencil patterns) and corresponding  $3\omega$  devices (bottom left to bottom right), (b) completed  $3\omega$  device.

first stencil. Next, the polymer not protected by aluminum is etched using oxygen plasma. The aluminum is then stripped, leaving a patterned PMMA film.

The second stencil, which consists of lines going from the sample polymer area to the bare oxidized silicon area for pads, is attached to the substrate. The wafer is held over a beaker of boiling water for a few seconds so that a thin layer of condensate forms on the substrate and membranes. The wafer is then blow dried with compressed air, and the capillary forces from the drying process draws the membrane into intimate contact with the substrate. Next, platinum, with a titanium adhesion layer, is evaporated through the second stencil to form probe lines bridging from the bare, oxidized silicon substrate up to the top of the PMMA film.

The third stencil layer follows an identical process to the second with different feature patterns. The third stencil is used to form the platinum line, to act as heater and thermometer for the  $3\omega$  measurement, and pads for electrical contact.

Examples of stencils and corresponding platinum features on PMMA are shown in fig. 2. The difference in edge blurring between fig. 2e and fig. 2f highlights the effectiveness of the capillary-driven lamination in reducing the significance of this phenomenon.

Figure 2: (a) cross section of etched SiNx film before being suspended, showing double exposure, (b) etched membrane with dot apertures and (c) corresponding platinum dots on PMMA, (d) etched membrane with line aperture and (e) corresponding platinum line on PMMA, (f) minimal edge blurring in platinum line on PMMA when using capillary-driven membrane lamination. All scale bars are 500nm.

# **Fabrication Repeatability**

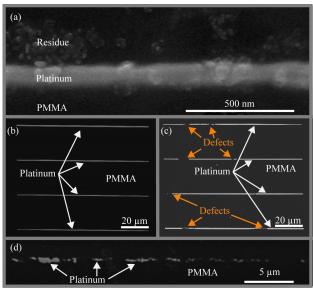

Processes involving multiple exposures and/or etching steps per layer directly on the primary substrate, have long been used in industry for devices with feature sizes well below the diffraction limit [12], and are very repeatable. In contrast, edge blurring is often severe in nanostencil lithography and detrimental in many applications, including in  $3\omega$  devices because the heater width affects the sensitivity to anisotropy and the heat source is typically assumed to be uniform with a precise boundary. Capillary-driven lamination, described above, substantially reduced the significance of edge blurring; however, there is still edge roughness and variation along the length of the line, as shown in fig. 3a. Edge roughness in the metal features may be due to edge roughness in the corresponding stencils, which is visible in fig. 2b & d. It is also possible that the evaporating water left residue at the edges of the features. Signs of residue are observed in fig. 3a.

In some cases, a combination of stencil defects, edge residue, and mechanical abrasion from lifting the stencils after deposition causes discontinuities in deposited lines, as highlighted by the differences between fig. 3b and fig. 3c. In the narrowest lines used for process debugging, ~200nm, there were often lines with many discontinuities, e.g. fig. 3d. The narrowest device used for a  $3\omega$ measurement in this paper was 1.4 µm, so the edge roughness of ~50nm is substantially smaller than the heater widths used for measurements reported here.

Figure 3: (a) SEM of platinum line with residue, (b) SEM of platinum lines on PMMA, (c) SEM of platinum lines with discontinuities on PMMA, (d) SEM of narrow platinum line with many discontinuities on PMMA.

# 30 THERMAL CONDUCTIVITY MEASUREMENT Experimental method

The  $3\omega$  method is a Joule heating technique that relies on the linear relationship between temperature and resistance of a single metal line acting as both a heater and a thermometer. A sinusoidal current is applied at a frequency,  $1\omega$ , which causes a power dissipation at frequency  $2\omega$ . Power dissipation causes temperature oscillations at the same frequency, which in turn causes resistance oscillations. The product of the  $1\omega$  current and  $2\omega$  resistance is a voltage at  $3\omega$ , which is a function of the temperature rise, and thus the thermal properties of the sample material. The details of the  $3\omega$  method have been described extensively in literature [9-10].

## **Sensitivity Analysis**

Sensitivity is defined as a fractional change in a measured parameter divided by the fractional perturbation in the sensed variable that caused the change. The through-plane and in-plane thermal conductivity sensitivities are, respectively,

$$S_{k_z} = \frac{\partial \Delta T}{\Delta T} / \frac{\partial k_z}{k_z} \tag{1a}$$

$$S_{k_x} = \frac{\partial \Delta T}{\Delta T} / \frac{\partial k_x}{k_x} \tag{1b}$$

$$S_w = \frac{\partial \Delta T}{\Delta T} / \frac{\partial w}{w} \tag{1c}$$

$$S_{TCR} = \frac{\partial \Delta T}{\Delta T} / \frac{\partial TCR}{TCR}$$

(1d)

where  $\Delta T$  is the measured temperature rise over ambient, k is the thermal conductivity in the direction indicated by the subscript, w is the heater width, and TCR is the temperature coefficient of resistance (S<sub>TCR</sub> is unity).

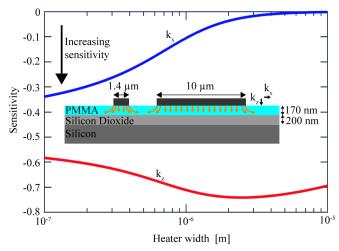

Wide heaters cause predominantly through-plane thermal conduction and are thus mainly sensitive to through-plane thermal conductivity. Narrower heaters cause substantial conduction both through and within the film, so they can be sensitive to in-plane conductivity. This phenomenon is illustrated in the inset of fig. 4.

To determine the sensitivities numerically, we use a model based on the harmonic line heater solution by Feldman [13]. A fractional perturbation,  $\partial k/k$ , of 0.01 is used for both  $k_x$  and  $k_z$  sensitivity calculations. Fig. 4 shows the sensitivity to through-plane and in-plane thermal conductivity versus heater width for the sample considered in this study, and nominal conductivity values of  $k_z = 0.24$  Wm<sup>-1</sup>K<sup>-1</sup> and  $k_x = 2.33$  Wm<sup>-1</sup>K<sup>-1</sup>, as measured. While narrower heaters would be more sensitive, the 1.4 µm heater width used in this study shows appreciable anisotropy sensitivity.

#### **Thermal Measurement Results**

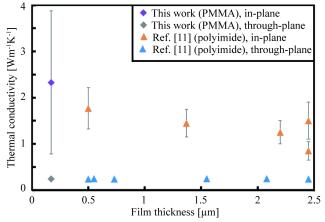

The spin cast PMMA demonstrates high thermal conductivity anisotropy, which is consistent with the expectation for a high degree of backbone alignment. The measured results are presented in fig. 5, alongside polyimide data from ref. [11].

Figure 4: Sensitivity versus heater width for both  $k_x$  (blue) and  $k_z$  (red). Inset: heater cross section schematic showing both in-plane and through-plane heat conduction for a narrow heater but primarily through-plane conduction for a wide heater.

The measured through-plane thermal conductivity is  $0.24 \pm 0.005 \text{ Wm}^{-1}\text{K}^{-1}$ , which is within the commonly accepted range of values for bulk PMMA thermal conductivity. The in-plane conductivity is  $2.33 \pm 1.55 \text{ Wm}^{-1}\text{K}^{-1}$ , corresponding to an anisotropy ratio of 9.7 from polymer backbone alignment. The heaters are oriented orthogonally to the radius of the wafer, so the measured thermal conductivities are the vertical and radial conductivities.

Uncertainty is calculated using a sum of squares approach:

$$\sigma_{k_z} = \frac{k_z}{S_{k_z}} \sqrt{(S_{TCR} \frac{\sigma_{TCR}}{TCR})^2 + (S_w \frac{\sigma_w}{w})^2}$$

(2)

Through-plane conductivity is an input for in-plane conductivity calculation, so in-plane uncertainty is

$$\sigma_{k_x} = \frac{k_x}{S_{k_x}} \sqrt{(S_{TCR} \frac{\sigma_{TCR}}{TCR})^2 + (S_w \frac{\sigma_w}{w})^2 + (S_{kz} \frac{\sigma_{k_z}}{k_z})^2}$$

(3)

We assume a 1% uncertainty in TCR and 50nm uncertainty in heater width. Anisotropy uncertainty can be lowered with narrower heaters, and with more heaters and multi-parameter fitting [14].

Figure 5: Measured in- and through-plane thermal conductivity.

# CONCLUSIONS

We have demonstrated that nanostencils can be fabricated using double exposure optical lithography as a scalable platform for resist-free patterning of nanoscale features on polymers and other sensitive substrates. We have deposited platinum features of ~200 nm on PMMA films. We have used the stencils to fabricate measurement structures for a  $3\omega$  thermal conductivity measurement of a 170nm spin-cast PMMA film, and report a thermal conductivity anisotropy ratio of 9.7, favoring in-plane conduction.

### ACKNOWLEDGEMENTS

J.S.K. thanks the Semiconductor Research Corporation (SRC) and the Intel Education Alliance for a Graduate Research Fellowship. This work was supported by the SRC through GRC task 2666. Work was performed in part in the nano@Stanford labs, which are supported by the National Science Foundation as part of the National Nanotechnology Coordinated Infrastructure under award ECCS-1542152. The authors are grateful to the process staff at the SNF and Prof. Yan Xia in the Department of Chemistry at Stanford for helpful discussions.

## REFERENCES

[1] C.J. Brennan, C.M. Neumann, and S.A. Vitale, "Comparison of Gate Dielectric Plasma Damage from Plasma-Enhanced Atomic Layer Deposited and Magnetron Sputtered TiN Metal Gates", Journal of Applied Physics, 118, 045307 (2015).

- [2] H.-K. Kim, D.-G. Kim, K.-S. Lee, M.-S. Huh, S. H. Jeong, K. I. Kim, and T.-Y. Seong, "Plasma Damage-Free Sputtering of Indium Tin Oxide Cathode Layers for Top-Emitting Organic Light-Emitting Diodes", Applied Physics Letters, 86, 183503 (2005).

- [3] R. Mahajan, R. Sankman, N. Patel, D.-W. Kim, K. Aygun, Z. Qian, Y. Mekonnen, I. Salama, S. Sharan, D. Iyengar, and D. Mallik, "Embedded Multi-Die Interconnect Bridge (EMIB) A High Density, High Bandwidth Packaging Interconnect", Proceedings of the 2016 IEEE 66<sup>th</sup> Electronic Components and Technology Conference (ECTC), Las Vegas, NV, 5/31-6/3/16, Institute of Electrical and Electronics Engineers, Piscataway (2016), pp. 557-565.

- [4] H.S. Song, S.L. Li, H. Miyazaki, S. Sato, K. Hayashi, A. Yamada, N. Yokoyama, and K. Tsukagoshi, "Origin of the Relatively Low Transport Mobility of Graphene Grown through Chemical Vapor Deposition", Scientific Reports, 2, 337 (2012).

- [5] D.G. Cahill, "Thermal Conductivity Measurement from 30 to 750K: the 3ω Method", Review of Scientific Instruments, 61, 802 (1990).

- [6] C. Dames, and G. Chen, "1ω, 2ω, and 3ω Methods for Measurement of Thermal Properties", Review of Scientific Instruments, 76, 124902 (2005).

- [7] J. Brugger, J.W. Berenschot, S. Kuiper, W. Nijdam, B. Otter, and M. Elwenspoek, "Resistless Patterning of Sub-Micron Structures by Evaporation through Nanostencils", Microelectronic Engineering, 53, 403, (2000).

- [8] O. Vazquez-Mena, L. Gross, S. Xie, L.G. Villanueva, and J. Brugger, "Resistless Nanofabrication by Stencil Lithography: A Review", Microelectronic Engineering, 132, 236 (2015).

- [9] F. W. Ingle, "A Shadow Mask for Sputtered Films", Review of Scientific Instruments, 45, 1460 (1974).

- [10] K. Sidler, L.G. Villanueva, O. Vazquez-Mena, V. Savu, and J. Brugger, "Compliant Membranes Improve Resolution in Full-Wafer Micro/Nanostencil Lithography", Nanoscale, 4, 773 (2012).

- [11] K. Kurabayashi, M. Asheghi, M. Touzelbaev, and K.E. Goodson, "Measurement of the Thermal Conductivity Anisotropy in Polyimide Films", IEEE Journal of Microelectromechanical Systems, 8, 2 (1999).

- [12] M. Maenhoudt, J. Versluijs, H. Struyf, J. Van Olmen, and M. Van Hove, "Double Patterning Scheme for Sub-0.25 k1 Single Damascene Structures and NA=0.75, λ=193nm", Proceedings of SPIE 5754 Optical Microlithography XVII, San Jose, CA, 5/12/04, Society of Photo-Optical Instrumentation Engineers, Bellingham (2004), pp. 1508-1518.

- [13] A. Feldman, "Algorithm for Solutions of the Thermal Diffusion Equation in a Stratified Medium with a Modulated Heating Source", High Temperatures High Pressures, 31, 293 (1999).

- [14] J.S. Katz, M.T. Barako, W. Park, A. Sood, M. Ashaeghi, K.E. Goodson, "Highly Anisotropic Thermal Conductivity in Spin-Cast Polystyrene Nano-Films", Proceedings of the 2018 17<sup>th</sup> IEEE Intersociety Conference on Thermal and Thermomechanical Phenomena in Electronic Systems (ITherm), San Diego, CA, 5/29-6/1/18, Institute of Electrical and Electronics Engineers, Piscataway (2018).

### CONTACT

\*K. E. Goodson, tel: +1-650-725-2086; goodson@stanford.edu