# Параметризуемый матричный умножитель двоичных чисел с фиксированной точкой в прямом и дополнительном коде

А.А. Беляев<sup>1,2</sup>, И.А. Беляев<sup>1</sup>, Я.Я. Петричкович<sup>1</sup> <sup>1</sup>АО НПЦ «ЭЛВИС», bel@elvees.com

<sup>2</sup>Национальный исследовательский университет «МИЭТ»

Аннотация — В статье описывается устройство матричного однотактного умножителя, особенностью которого является возможность вычисления произведения двух операндов в формате с фиксированной точкой, каждый из которых может быть представлен как в прямом, так и в дополнительном коде. Приводится сравнение с традиционной схемой матричного умножителя и результаты синтеза предлагаемого устройства по технологии 28 нм.

Ключевые слова — умножитель, сложнофункциональный блок, IP-блок, двоичная арифметика, прямой код, дополнительный код, цифровая обработка сигналов.

#### I. Введение

Одним из ключевых вычислительных элементов в составе современных высокопроизводительных систем цифровой обработки сигналов является умножитель [1,2].

Выполняемая с его помощью операция умножения, а также основанные на ней операции комплексного умножения и умножения с накоплением необходимы при вычислении преобразований Фурье, фильтров и произведений матриц, что, в свою очередь, является основой для реализации прикладных задач коммуникации, обработки изображений и видео, а также сверточных нейронных сетей. Таким образом, эффективная реализация операций умножения является основой для решения важнейших задач цифровой обработки сигналов.

В разнообразных задачах сигнальной обработки могут использоваться самые различные типы данных – как знаковые (signed), так и беззнаковые (unsigned). Например, пиксели исходного изображения, как правило, бывают представлены массивом беззнаковых 8-разрядных данных, а коэффициенты фильтров или преобразований, на которые они умножаются, могут быть как знаковыми, так и беззнаковыми, и разрядность их может варьироваться в широких пределах.

По этой причине крайне желательно, чтобы цифровые умножители могли работать с обеими разновидностями типов данных — как знаковыми, так и беззнаковыми, в противном случае использование специализированных умножителей под различные типы данных приведет к неоправданному росту аппаратных затрат.

Поставщикам IP-блоков приходится учитывать потребности разработчиков. В частности, мировой лидер по поставке цифровых IP-блоков компания Synopsys предлагает своим потребителям в составе библиотеки DesignWare [3] умножители, в которых выбор знакового либо беззнакового режима работы выбирается с помощью управляющего 1-разрядного входа TC (two's complement control, 0 = unsigned, 1 = signed).

Однако такой способ управления позволяет изменять тип данных лишь одновременно у обоих сомножителей (либо оба они знаковые, либо оба беззнаковые) и не дает возможность изменять тип входных операндов независимо друг от друга, хотя, как указывалось выше, необходимость вычисления произведения двух сомножителей, один из которых знаковый, а другой — беззнаковый, встречается в цифровой обработке сигналов довольно часто.

Проблему вычисления произведения разнотипных сомножителей можно решить также за счет увеличения разрядности сомножителей на 1 разряд, при этом оба сомножителя всегда рассматриваются как знаковые. Однако такой способ подразумевает увеличение аппаратных затрат и, кроме того, некоторое снижение быстродействия вследствие увеличения длины критической цепи.

Целью данной работы являлась разработка устройства для вычисления произведения двух операндов, представленных в форматах с фиксированной точкой (в том числе целых чисел), любой из которых, независимо от другого, может иметь знаковый либо беззнаковый тип. При этом требовалось обеспечить параметризуемость данного устройства по количеству разрядов каждого из входных операндов.

Раздел II посвящен выводу базовых алгебраических соотношений, лежащих в основе построения проектируемого устройства.

В разделе III описывается структура параметризуемого матричного умножителя, выполняющего умножение двух операндов в форматах с фиксированной точкой, каждый из которых может иметь знаковый либо беззнаковый тип.

В разделе IV приводятся результаты синтеза схемы предложенного умножителя для 8-разрядных

операндов и сравнение их с аналогичными результатами для традиционной схемы умножителя.

Раздел V содержит заключение и выводы по выполненной работе.

#### II. АЛГЕБРАИЧЕСКОЕ ОПИСАНИЕ РАБОТЫ ЗНАКОПЕРЕМЕННОГО УМНОЖИТЕЛЯ

Значение беззнакового целого числа  $A_u$ , представленного в прямом J-разрядном коде, может быть записано формулой:

$$A_u = \sum_{j=0}^{J-1} (2^j a_j),$$

где  $a_i - j$ -й разряд числа.

Значение знакового целого числа  $A_s$ , представленного в дополнительном J-разрядном коде, выражается формулой:

$$A_s = (-1)^{a_{J-1}} 2^{a_{J-1}} a_{J-1} + \sum_{j=0}^{J-2} (2^j a_j).$$

В общем случае значение знакового либо беззнакового числа *А* записывается формулой:

$$A = (-1)^{n_A} 2^{a_{J-1}} a_{J-1} + \sum_{i=0}^{J-2} (2^j a_i),$$

где  $n_A = tc_A \times a_{J-1}$  — знак числа A;  $tc_A$  — управляющий бит, указывающий на то, что число A записано в прямом ( $tc_A$  =0), либо дополнительном ( $tc_A$  =1) коде.

Таким образом, любое число в прямом или дополнительном коде может быть представлено в виде суммы двух слагаемых:

$$A = A_1 + A_2,$$

где первое слагаемое зависит от старшего разряда  $a_{J-1}$  и типа кодирования числа  $tc_A$ , а второе слагаемое зависит от младших J-1 разрядов и одинаково для обоих типов кодирования:

$$A_1 = (-1)^{n_A} 2^{a_{J-1}} a_{J-1},$$

$$A_2 = \sum_{j=0}^{J-2} (2^j a_j),$$

Аналогично и второй сомножитель B может быть представлен в виде суммы двух слагаемых:

$$B=B_1+B_2,$$

где:

$$B_1 = (-1)^{n_B} 2^{b_{K-1}} b_{K-1},$$

$$B_2 = \sum_{k=0}^{K-2} (2^k b_k),$$

$$b_k$$

– разряды числа  $B(k=0,1,...K-1)$ .

Тогда произведение этих двух сомножителей может быть записано в виде:

$$\begin{array}{l} AB = (A_1 + A_2)(B_1 + B_2) = A_1B_1 + A_2B_1 + \\ A_1B_2 + A_2B_2 = (-1)^{n_A + n_B}2^{a_{J-1} + b_{K-1}}a_{J-1}b_{K-1} + \\ (-1)^{n_A}2^{a_{J-1}}a_{J-1}\sum_{k=0}^{K-2}(2^kb_k) + \\ (-1)^{n_B}2^{b_{K-1}}b_{K-1}\sum_{j=0}^{J-2}(2^ja_j) + \\ \sum_{i=0}^{J-2}(2^ja_i)\sum_{k=0}^{K-2}(2^kb_k) \,. \end{array}$$

Последняя формула содержит знакопеременные слагаемые. Чтобы преобразовать их и избавиться от знака «минус», можно воспользоваться известным соотношением для дополнительного кода:

$$-A = -A + 1$$

,

где  $\sim A$  — побитовая инверсия числа A.

С учетом этого формула для вычисления произведения примет вид:

$$\begin{array}{l} AB = 2^{a_{J-1}+b_{K-1}}(a_{J-1}b_{K-1}^{} n_A^{} n_B) + \\ \sum_{k=0}^{K-2}(2^{k+a_{J-1}}a_{J-1}b_k^{} n_A) + 2^{a_{J-1}} + \\ \sum_{j=0}^{J-2}(2^{j+b_{K-1}}a_jb_{K-1}^{} n_B) + 2^{b_{K-1}} + \\ \sum_{j=0}^{J-2}(2^ja_j) \sum_{k=0}^{K-2}(2^kb_k) \,. \end{array}$$

Последнее слагаемое в полученной формуле полностью совпадает с результатом вычисления беззнакового парциального произведения чисел A и B, без учета старших разрядов обоих чисел, другие три слагаемых зависят от знаков чисел и типа представления.

### III. СХЕМОТЕХНИЧЕСКАЯ РЕАЛИЗАЦИЯ МАТРИЧНОГО ЗНАКОПЕРЕМЕННОГО УМНОЖИТЕЛЯ

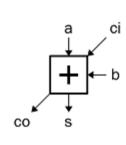

Базовым элементом для построения схемы матричного умножителя является полный одноразрядный сумматор, обозначение и таблица истинности для которого приведены на рис. 1.

| а | b | ci | S | СО |

|---|---|----|---|----|

| 0 | 0 | 0  | 0 | 0  |

| 0 | 0 | 1  | 1 | 0  |

| 0 | 1 | 0  | 1 | 0  |

| 0 | 1 | 1  | 0 | 1  |

| 1 | 0 | 0  | 1 | 0  |

| 1 | 0 | 1  | 0 | 1  |

| 1 | 1 | 0  | 0 | 1  |

| 1 | 1 | 1  | 1 | 1  |

Рис. 1. Обозначение и таблица истинности полного одноразрядного сумматора

Полный одноразрядный сумматор имеет три входа — для двух слагаемых и входа переноса, и два выхода — для выхода суммы и выхода переноса.

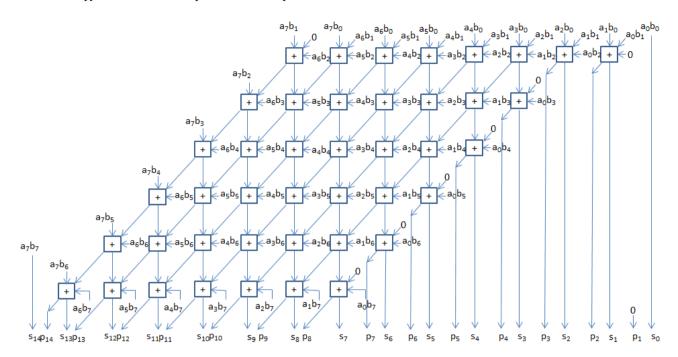

Пример традиционной схемы матричного умножителя для вычисления произведения двух беззнаковых 8-разрядных операндов с выводом результата в двухрядном коде приведен на рисунке 2.

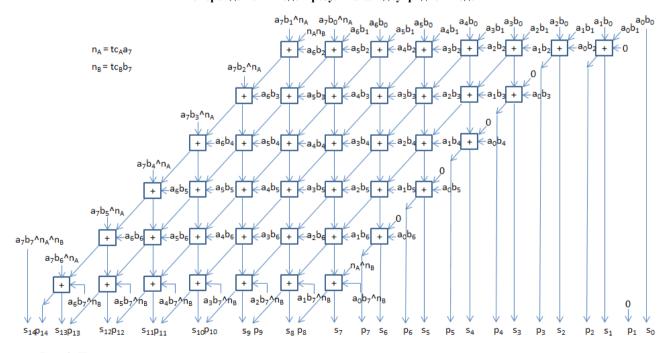

На рисунке 3 представлена схема предлагаемого матричного умножителя для вычисления произведения двух знаковых/беззнаковых 8-разрядных операндов с выводом результата в двухрядном коде. Хотя в приведенном примере операнды имеют одинаковую разрядность, представленная схема легко обобщается (параметризуется) для случая произвольной разрядности каждого из операндов. Заметим, что сама

структура матрицы одноразрядных сумматоров практически одинакова для обеих схем умножителей, расширение функциональности во втором случае достигается лишь за счет небольшого усложнения логических функций для некоторых входов матрицы.

Применение двухрядного кода для вывода результата в обоих случаях дает возможность минимизировать задержку в тех случаях, когда требуется вычислять сумму нескольких произведений.

Рис. 1. Традиционная схема матричного умножителя для вычисления произведения двух беззнаковых 8-разрядных операндов с выводом результата в двухрядном коде

Рис. 3. Предлагаемая схема матричного знакопеременного умножителя для вычисления произведения двух знаковых/беззнаковых 8-разрядных операндов с выводом результата в двухрядном коде

Отметим также, что в данной работе для ясности изложения внимание намеренно сфокусировано лишь на матричных структурах умножителей и при этом не рассматриваются такие известные способы ускорения

работы умножителей [4], как, например, дерево Уоллеса, алгоритм Бута и др. Эти и другие техники ускорения работы умножителей в равной степени могут

быть применены и к предлагаемой схеме знакопеременного умножителя.

#### IV. РЕЗУЛЬТАТЫ СИНТЕЗА

В таблице 1 приведены результаты синтеза предлагаемого знакопеременного умножителя по технологии 28 нм для различных разрядностей входных операндов.

В этой же таблице для сравнения представлены данные синтеза для альтернативного варианта реализации знакопеременного умножителя на основе известных схем знаковых умножителей за счет увеличения разрядности на 1 разряд.

Таблица 1 Сравнительные результаты синтеза по технологии 28 нм двух типов умножителей

|                          | Площадь (при максимальном быстродействии), мкм <sup>2</sup> |                            | Площадь (минимальная), мкм <sup>2</sup> |                            | Максимальное быстродействие,<br>нс |                            |

|--------------------------|-------------------------------------------------------------|----------------------------|-----------------------------------------|----------------------------|------------------------------------|----------------------------|

| Разрядность<br>операндов | Предлагаемый<br>умножитель                                  | Традиционный<br>умножитель | Предлагаемый<br>умножитель              | Традиционный<br>умножитель | Предлагаемый<br>умножитель         | Традиционный<br>умножитель |

| 4                        | 270                                                         | 408                        | 54                                      | 71                         | 0.175                              | 0.210                      |

| 6                        | 432                                                         | 611                        | 110                                     | 138                        | 0.263                              | 0.314                      |

| 8                        | 685                                                         | 939                        | 190                                     | 229                        | 0.384                              | 0.418                      |

| 12                       | 1332                                                        | 2101                       | 436                                     | 511                        | 0.603                              | 0.639                      |

| 16                       | 2138                                                        | 3824                       | 808                                     | 939                        | 0.830                              | 0.843                      |

#### V. ЗАКЛЮЧЕНИЕ

В работе представлен способ построения матричного знакопеременного умножителя для вычисления произведения двух операндов с параметризуемой разрядностью, представленных в форматах с фиксированной точкой (в том числе целых чисел), любой из которых, независимо от другого, может иметь знаковый либо беззнаковый тип.

Основными достоинствами предлагаемого умножителя являются:

- универсальность: любой из множителей может быть представлен как в прямом, так и в дополнительном коде;

- параметризуемость: умножитель может быть имплементирован для множителей с любым количеством разрядов каждого из операндов;

- сокращение площади по сравнению использованием традиционных схем умножителей;

- вывод результата в двухрядном коде, что позволяет использовать частичные произведения дальше без задержки переноса.

#### ЛИТЕРАТУРА

- [1] Угрюмов Е.П. Цифровая схемотехника: Учеб. пособие /- 3-е изд. СПб. : БХВ-Петербург, 2010. 816 с.

- [2] Уэйкерли Д.Ф. Проектирование цифровых устройств: Пер. с англ. Т.1 / Д. Ф. Уэйкерли. М.: Постмаркет, 2002.

- [3] https://www.synopsys.com/designware-ip/technical-bulletin/designware-libraries.html (дата обращения: 27.08.2021).

- [4] Кормен Т., Лейзерсон Ч., Ривест Р., Алгоритмы: построение и анализ / Пер. с англ. под ред. А. Шеня. М.: МЦНМО, 2000. 960 с. ISBN 5-900916-37-5.

## Parameterizable Matrix Multiplier of Fixed-Point Binary Numbers in Direct and Complementary code

A.A. Belyaev<sup>1,2</sup>, I.A. Belyaev<sup>1</sup>, Y.Y. Petrichkovich<sup>1</sup>

<sup>1</sup>Joint Stock Company Research and Development Center «ELVEES»

<sup>2</sup>National Research University «MIET»

Abstract — One of the most important computational operation in digital signal processing is multiplication. It is an underlying operation in telecommunication, photo and video processing, convolution neural networks, etc. The article describes the design of a matrix multiplier, the feature of which is the ability to calculate the product of two operands in a fixed-point format, each of which can be represented both in direct and in complementary code. A comparison with the traditional matrix multiplier scheme and the results of the synthesis of the proposed device using the 28 nm technology are presented.

Keywords — multiplier, IP core, binary arithmetic, direct code, complementary code, digital signal processing.

#### REFERENCES

- [1] Ugrjumov E.P. Cifrovaja shemotehnika Digital circuitry, 3<sup>rd</sup> ed., SPb., BHV-Peterburg, 2010, 816 p. (In Russian)

- [2] John F. Wakerly. Digital Design: Principles and Practices, 4th Edition, 2006.

- [3] https://www.synopsys.com/designware-ip/technical-bulletin/designware-libraries.html (дата обращения: 27.08.2021).

- [4] Thomas H. Cormen, Charles E. Leiserson, Ronald L. Rivest, and Clifford Stein. Introduction to Algorithms, Third Edition MIT Press, 2009.