Abstract

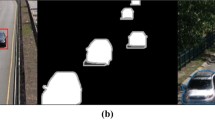

In this paper, a high speed, reliable, low memory demanding and precise object detection and tracking algorithm is proposed. The proposed work uses a macroblock of rectangular shape, which is placed in the very first frame of the video to detect and track a single moving object using monocular camera. The macroblocks are positioned in the field of view (FOV) of camera where the probability of occurrence of object is high. After placing macroblocks, a threshold value is examined to detect the presence of objects in the selected macroblocks. Afterwards, a quadtree approach is used to minimize the bounding box and to reduce the pixelation. A tracking algorithm is proposed which illustrates a unique method to find the moving directional vectors. The proposed method is based on macroblock resizing, which demonstrates an accuracy rate of 98.5% with low memory utilization.

Similar content being viewed by others

References

A. L. Bovic, Image and Video Processing (Acad. Press, New York, 2000).

M. Tekalp, Digital Video Processing (PrenticeHall, Englewood Cliffs, NJ, 1995).

Y. Amit, 2D Object Detection and Recognition (MIT Press, Cambridge, MA, 2002).

R. F. Gonzalez and R. E. Wood, Digital Image Processing (Pearson Education, Singapore, 2001).

O. Javed, and M. Shah, “Object tracking: a survey,” ACM Comput. Surv. 38 (4), 1–45 (2006).

S. Zhang, C. Wang, S. C. Chan, X. Wei, and C. H. Ho, “New object detection, tracking, and recognition approaches for video surveillance over camera network,” IEEE Sensors J. 15 (5), 2679–2691 (2015).

M. M. Azab, H. A. Shedeed, and A. S. Hussein, “New technique for online object tracking-by-detection in video,” IET Image Processing 8 (12), 794–803 (2014).

R. K. Behera, P. Kharade, S. Yerva, P. Dhane, A. Jain, and K. Kutty, “Multi-camera based surveillance system,” in Proc. World Congress on Information and Communication Technologies (WICT) (Trivandrum, 2012), pp. 102–108.

X. Lei and A. Fu, “2D maximum-entropy thresholding image segmentation method based on second-order oscillating PSO,” in Proc. 5th Int. Conf. on Natural Computation (Tianjin, 2009), pp. 161–165.

S. Kumar, M. Pant, and A.K. Ray, “2D maximum entropy method for image thresholding converge with differential evolution,” Adv. Mech. Eng. Its Appl. 2 (3), 289–292 (2012).

Jiwoon Jeon and R. Manmatha, “Using maximum entropy for automatic image annotation,” Image Video Retrieval 3115, 24–32 (2004).

C. Stauffer and W. E. L. Grimson, “Learning patterns of activity using real-time tracking,” IEEE Trans. Pattern Anal. Mach. Intellig. 22 (8), 747–757 (2000).

G. Han, X. Li, N. Sun, and J. Liu, “A robust object detection algorithm based on background difference and LK optical flow,” in Proc. 11th Int. Conf. on Fuzzy Systems and Knowledge Discovery (FSKD) (Xiamen, 2014), pp. 554–559.

W. Wang, R. Nevatia, and B. Yang, “Beyond pedestrians: a hybrid approach of tracking multiple articulating humans,” in Proc. IEEE Winter Conf. on Applications of Computer Vision (Waikoloa, HI, 2015), pp. 132–139.

V. Reddy, C. Sanderson, and B. C. Lovell, “Improved foreground detection via block-based classifier cascade with probabilistic decision integration,” IEEE Trans. Circuits Syst. Video Technol. 23 (1), 83–93 (2013).

E. López-Rubio and R. M. Luque-Baena, “Stochastic approximation for background modelling,” Comput. Vision Image Understand. 115 (6), 735–749 (2011).

Z. Zivkovic and F. van der Heijden, “Efficient adaptive density estimation per image pixel for the task of background subtraction,” Pattern Recogn. Lett. 27 (7), 773–780 (2006).

Shuai Zhang, Chong Wang, Shing-Chow Chan, Xiguang Wei, and Check-Hei Ho, “New object detection, tracking, and recognition approaches for video surveillance over camera network,” IEEE Sensors J. 15 (5), 2679–2691 (2015).

Shuai Zhang, S. C. Chan, Bin Liao, and K. M. Tsui, “A new visual object tracking algorithm using Bayesian Kalman filter,” IEEE Sensors J. 15 (5) (2015).

Shang-Lin Wu, Chien-Yu Lu, Ming-Hsien Tu, Huan-Shun Huang, Kuen-Di Lee, Yung-Shin Kao, and Ching-Te Chuang, “A 0.35 V, 375 kHz, 5.43 μW, 40 nm, 128 kb, symmetrical 9T subthreshold SRAM with tri-state bit-line,” Microelectron. J. 51, 89–98 (2016).

Junchao Chen, Kwen-Siong Chong, and Bah-Hwee Gwee, “Ultra-low power read-decoupled SRAMs with ultra-low write-bitline voltage swing,” Springer Circuits, Syst. Signal Processing (CSSP) 33 (10), 3317–3329 (2015).

C. B. Kushwah, S. K. Vishvakarma and D. Dwivedi, “Single-ended boost-less (SE-BL) 7T process tolerant SRAM cell design in sub-threshold regime for ultralow power applications,” Springer Circuits, Syst. Signal Processing (CSSP) 35 (2), 385–407 (2016).

M. Moghaddam, S. Timarchi, M. H. Moaiyeri, and M. Eshghi, “An ultra-low-power 9T SRAM cell based on threshold voltage techniques,” Springer Circuits, Syst. Signal Processing (CSSP) 35 (5), 1437–1455 (2016).

B. H. Calhoun and A. Chandrakasan, “A 256 kb subthreshold SRAM in 65nm CMOS,” in Proc. IEEE Int. Solid State Circuits Conf. (San Francisco, CA, 2006), pp. 2592–2601.

N. Verma and A. P. Chandrakasan, “A 256 kb 65 nm 8T subthreshold SRAM employing sense-amplifier redundancy,” IEEE J. Solid-State Circuits 43 (1), 141–149 (2008).

Ya-Chun Lai and Shi-Yu Huang, “A resilient and power-efficient automatic-power-down sense amplifier for SRAM design,” IEEE Trans. Circuits Syst. II: Express Briefs 55 (10), 1031–1035 (2008).

Do Anh-Tuan, Kong Zhi-Hui, and Yeo Kiat-Seng, “Hybrid-mode SRAM sense amplifiers: New approach on transistor sizing,” IEEE Trans. Circuits Syst. II: Express Briefs 55 (10), 986–990 (2008).

Z. Bo, S. Hanson, D. Blaauw, and D. Sylvester, “A variation-tolerant sub-200 mV 6-T subthreshold SRAM,” IEEE J. Solid-State Circuits 43 (10), 2338–2348 (2008).

B. H. Calhoun and A. P. Chandrakasan, “A 256-kb 65-nm sub-threshold SRAM design for ultra-low-voltage operation,” IEEE J. Solid-State Circuits 42 (3), 680–688 (2007).

S. W. Sun and P. G. Y. Tsui, “Limitations of CMOS supply-voltage scaling by MOSFET threshold-voltage variation,” IEEE J. Solid-State Circuits 30 (8), 947–949 (1995).

T. H. Kim, J. Liu, and C. H. Kim, “An 8T subthreshold SRAM cell utilizing reverse short channel effect for write margin and read performance improvement,” in Proc. Custom Integrated Circuits Conf. CICC’07 (San Jose, Sept. 16–19, 2007), pp. 241–244.

K. Zhang, U. Bhattacharya, Z. Chen, F. Hamzaoglu, D. Murray, N. Vallepalli, Y. Yang, B. Zheng, and M. Bohr, “A SRAM design on 65nm CMOS technology with integrated leakage scheme,” in Proc. Symp. on Digest of Technical Papers on VLSI Circuits (Honolulu, June 17–19, 2004), pp. 294–295.

J. Chen, L. Clark, and T.-H. Chen, “An ultra-low-power memory with a subthreshold power supply voltage,” IEEE J. Solid-State Circuits 41 (10), 2344–2353 (2006).

Author information

Authors and Affiliations

Corresponding author

Additional information

The article is published in the original.

Pooran Singh born in 1986 and is a PhD scholar in Discipline of Electrical Engineering department (VLSI Design) at IIT Indore. He is working with Dr. Santosh Kumar Vishvakarma at Nanoscale Devices, VLSI Circuit and System Design R and D Lab in research topic “Ultra low power, high-stability feedback controlled SRAM cell for FPGA and SRAM.” He received degree in Masters in Technology from ABV-IIITM, Gwalior in 2010. He was awarded with the prestigious Fulbright-Nehru Doctoral Research Fellowship 2014–2015, a very highly competitive fellowship award to carry on his research in USA for the period of nine months. He has worked with School of Electrical and Computer Engineering (ECE), Georgia Institute of Technology, Atlanta, USA under Fulbright-Nehru Fellowship.

Santosh K. Vishvakarma born in 1979 and received M.Tech. degree in Microelectronics from Punjab University, Chandigarh, India in 2003, and Ph.D. degree from Indian Institute of Technology, Roorkee, Uttrakhand, India in 2010. From January 2009 to July 2010, he was with University Graduate Center, Kjeller, Norway, as a Postdoctoral Fellow with Prof. T. A. Fjeldly under European Union Project “COMON” on compact modelling development and parameter extraction of multi-gate MOSFETs. He is currently with the School of Engineering, Indian Institute of Technology, Indore as Assistant Professor, where he is leading Nanoscale Devices, VLSI Circuit and System Design Lab. His current research includes Nanoscale devices and circuits, ultralow-power digital and analog circuit design and their technology, FPGA based design, power reduction techniques in FPGA based system design, multi-gate and multi-fin MOSFET, and tunnel FET and their circuit applications in memories. Recently, he started working for high speed transceiver design and graphene based digital Standard Cell Design. He is also keen interested and started work on Internet of Things (IoT) for healthcare and defence applications.

Rights and permissions

About this article

Cite this article

Singh, P., Vishvakarma, S.K. Low complexity-low power object tracking using dynamic quadtree pixelation and macroblock resizing. Pattern Recognit. Image Anal. 27, 731–739 (2017). https://doi.org/10.1134/S1054661817040150

Received:

Published:

Issue Date:

DOI: https://doi.org/10.1134/S1054661817040150