Abstract

The effect of TiO2 interfacial morphology on perovskite crystallinity was investigated by modifying the micro and nanoscale surface roughness of compact TiO2. While surface treatments of the compact TiO2 layer are recognized as effective strategies to enhance the photovoltaic performance of perovskite solar cells, the discussion regarding the crystallinity of perovskite atop TiO2 has been limited. In this study, we explored the impact of micro and nano scale interface morphology on perovskite crystal formation and its subsequent effects on device performance. Surprisingly, despite the absence of noticeable voids at the interface between the compact TiO2 and perovskite layers, the perovskite crystal morphology exhibited significant improvement following either micro or nanoscale interfacial modification. This enhancement ultimately led to improved photoconversion efficiency and reduced I–V hysteresis. These results emphasize the importance of underlayer surface morphology in the perovskite crystallization and suggest that the presence of grain boundaries within the perovskite layer may also contribute to I–V hysteresis in perovskite solar cells.

Similar content being viewed by others

Introduction

Organometal halide perovskite solar cell (PSC) has been attracting great attention due to its remarkable optoelectronic properties1,2,3,4,5 available with a cost-effective fabrication process. PSC has achieved a drastic improvement in a photoconversion efficiency (PCE) since it was first reported in 20096, that PCE now reaches over 25%, which is comparable to that of conventional crystalline silicon photovoltaics7,8,9,10. Among the evolution of PSCs, a significant number of highly efficient PSC devices adopt a structure wherein a perovskite layer is deposited on an electron transport layer, and titanium oxide (TiO2) serves as the frequently utilized electron transport layer11,12,13. However, it has been reported that an interface between TiO2 and perovskite layers shows a mismatch in the junction since there is a large difference in a lattice constant between TiO2 and that of the perovskite crystal14. They also reported that I–V hysteresis, the phenomenon which PCE value differs depending on the scan direction, is attributed to the electrostatic capacitance component resulting from the mismatch between these interfaces15,16 although it is worth noting that there are other proposed origins of I–V hysteresis, including ionic migration of perovskite17,18 or the ferroelectric characteristics of perovskite19,20. At the same time, several studies have reported enhancements in both PCE and the mitigation of I–V hysteresis through interfacial modifications at the TiO2 and perovskite interface21,22,23,24. In these studies, they suggested that the surface treatment resulted in an improvement of a wettability of the TiO2 surface and/or an adjustment of the valence band position of TiO2, which thus led to an enhancement of the photo carriers generated in the perovskite layer transfer to the TiO2 layer.

While many scientists have examined the efficacy of surface modification at TiO2 and perovskite interface, there has been limited discussions concerning the influence of surface treatments on the deposited perovskite crystals in previous studies. However, the influence of underlayer surface roughness has been a subject of interest across various research fields related to thin film fabrication. In the context of organic thin film transistors, it has been observed that increased surface roughness in the gate dielectric leads to a higher density of grain boundaries, resulting in an increased presence of trap states in the semiconductor layer25,26. In the field of heteroepitaxy, where a crystal or thin film is grown on a substrate with a different lattice constant, it is well-documented that the quality of deposited crystals can change significantly depending on the condition of the underlayer crystal interface, potentially leading to the formation of dislocations or defects27,28. Although perovskite films in PSCs differ from these materials, as they are primarily fabricated using spin-coating techniques and are generally polycrystalline, it is conceivable that modifications at the interface between the TiO2 and perovskite layers could affect not only the junction state but also the crystallinity of the grown perovskite layer.

In this report, we examined the effect of enhancing the contact of TiO2 and perovskite interface on the perovskite crystallinity and subsequently evaluated the solar cell device performance. First, we focused on micro-scale roughness and attempted to improve the interfacial contact between TiO2 and perovskite layers by introducing a FTO substrate with a smoother surface morphology than the commonly used FTO substrate. Secondly, we attempted to eliminate gaps at the nanometer level by depositing a mesoporous layer of TiO2 nanoparticles that serve as scaffolds for perovskite layers on top of a dense layer of TiO2 and further improved the TiO2 and perovskite contact. In order to clarify the effect of underlayer morphology, we adopted the the simplest perovskite composition (methyl ammonium lead iodide) and the device structure without any doping or passivation to exclude any possible factors that may affect the results. Surprisingly, the morphology of the perovskite films exhibited a remarkable improvement by the surface modifications that the grain boundaries observed at the perovskite layer reduced significantly. Our study demonstrated that the surface modification of a perovskite underlayer gives a drastic impact on not only to the interfacial contact but also the perovskite morphology.

Results and discussion

The modification of micro scale roughness on the c-TiO2/perovskite interface

We first focused on a micro scale surface roughness of TiO2 and perovskite interface, which some studies have identified the presence of voids or gaps at the interface as a major issue that leads to a poor PCE and stability of the devices14,21. In this study, we adopted a FTO substrate with a smooth surface morphology as a means of improving the interfacial contact of TiO2 and perovskite layers. FTO substrate is a common material used as a transparent conductive oxide electrode in PSC devices though its surface typically exhibits a rough surface morphology with a scale of 0.5–1.0 μm that can exacerbate the physical gap in the interface. On the other hand, FTO substrate used in this study has a flatter surface morphology than that of the generally used FTO substrate, that the standard surface roughness parameters, arithmetical mean height (Sa) and root mean square height (Sq), calculated as 0.012 μm and 0.015 μm, which is both smaller than half of the values of conventional FTO (Supplementary Fig. S1, Supplementary Table S1). Thus, an introduction of the flatter FTO substrate is expected to improve the planarity of the interface, thereby reducing the likelihood of voids generates.

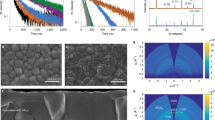

PSC device with a planer hetero junction structure was fabricated on the FTO substrate with a different surface morphology and its effect on a perovskite crystal deposited above was examined. For brevity, FTO substrate generally used in PSC devices is denoted as “Rough FTO” and FTO substrate with a flatter surface morphology is denoted as “Flat FTO” respectively. Figure 1a shows cross-sectional scanning electron microscopy (SEM) images of PSC devices prepared with the FTO substrates having a different surface roughness. Further SEM images showing a wider range of the devices are shown in Supplementary Fig. S2. According to the SEM observations, few difference was observed in a film thickness of deposited layers depending on their FTO surface textures. The compact TiO2, perovskite (CH3NH3PbI3, MAPbI3), Spiro-OMeTAD and Au back contact layer had an average thickness of 50 nm, 600 nm, 180 nm, and 80 nm respectively. Moreover, by focusing on the interface between the compact TiO2 dense layer and the perovskite layer, neither of the device had any noticeable gaps or voids at the TiO2 and perovskite interface, which had been proposed as a major concern by the previous studies14,21. This enhancement of the contact between TiO2 and perovskite interface may be associated with the utilization of a fast crystallization deposition, a perovskite fabrication process that drips the antisolvent during the spin coating process29. Application of the antisolvent dripping, followed by an immediate annealing, can expedite the crystallization of perovskite crystals. This accelerated crystallization process may result in the creation of tiny nano-sized crystals, effectively preventing the formation of a noticeable gap between the dense TiO2 and perovskite layers.

(a) Cross section SEM images of PSC devices with Rough FTO (left) and Flat FTO (right). A compact TiO2 layer is denoted as c-TiO2. (b) Schematic illustration of a possible grain growth of perovskite layer fabricated with Rough and Flat FTO substrate. Red arrows indicate growth direction of perovskite grains.

However, when focused on the perovskite layer itself on the other hand, there was a significant difference appeared at the perovkite microstrucuture depending on the surface morphology of the FTO substrate. The perovskite layer that was fabricated with the Rough FTO substrate exhibited grain boundaries toward different directions throughout the film with a grain size of 300–500 nm. Furthermore, since the compact TiO2 layer was deposited along with the rough surface morphology of the FTO substrate, it appears that the TiO2 layer, with a maximum thickness of 50 nm, is significantly influenced by the surface morphology of the Rough FTO. Consequently, crystal growth direction of the perovskite layer was also likely to be affected by the morphology. On the other hand, the compact TiO2 layer deposited on the Flat FTO had a flatter and more uniform surface in response to the morphology of the FTO substrate. Surprisingly, the perovskite layer fabricated with the Flat FTO substrate had significantly fewer grain boundaries, which predominantly oriented vertically, compared to the perovskite layer on the Rough FTO substrate. This observation clearly demonstrates the inneglisible influence of the microstructure of TiO2 interface on the subsequent perovksite film quality.

As previously mentioned in the introduction, researchers in the field of film fabrication have extensively explored the impact of substrate morphology on the properties of deposited films. Recent findings have highlighted notable differences in the microstructural characteristics and mechanical properties of chemically vapor-deposited Ti(C,N) coatings, despite them being produced through the same process with the only variation being the substrate's surface roughness, coarse and fine textured morphology30. As schematically shown in Fig. 1b, our observations will align with these reports, indicating that a rough substrate surface, particularly with the presence of macroscopic steps and edges, promotes the growth of grains that maintain the rough surface morphology. These grains undergo competitive interactions with neighboring grains during lateral growth. When grains originate on the steps of a rough substrate, their lateral expansion is restricted by adjacent grain growth, leading to the formation of grain boundaries. In contrast, when perovskite is deposited onto a flat surface, as exemplified by the Flat FTO, it tends to exhibit uniform growth along the smooth underlayer. These perovskite grains prefer vertical growth towards the substrate surface, resulting in fewer grain boundaries and a more predominant vertical orientation.

Surface morphology of the perovskite films deposited on the underlayer with a different surface morphology was also examined by the top view SEM observation shown in Supplementary Fig. S3. Both perovskite films were uniformly covered with a grain size of around 100–500 nm without any notable pinholes regardless of the surface morphology of FTO substrates. This is also comfirmed by the surface roughness measurement summarized in Supplementary Fig. S4. Although it was previously observed that the bare Rough and Flat substrates exhibited distinct differences in surface roughness as illustrated in Supplementary Fig. S1 and Supplementary Table S1, both perovskite films exhibited nearly identical surface roughness characteristics. Perovskite films fabricated on Rough FTO and Flat FTO had their surface roughness parameters calculated as 0.012 and 0.011 μm for Sa and 0.015 μm for Sq, respectively and both films had a negative Kurtosis value indicating the platykutic surface. Even though the perovskite film on Rough FTO displayed coarse grains with numerous grain boundaries in the cross-sectional observation, it appears that the perovskite surface is just as smooth as that on Flat FTO, which is notably smoother than the original bare FTO substrate.

Further evaluation of each perovskite films by X-ray diffraction (XRD) measurement was operated shown in Supplementary Fig. S5. The diffraction patterns confirmed that both perovskite films have a crystal structure of an unoriented tetragonal MAPbI3 that is well consistent with the diffraction pattern shown by the previous report31. Despite the basic composition and crystal structure did not exhibit any noticeable differences, their perovskite film quality seems to vary significantly depending on their underlayer’s morphology.

The substantial improvement derived by the surface modification was also examined by the current–voltage (I–V) measurement of the solar cell devices. I–V curves and each photovoltaic parameters of PSC devices fabricated with Rough and Flat FTO substrates are shown in Fig. 2 and Table 1. For the evaluation of I–V hysteresis, the hysteresis factors32, defined by Eq. (1) below for the perovskite solar cells was calculated.

(a) I–V curves of PSC devices fabricated with Rough FTO and Flat FTO. Dashed lines and solid lines indicate forward scan (scan from 0.0 to 1.2 V) and reverse scan (scan from 1.2 to 0.0 V), respectively. (b) Box plots of photovoltaic parameters for 8 samples for each. A blank box correspond to the forward scan and filled box to the reverse scan.

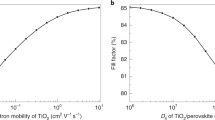

Despite both samples have the same device structure and material compositions, the introduction of Flat FTO in PSC devices also showed a clear enhancement of the photovoltaic performances. The device with Flat FTO exhibited an increase in Voc and fill factor (FF), which resulted in an improvement of overall PCE. JSC on the other hand, did not show a clear difference, or slightly smaller value was observed with Flat FTO which is also confirmed with the EQE measurement (Supplementary Fig. S6). This is in a good agreement with the XRD result that both perovskite films have the same composition corresponds to MAPbI3. Moreover, despite the mismatch between compact TiO2 and perovskite layer, that had been previously demonstrated as a potential cause of I–V hysteresis, was not observed in our devices, I–V hysteresis behavior also showed a difference by their FTO surface morphology.

Improvement of the device performance was further evaluated by introducing the space-charge limited current (SCLC) measurement. Electron only device was fabricated for both Rough and Flat FTO substrate with the configuration of FTO (Rough or Flat)/c-TiO2/perovskite/C60/Au and characterized for different biases. Figure 3 shows the dark J–V curves of the electron only devices fabricated with Rough and Flat FTO. In the low biased range, there is a linear relationship between current and voltage, characterized as the Ohmic region followed by the trap-limited SCLC region appears in the intermediate bias range. Trap density levels experience a continuous occupation, with all traps becoming filled until reaching the trap-filled limit voltage (VTFL) as bias is increased. Then, there is a surge in the current indicating the trap occupation. The trap-free SCLC region is then observable at high bias range. The onset voltage (VTFL) exhibits a linear correlation with the density of trap states33,34,35; thus, we employed VTFL values to evaluate a trap density among the perovskite films resulting from the interface modifications. While dark J–V curves for full stack solar cell device did not show a distinct difference (Supplementary Fig. S7), VTFL was characterized as 1.45 V for Rough FTO and 0.96 V for Flat FTO, indicating the reduced trap in perovskite layer by Flat FTO. This result may be induced by the perovskite layer with diminished horizontal grain boundaries previously shown in Fig. 1a, which will facilitate a carrier transportation and eventually led to the better device performance. Indeed, grain boundaries existing in the crystal have been reported to hinder a carrier transport or cause an undesired recombination of carriers, which can eventually lower the photovoltaic performance. These undesirable characteristics have been reported not only for perovskite solar cells but also for multi crystalline silicon solar cells36,37. deQuilettes and co-workers examined the effect of microstructure on carrier dynamics in perovskite thin films according to the photoluminescence spectroscopy38. They reported that grain boundaries showed lower photoluminescence and exhibited a faster nonradiative decay compared with those of bulk perovskite crystals. There is also a report that a device with potassium doped perovskite could diminish the grain boundary of perovskite layer and achieved a hysteresis free photovoltaic performance39,40. Their results are consistent with our suggestion that carrier recombination and/or internal resistance were successfully prevented by the elimination of grain boundaries, which may eventually lead to the improvement of solar cell performances. Our results also indicate that presence of grain boundaries in the perovskite crystal may also be a crucial factor that causes I–V hysteresis in PSC devices.

The modification of nano scale roughness on the c-TiO2/perovskite interface

Secondly, based on the abovementioned results we further discuss the effect of TiO2 and perovskite interfacial contact on the deposited perovskite crystal by modifying a nano meter scale surface roughness. Application of nano structure and its influence on the subsequent film property has been reported by inorganic planer heterojunction solar cells using TiO2 nanoparticles41. Herein, we fabricated a nanoparticle TiO2 layer on top of the compact TiO2 dense layer to create a mesoscopic structured PSC device, which has been reported to have a higher efficiency than the device with the planar heterojunction structure. Using two types of FTO substrates, Rough FTO and Flat FTO, a compact TiO2 dense layer was deposited followed by a TiO2 mesoporous layer. The deposition of the perovskite layer, the hole transport layer, and the gold electrode was carried out in the same manner as the process for the planer hetero junction structure.

Cross sectional SEM images of PSC devices fabricated with and without mesoporous TiO2 layer are shown in Fig. 4 (SEM images showing a wider range of the mesoscopic structure device are also shown in Supplementary Fig. S2). Both devices had almost the same film thickness for the compact TiO2, perovskite, Spiro-OMeTAD and Au electrode with a thickness of 50 nm, 600 nm, 180 nm, and 80 nm respectively. For the mesoscopic structure device, mesoporous TiO2 layer was introduced on top of the compact TiO2 layer with an average thickness of 100 nm. As with the result shown in Fig. 1a, while the perovskite layer fabricated with the planer hetero junction structure exhibited the notable grain boundaries toward various directions, the perovskite film fabricated on the mesoporous TiO2 layer appeared with the much smoother surface as well as the much less grain boundaries that their horizontal direction almost disappeared. While the device with Rough FTO presented a considerable development by the application of mesoporous TiO2, the device with Flat FTO did not show such a notable difference in presence of mesoporous TiO2 layer. However, as the Supplementary Fig. S8 shows, grain boundaries were effectively diminished, and the perovskite morphology improved slightly compared with the planer hetero junction device.

(a) Cross section SEM images of PSC devices with planer hetero junction (left) and mesoscopic structure (right). The caption of c-TiO2 indicates a compact TiO2 layer and m-TiO2 for the mesoporous TiO2 layer. (b) Schematic illustration of a possible grain growth of perovskite layer fabricated with and without mesoporous TiO2 layer. Red arrows indicate growth direction of perovskite grains.

As schematicaly shown in Fig. 4b, introduction of a nano structure with mesoporous TiO2 layer effectively fill the gap produced from the rough surface morphology of the FTO substrates. This will enable a nano scale mechanical interlocking, which significantly reinforces the interface with the increased surface area and the total contact42,43. Therefore, the growth direction of the perovskite crystal was controlled, resulting in a dense film with significantly diminished grain boundaries. It has been pointed out that among the papers achieving the highly efficient PSC devices, mesoscopic structure account for a large part of the reports and thus the investigations for the reason why mesoscopic structure affords superior performance may be a key for the further improvement of PSCs11. While effective electron extraction facilitated by a large area contact as well as the energy level alignment between the perovskite and TiO2 layer have been proposed as potential benefits of mesoscopic structures, our findings also suggest an additional role of nano scale interface modification in regulating perovskite crystal growth, resulting in the formation of higher quality films with fewer grain boundaries.

According to the top view SEM observation shown in Supplementary Fig. S3, the perovskite film was uniformly covered with a grain size around 100–500 nm and there was no apparent difference in the perovskite morphology compared with other perovskite films. However, surface roughness measurement resulted in the increased value of Sa and Sq compared to that of the perovskite fabricated on Rough and Flat FTO without TiO2 nano particle (Supplementary Fig. S4). As the film showed a positive kurtosis value as well as the increased positive skewness value, there is a tendancy of an acute peaks at the perovskite surface, possibly due to the TiO2 nano particle. XRD measurement confirmed that the perovskite film fabricated on mesoporous TiO2 layer is a tetragonal MAPbI3 without any preferential orientations, which is identical to the result obtained in Rough and Flat FTO without TiO2 nano particle (Supplementary Fig. S5).

Solar cell performance of the planer hetero junction and mesoscopic structured devices are summarized in Fig. 5 and Table 2. The device fabricated with Rough FTO, which showed I–V hysteresis in planer hetero junction structure previously shown in Fig. 2, achieved a significant enhancement by the introduction of the mesoporous TiO2 layer, that all Jsc, Voc and FF improved and PCE showed more than 1.5 times larger value than that of the planer structured devices (Fig. 5b). In addition, while the device with planer hetero junction structure showed a large hysteresis in I–V measurement, hysteresis factor decreased as half of the planer hetero junction structure’s value in mesoscopic structure devices. On the other hand, the device with Flat FTO which showed the improvement of PCE and I–V hysteresis with the planer hetero junction structure did not show a notable improvement in I–V hysteresis, although the photovoltaic parameters and overall PCE improved by introducing a mesoporous TiO2 layer (Supplementary Fig. S9). However, Rough FTO obtained a higher Jsc than that of the Flat FTO, as shown in Supplementary Table S2. This trend was also observed for the device in planer hetero junction structure as shown in Table 1. This may be due to the flat surface morphology that Flat FTO has, which reflects incident light and causes loss of absorbed light, while Rough FTO has a rough surface morphology that causes the reabsorption of reflected light and thus possible to absorb light more than the Flat FTO.

(a) I–V curves of PSC devices fabricated with planer (only c-TiO2) and mesoscopic (c-TiO2 and m-TiO2) structure. Dashed lines and solid lines indicate forward scan (scan from 0.0 to 1.2 V) and reverse scan (scan from 1.2 to 0.0 V), respectively. (b) Box plots of photovoltaic parameters for 8 samples each. A blank box correspond to the forward scan and filled box to the reverse scan.

Enhancement of the device performance in mesoscopic structured device was also evaluated by SCLC measurement shown as Fig. 6. Electron only device was fabricated with the configuration of Rough FTO/c-TiO2/m-TiO2/perovskite/C60/Au. Dark J–V curves of the electron only devices fabricated with and without TiO2 nano particle were measured under the different bias, as same as the measurement shown in Fig. 3. Introduction of the TiO2 nano particle resulted in the decrease of trap in perovskite layer that the measured VTFL was 0.82 V for the mesoscopic structured device while planer structured device was 1.46 V. This is lower than that of the previously shown Flat FTO results in Fig. 3, which is also in a good agreement with the better device performance of mesoscopic structured device than the planer structured device with Flat FTO. As confirmed by SEM observations, mesoscopic structure devices with both Rough and Flat FTO exhibited the improvement in perovskite morphology indicating the further efficacy of the surface treatment of TiO2 layer on perovskite crystallization. In addition to the enhancement in the perovskite crystallinity, an increase in the coverage area of the perovskite layer by TiO2 nanoparticles will lead to an efficient electron injection, which will be associated with the increased Jsc observed in the mesoscopic structured samples, and EQE shown in Supplementary Fig. S6. At the same time, since it is deposited with a thickness of around 100 nm, the TiO2 nanoparticles eliminated the gaps between TiO2 and perovskite layer within a nano meter scale, and therefore seems to obscure the impact of macro scale surface modification derived by the Flat FTO.

In summary, we examined the effect of improving the interfacial contact of TiO2 and perovskite on the crystallinity of the fabricated perovskite layer as well as the subsequent photovoltaic characteristics of the solar cell devices. First, we introduced a FTO substrate with a smoother surface morphology as a method to eliminate the micro scale voids between TiO2 and perovskite layers. Then a mesoporous TiO2 layer was introduced for the further nano scale modification of TiO2 and perovskite contact. SEM observation revealed a substantial enhancement not only in the interface between the TiO2 and perovskite layers but also in the overall perovskite morphology upon the incorporation of the Flat FTO substrate. Along with exploring the impact of surface treatment on the perovskite crystallinity, we also confirmed the improvement of PSC device photovoltaic characteristics as well as the I–V hysteresis. The observed enhancement is also confirmed by inducing the mesoporous TiO2 layer that the presence of grain boundaries across the entire film resulted in a noticeable decrease with a conventional Rough FTO substrate associated with the notable improvement of I–V hysteresis and photovoltaic characteristics. As the photovoltaic performance including I–V hysteresis changed in response to the perovskite morphology, the presence of grain boundaries inside perovskite layers is also likely to be responsible for the cause of I–V hysteresis. Our results clearly emphasize the importance of underlying surface morphology on the resulting perovskite film quality, which will contribute to the further development of the perovskite crystallization process in future.

Methods

Materials

All chemicals were stored in a drying room with a dew point temperature of – 30 °C and employed without having any purification. As for the transparent conductive layer, fluorine doped tin oxide (FTO) substrates were purchased from Nippon Sheet Glass Co. Ltd (NSG) and SPD laboratory Inc (SPD). They are mentioned as “Rough FTO” for the one from NSG and “Flat FTO” for the one from SPD respectively. Both FTO substrates showed an average sheet resistance of 10 Ω/□ and 80% transmittance in visible range while an average film thickness was 800 nm for Rough FTO and 1000 nm for Flat FTO. The chemicals to prepare perovskite layer, PbI2 (99.99%) is obtained from Kojundo Chemical Laboratory Co., LTD and MAI from Tokyo Chemical Industry (TCI). Titanium diisopropoxide bis (acetylacetonate) (75 wt% in isopropanol), lithium bis (trifluoro methanesulfonyl) imide (LiTFSI) and 4-tert-butylpyridine (tBP) are purchased from Sigma-Aldrich. TiO2 paste with a size of 24 nm nano particle was purchased from JGC C&C. Spiro-OMeTAD ((2,20,7,70-tetrakis-(N,N-di-4-methoxyphenylamino)-9,90-spirobifluorene)) is bought from Merck. All the solvents are obtained from Wako Pure Chemical Industries, LTD.

Device fabrication

The basic device structure of fabricated PSC is FTO/compact TiO2/perovskite (MAPbI3)/Spiro-OMeTAD/Au. For the device with mesoscopic structure, mesoporous TiO2 was fabricated on the compact TiO2 layer before the perovskite layer fabrication. All samples were fabricated on same date in the same batch. As for the transparent conductive layer, FTO glasses are cleaned by a sonication in acetone and ethanol for 10 min respectively. A compact TiO2 layer was deposited on the cleaned FTO glass substrates by spray pyrolysis deposition with the solution of 300 µL titanium diisopropoxide bis (acetylacetonate), dispersed in 4.00 mL of ethanol. Then they were annealed at 430 °C for 15 min. For the device with the mesoscopic structure, a mesoporous TiO2 layer was fabricated by spin coating 24 nm TiO2 nano particles dispersed in ethanol with a rotation speed of 6000 rpm for 30 s. Then the sample was annealed at 550 °C for 15 min. Then a perovskite absorber layer was deposited by the fast deposition-crystallization method. A perovskite precursor solution containing 1.4 M of PbI2, and 1.4 M of MAI was prepared by dissolving all the powders in solvents mixing 632 µL of DMF and 71.0 µL of DMSO. After dropping the precursor solution, a two-step spin coating with a rotation speed of 1000 rpm for 10 s and 5000 rpm for 40 s was conducted to disperse the droplets. During the spin coating, 0.6 mL of chlorobenzene was quickly dropped 22 s after the beginning of the program. The as-spun films were annealed at 70 °C for 1 min followed by the further anneal at 100 °C for 30 min. Then a hole transport layer was spin coated using a solution of Spiro-OMeTAD (72.3 mg/mL) in chlorobenzene (1.00 mL). To increase conductivity, LiTFSI (520 mg/mL in acetonitrile, 17.5 µL) and tBP (26.8 µL) were added to the solution. The solution was spin coated with a rotation speed of 4000 rpm for 30 s and annealed for 10 min at 70 °C. At last, Au electrode with the thickness of around 80 nm was deposited by a thermal evaporation, and the area of the Au contact was more than 0.18 cm2. All processes were performed in the drying room and fabricated devices were stored in the dry room for a day before the measurements.

Device evaluation

The current–voltage (I–V) curves were measured and recorded under AM 1.5G illumination (100 mW/cm2) with a 450 W xenon light source (YSS-80A; Yamashita Denso Co., Ltd., Japan). The light source was calibrated using a silicon photodiode of BS-520 (Bunkoukeiki Co., Ltd., Japan). Scan speed of the measurement was fixed as 100 mV/s. The EQE spectrum was recorded with an EQE system (CEP-2000MLQ, Bunkoukeiki Co., Ltd.) in the DC mode without any voltage bias. A black mask was used to confirm the device photoactive area of 0.18 cm2 during the I–V and EQE measurements. Surface and cross section morphology was observed using a field emission scanning electron microscope (SEM, SU 8000, Hitachi). X-ray diffraction (XRD) measurement was carried out on a Bruker D8 Discover with Cu K-alpha radiation (λ = 0.15406 nm). Surface roughness measurement was operated with a laser microscope (OLYMPUS, LEXT OLS4000) for a sample area of 258 μm × 258 μm.

Data availability

All data generated or analyzed during this study are included in this published article (and its Supplementary Information files).

References

Green, M. A., Ho-Baillie, A. & Snaith, H. J. The emergence of perovskite solar cells. Nat. Photonics 8, 506–514 (2014).

Stranks, S. D. et al. Electron-hole diffusion lengths exceeding 1 micrometer in an organometal trihalide perovskite absorber. Science 342, 341–344 (2013).

Dong, Q. et al. Electron-hole diffusion lengths > 175 mm in solution-grown CH3NH3PbI3 single crystals. Science 347, 967–970 (2015).

Giorgi, G., Fujisawa, J. I., Segawa, H. & Yamashita, K. Small photocarrier effective masses featuring ambipolar transport in methylammonium lead iodide perovskite: A density functional analysis. J. Phys. Chem. Lett. 4, 4213–4216 (2013).

Yin, W. J., Shi, T. & Yan, Y. Superior photovoltaic properties of lead halide perovskites: Insights from first-principles theory. J. Phys. Chem. C 119, 5253–5264 (2015).

Kojima, A., Teshima, K., Shirai, Y. & Miyasaka, T. Organometal halide perovskites as visible-light sensitizers for photovoltaic cells. J. Am. Chem. Soc. 131, 6050–6051 (2009).

The National Renewable Energy Laboratory (NREL). Best Research-Cell Efficiency Chart. https://www.nrel.gov/pv/cell-efficiency.html. (Accessed 26 Jan 2022).

Kim, G. et al. Impact of strain relaxation on performance of a-formamidinium lead iodide perovskite solar cells. Science 370, 108–112 (2020).

Yoo, J. J. et al. Efficient perovskite solar cells via improved carrier management. Nature 590, 587–593 (2021).

Jeong, J. et al. Pseudo-halide anion engineering for α-FAPbI3 perovskite solar cells. Nature 592, 381–385 (2021).

Nakazaki, J. & Segawa, H. Evolution of organometal halide solar cells. J. Photochem. Photobiol. C Photochem. Rev. 35, 74–107 (2018).

Jena, A. K., Kulkarni, A. & Miyasaka, T. Halide perovskite photovoltaics: Background, status, and future prospects. Chem. Rev. 119, 3036–3103 (2019).

Shahiduzzaman, M. et al. The benefits of ionic liquids for the fabrication of efficient and stable perovskite photovoltaics. Chem. Eng. J. 411, 128461 (2021).

Cojocaru, L. et al. Temperature effects on the photovoltaic performance of planar structure perovskite solar cells. Chem. Lett. 44, 1557–1559 (2015).

Cojocaru, L. et al. Origin of the hysteresis in I–V curves for planar structure perovskite solar cells rationalized with a surface boundary-induced capacitance model. Chem. Lett. 44, 1750–1752 (2015).

Cojocaru, L. et al. Simulation of current-voltage curves for inverted planar structure perovskite solar cells using equivalent circuit model with inductance. Appl. Phys. Express 10, 4–7 (2017).

Eames, C. et al. Ionic transport in hybrid lead iodide perovskite solar cells. Nat. Commun. 6, 2–9 (2015).

Calado, P. et al. Evidence for ion migration in hybrid perovskite solar cells with minimal hysteresis. Nat. Commun. 7, 1–10 (2016).

Frost, J. M. et al. Atomistic origins of high-performance in hybrid halide perovskite solar cells. Nano Lett. 14, 2584–2590 (2014).

Chen, H. W., Sakai, N., Ikegami, M. & Miyasaka, T. Emergence of hysteresis and transient ferroelectric response in organo-lead halide perovskite solar cells. J. Phys. Chem. Lett. 6, 164–169 (2015).

Cojocaru, L. et al. Surface treatment of the compact TiO2 layer for efficient planar heterojunction perovskite solar cells. Chem. Lett. 44, 674–676 (2015).

Murakami, T. N. et al. Adjustment of conduction band edge of compact TiO2 layer in perovskite solar cells through TiCl4 treatment. ACS Appl. Mater. Interfaces 9, 36708–36714 (2017).

Shahiduzzaman, M. et al. Compact TiO2/anatase TiO2 single-crystalline nanoparticle electron-transport bilayer for efficient planar perovskite solar cells. ACS Sustain. Chem. Eng. 6, 12070–12078 (2018).

Shahiduzzaman, M. et al. Low-temperature-processed brookite-based TiO2 heterophase junction enhances performance of planar perovskite solar cells. Nano Lett. 19, 598–604 (2019).

Sun, X., Di, C. A. & Liu, Y. Engineering of the dielectric-semiconductor interface in organic field-effect transistors. J. Mater. Chem. 20, 2599–2611 (2010).

Geiger, M. et al. Effect of the degree of the gate-dielectric surface roughness on the performance of bottom-gate organic thin-film transistors. Adv. Mater. Interfaces 7, (2020).

Wu, P. et al. Lattice mismatch induced nonlinear growth of graphene. J. Am. Chem. Soc. 134, 6045–6051 (2012).

Kinjo, R., Kawayama, I., Murakami, H. & Tonouchi, M. Thickness dependence of dielectric characteristics of SrTiO3 thin films on MgAl2O4 substrates. Adv. Mater. Phys. Chem. 2013, 58–61 (2013).

Xiao, M. et al. A fast deposition-crystallization procedure for highly efficient lead iodide perovskite thin-film solar cells. Angew. Chem. 126, 10056–10061 (2014).

Wächtler, C., Wüstefeld, C., Šíma, M., Pikner, J. & Rafaja, D. Influence of the substrate treatment on the microstructure and properties of chemical vapour deposited Ti(C, N) coatings. Surf. Coat. Technol. 466, 129675 (2023).

Stoumpos, C. C., Malliakas, C. D. & Kanatzidis, M. G. Semiconducting tin and lead iodide perovskites with organic cations: Phase transitions, high mobilities, and near-infrared photoluminescent properties. Inorg. Chem. 52, 9019–9038 (2013).

Li, Z. et al. Acid additives enhancing the conductivity of spiro-OMeTAD toward high-efficiency and hysteresis-less planar perovskite solar cells. Adv. Energy Mater. 7, 1601451 (2017).

Shi, D. et al. Low trap-state density and long carrier diffusion in organolead trihalide perovskite single crystals. Science 347, 519–522 (2015).

Lampert, M. A. Simplified theory of space-charge-limited currents in an insulator with traps. Phys. Rev. 103, 1648–1656 (1956).

Lampert, M. A., Rose, A. & Smith, R. W. Space-charge-limited currents as a technique for the study of imperfections in pure crystals. J. Phys. Chem. Solids 8, 464–466 (1959).

Grovenor, C. R. M. M. Grain boundaries in semiconductors. J. Phys. C Solid State Phys. 18, 4079–4119 (1985).

Long, R., Liu, J. & Prezhdo, O. V. Unravelling the effects of grain boundary and chemical doping on electron-hole recombination in CH3NH3PbI3 perovskite by time-domain atomistic simulation. J. Am. Chem. Soc. 138, 3884–3890 (2016).

DeQuilettes, D. W. et al. Impact of microstructure on local carrier lifetime in perovskite solar cells. Science 348, 683–686 (2015).

Tang, Z. et al. Hysteresis-free perovskite solar cells made of potassium-doped organometal halide perovskite. Sci. Rep. 7, 1–7 (2017).

Tang, Z. et al. Modulations of various alkali metal cations on organometal halide perovskites and their influence on photovoltaic performance. Nano Energy 45, 184–192 (2018).

Chen, J. et al. Preferentially oriented large antimony trisulfide single-crystalline cuboids grown on polycrystalline titania film for solar cells. Commun. Chem. 2, 1–9 (2019).

Dubrovskiǐ, V. G. & Cirlin, G. E. Growth kinetics of thin films formed by nucleation during layer formation. Semiconductors 39, 1267–1274 (2005).

Liu, Z. et al. High-adhesion stretchable electrodes based on nanopile interlocking. Adv. Mater. 29, 1–8 (2017).

Acknowledgements

This work was supported by JST SPRING, Grant Number JPMJSP2108. Also, authors thank the New Energy and Industrial Technology Development Organization (NEDO, Japan) for their financial supports.

Author information

Authors and Affiliations

Contributions

S.T., S.U. and H.S. developed the basic concept. S.T. did all the experiments including the fabrication and evaluation of the PSC devices. S.U. and H.S. provided technical advice regarding PSCs. P.J. and S.K. supplied the flat FTO. S.T., S.U., and H.S. analyzed the data and S.T. prepared all the figures in this paper. S.T. wrote the main manuscript. All authors discussed the results and revised the paper.

Corresponding authors

Ethics declarations

Competing interests

The authors declare no competing interests.

Additional information

Publisher's note

Springer Nature remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

Supplementary Information

Rights and permissions

Open Access This article is licensed under a Creative Commons Attribution 4.0 International License, which permits use, sharing, adaptation, distribution and reproduction in any medium or format, as long as you give appropriate credit to the original author(s) and the source, provide a link to the Creative Commons licence, and indicate if changes were made. The images or other third party material in this article are included in the article's Creative Commons licence, unless indicated otherwise in a credit line to the material. If material is not included in the article's Creative Commons licence and your intended use is not permitted by statutory regulation or exceeds the permitted use, you will need to obtain permission directly from the copyright holder. To view a copy of this licence, visit http://creativecommons.org/licenses/by/4.0/.

About this article

Cite this article

Takahashi, S., Uchida, S., Jayaweera, P.V.V. et al. Impact of compact TiO2 interface modification on the crystallinity of perovskite solar cells. Sci Rep 13, 16068 (2023). https://doi.org/10.1038/s41598-023-43395-1

Received:

Accepted:

Published:

DOI: https://doi.org/10.1038/s41598-023-43395-1

Comments

By submitting a comment you agree to abide by our Terms and Community Guidelines. If you find something abusive or that does not comply with our terms or guidelines please flag it as inappropriate.