Abstract

In this paper, a new design of a non-isolated high-voltage gain DC/DC converter that operates at a reasonable duty cycle, by merging the dual boost converter with the switched inductor structure, is presented as a solution for the high-conversion ratio requirement. The proposed converter operates in discontinuous-current mode (DCM) with zero current switching for all switches and diodes. Wide duty cycle range operation, high output voltage gain, low switching stress, small switching losses, and high efficiency are achieved efficiently. Operating the converter in DCM can support a wide range of the duty cycle operation, maintain lower voltage stress of all devices, ensure the same current sharing among inductors, make it easy to control, provide more stability, and require a smaller inductor which reduces size and weight of the proposed converter. Moreover, the converter operates with a continuous input current. These features make the converter a good choice for many applications such as photovoltaic, x-ray, fuel cells, etc. To prove the converter’s effectiveness, theoretical analysis, project specifications, and operation principles are presented and studied. Experimental results in an open and closed-loop, and a comparison with other recent converters are also introduced to confirm the validity of the proposed converter.

Similar content being viewed by others

Introduction

Scientists have been interested in renewable energy sources such as photovoltaic (PV) to produce electricity because they appeared to be the most efficient and effective solution to the environmental problems that the world faces today. The unregulated low-level DC output voltage from these sources is considered the biggest and the most important challenge that requires to be boosted to a regulated higher level using power electronic conditioning. The power electronic interface specification is dependent not only on the renewable energy supply but also on its effects on the power-system operation1. To obtain the voltage step-up function, a conventional non-isolated DC/DC boost converter was used2 because of its simple structure, simple control, and low cost. But it provided a limited practical gain because of their parasitic elements and must be operated at an extreme duty cycle in order to obtain high voltage gain. That causes a high-semiconductors voltage stress, diode reverse recovery problems, and high switching loss which decrease the system performance and efficiency. In3, cascaded boost converter has been successful in solving some of the problems appeared with conventional boost converter as it can attain a reasonable high voltage gain without working at extreme duty cycle, and the voltage stress through the switches remains lower than the voltage across the load. But, it has higher losses, lower efficiency, and electromagnetic interference problems. In switched-capacitor-based converters4,5 and switched capacitor/switched inductor-based converters6,7,8,9 high-voltage gain with small duty cycle, small voltage stress across the switches can be attained, and these converters can be used in a wide range of power. However, they have some problems such as higher losses, lower efficiency, electromagnetic interference problems, and reverse recovery problem.

The use of high-frequency transformers can increase the voltage gain as well as isolation, and then, full-bridge-based topologies can be used10, but with limited power capability, higher losses, lower efficiency, and higher cost. Full-bridge, half-bridge, fly back, forward, and push–pull converters are used at various voltage and power levels11,12,13,14 where isolation is needed. However, they suffer from numerous restrictions which reduce their efficiency, reduce performance in high step-up applications, and make the system more complicated and bulkier. They have also a limited range of increasing the voltage level besides higher voltage stress. Also, a massive turn-off voltage spikes in the power switch is generated due to the leakage inductance, which results in additional voltage stress on the components that require a snubber circuit to clamp the switch voltage resulting in a bigger size and more expensive. A high gain DC/DC converter utilizing coupled inductor and voltage multiplier cell that achieves high gain at a small duty ratio, and low voltage stress across the semiconductor components is presented in15. However, it is a hard switching circuit that shortens the life of its components, furthermore, the voltage multiplier cell makes the system bulky and more expensive. Magnetically coupled inductors topologies are presented in16,17,18 which increase the output voltage gain of the converter with transfer energy stored in coupled inductance and decrease the normalized voltage stress across the semiconductors. However, a clamping circuit is needed to prevent switching spikes and recover the leakage energy due to the leakage inductance which produces voltage spikes and ringing.

Recently, several DC/DC converters are presented such as a high voltage gain quasi-Z-source DC/DC converter19 that gives a high voltage gain at the low duty cycle and low voltage stress on the semiconductors. However, it works with hard switching making more losses that affect the system performance and efficiency, and it has a limited gain as it is used only for duty cycles less than 0.3. In20, a single switch DC/DC converter with non-coupled inductors is used that achieves high voltage gain with high efficiency. The major drawback is it has a large number of passive components that make the system bulkier and more expensive. A high voltage gain p-type DC/DC converter is presented in21 that has the advantages of high gain with small duty cycle, continuous input current, common ground, and low voltage stress on semiconductors devices. However, it operates with hard switching and requires a high number of components that making the system larger and more expensive. To improve the voltage gain, a single switch three-Z-network converter is presented in22. Although a high voltage gain is achieved, it has a large number of passive components which increase the losses and reduce the efficiency. An impedance network DC/DC boost converter is used in23 that reaches a high voltage gain with a small number of diodes and small duty cycle that avoids instability caused by saturation of its inductors. But, the main drawback of the converter is the lower efficiency. In24, a step-up DC/DC converter with switched capacitor cells is presented. The converter provides high voltage gain at low duty ratios, low voltage stress on the switches and, switched capacitors, and it can be expanded. However, it has a large number of active and passive components that makes the converter size larger and more expensive.

A single power switch high gain DC/DC converter with advantages of continuous input current, a small number of active components, and low voltage stress across the power switch and diodes is proposed in25. But, it is limited power and has a large number of passive components. A non-isolated high gain DC/DC converter for dc micro grid applications with a single switch is presented in26, with the advantage of simple control, and low voltage stress across the semiconductor devices. Even so, it operates with hard switching and has a large number of passive components. A transformer-less DC/DC converter based on a coupled inductor and switched capacitor–boosting techniques that increase the voltage gain with a low duty cycle is presented in27. Although the voltage stresses across the active components are reduced, it operates with hard switching, has large losses and large number of elements, and hence large size and high expensive. A switched-inductor double power switches high gain DC/DC converter (SL-DS-DC) with higher voltage gain is presented in28. However, it has more passive and active components which make the system bulkier and more expensive. A simple control scheme to improve the performance of a quadratic boost converter is presented in29. This scheme provides a faster transient response and better noise immunity, but it has a large number of passive components, high losses because of hard switching, low efficiency, large size, and more expensive. High gain-switched boost DC/DC converters contain switched capacitor/switched inductor cells are presented in30. The converters have advantages such as high voltage gain at non-extreme duty cycle, low voltage stresses across the switches and output diode, and they can be expanded to give higher voltage gain. To provide higher gain, more cells should be added but this makes the system bulkier and is more expensive. In31, a transformer-less high step-up DC/DC converter consisting of an active switched-inductor with quasi-Z-source circuit is offered. High voltage gain at the low duty cycle and high efficiency are achieved. The main drawback is the semiconductors’ components increased by increasing the switched-capacitor cells. A double boost-fly back converter is introduced in32, the static gain is increased with the reduction of input current ripple where a combination between two conventional boost-fly back converters with input-parallel and floating output is done. However, if the converter operates with a duty cycle less than 0.5, the input current will be discontinuous with greater ripple. Also, with the increased number of fly back cells more sensors are needed which makes the system bulkier and more expensive.

In this paper, a new design of a non-isolated high-voltage gain DC/DC boost converter operating with a reasonable duty cycle by integrating dual boost converter with switched inductor structure is presented. The proposed converter operates with soft-switching (zero current switching (ZCS) mode for all switches and diodes. High voltage gain, low switching stress, small switching losses, and high efficiency are achieved. The operating modes, steady-state analysis, and design guidelines of the proposed circuit are discussed. Experimental results for the open and closed loops are conducted to verify the validity of the proposed circuit.

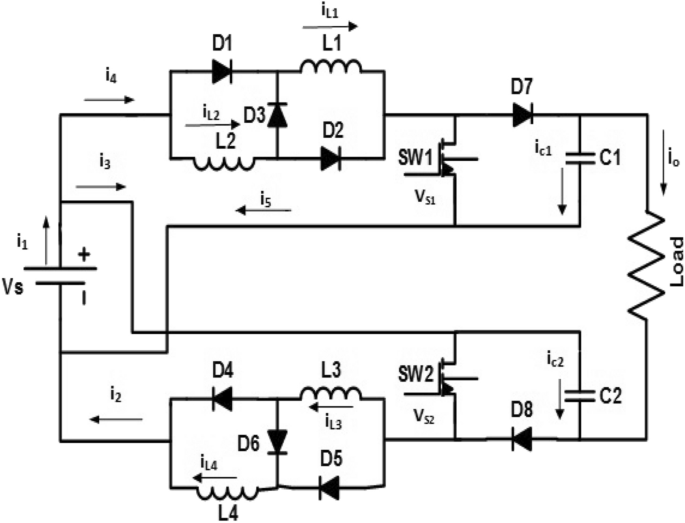

Description and operating modes

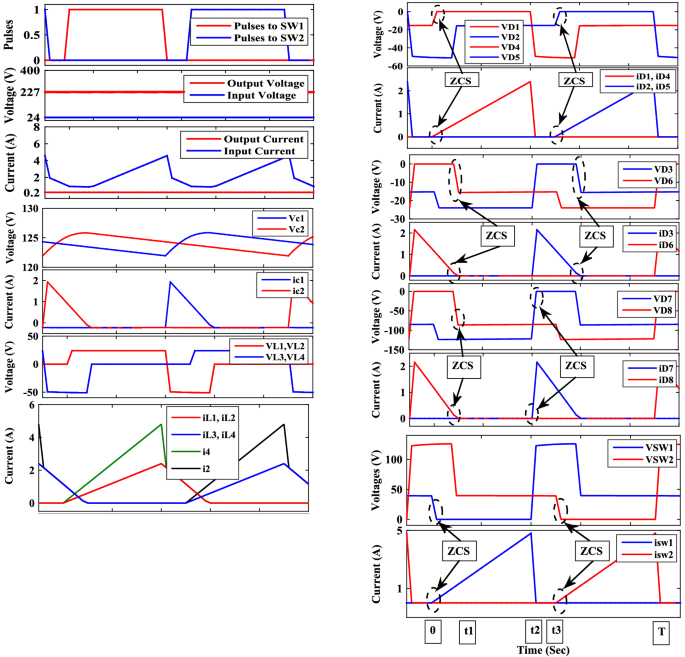

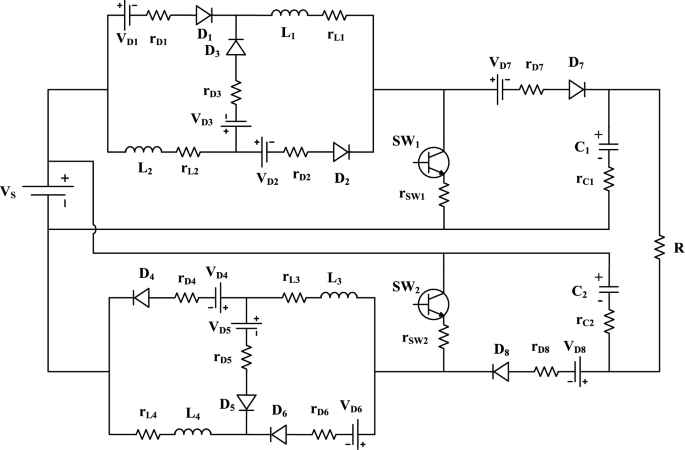

The proposed converter is composed of two similar converters connected to the same source as shown in Fig. 1. Each converter has two inductors, one capacitor, four diodes, and one switch. The four inductors have the same magnitude. The two switches are controlled in 180° phase delay to each other simultaneously. The proposed converter works in four modes as presented in Fig. 2. The key operating waveforms of the proposed converter are displayed in Fig. 3.

Mode 1

In this mode, i.e. (0 ≤ t ≤ t1), the switch SW1 turns on, the switch SW2 turns off, the diodes D3, D4, D5, and D7 are reversed biased and the diodes D1, D2, D6, and D8 are forward biased. The first switched inductors L1 and L2 are connected in parallel with each other and being charged through the input voltage source (VS) and the current through them increases. The current through the second switched inductors L3 and L4, which connected in series with each other, decreases and the voltage across them becomes VS − VC2 that charges the capacitor C2 with input source VS. However, the capacitor C1 discharges through the load. It is noted that Vs is in series with both the output capacitors where the output load voltage (Vo) is VC1 + VC2 − VS.

The voltage and current equations related to this mode are;

Mode 2

During this mode, i.e. (t1 ≤ t ≤ t2), the switch SW1 is still turn on, the switch SW2 is still turn off, the diodes D3, D4, D5, D6, D7, and D8 are reversed biased and the diodes D1 and D2 are forward biased. The first switched inductors L1 and L2 are still connected in parallel with each other and being charged through VS and the current through them still increasing. The current through the second switched inductors L3 and L4 becomes zero as the diodes D6 and D8 are reversed biased. The capacitors C1 and C2 discharged through the load, and VS is in series with them.

The voltage and current equations related to this mode are:

Mode 3

In this mode, i.e. (t2 ≤ t ≤ t3), both switches SW1 and SW2 turn off. The diodes D1, D2, D4, and D5 are reversed biased and the diodes D3, D6, D7, and D8 are forward biased. The first switched inductors L1 and L2 are connected in series with each other, and the voltage across them is VS − VC1. Also, the current through them decreases and charges the capacitor C1 with input voltage source VS as diode D7 is forward biased. The second switched inductors L3 and L4 are connected in series with each other, and the voltage across them is VS − VC2. Also, the current through them decreases and charges the capacitor C2 with input voltage source VS as diode D8 is forward biased. Both the output capacitors are charged, and their voltage increases. They are in series with VS.

The voltage and current equations related to this mode are;

Mode 4

In this mode, i.e. (t3 ≤ t ≤ TS), the switch SW1 is still turn off and the switch SW2 is still turn on. The diodes D1, D2, D3, D6, D7, and D8 are reversed biased, and the diodes D4 and D5 are forward biased. The current through the first switched inductor L1 and L2 becomes zero as the diodes D3 and D7 are reversed biased. The second switched inductors L3 and L4 are still connected in parallel with each other and being charged through VS, and the current through them still increasing. The capacitors C1 and C2 discharged through the load, and Vs is in series with both the output capacitors.

The voltage and current equations related to this mode are;

Derivation of voltage gain

For the analysis point of view, the power losses are ignored. For the reason that both converters are boost type, it is assumed that the capacitor voltages VC1 and VC2 are larger than the input voltage VS. Also, both converters have equal duty cycles, the same value of inductances, and the output voltage for each converter has the same average value.

During the on-state for one converter, the switch SW is closed. Therefore, the input voltage VS appears across the switched inductors. As a result, a change in the current ΔiL flows through the switched inductors during a time period Δt by the formula: ΔiL = (1/Leq1) VS Δt.

where Leq1 is the equivalent inductance of the switched inductors during the on-state, and it is equal to L/2 as the two inductors are connected in parallel.

At the end of the on-state, the increase of iL is:

Alternatively, the switch SW is open during the off-state. Thus, the inductor current flows through the load. If zero voltage drops in the diode is considered, and the capacitor is large enough for its voltage to stay constant, the evolution of iL is: VS − VC = L (diL/ dt).

Then, the change of iL during the off-period is:

where Leq2 is the equivalent inductance of the switched inductors during the off-state, and it is equal to 2L as the two inductors are connected in series.

and t1 = (D + 0.2) T

On the basis that the converter works in steady-state conditions, the amount of stored energy in each of its components has to be the same at the beginning and at the ending of the commutation cycle. Particularly, the stored energy in the inductor is given by:

Therefore, the inductor current has to be the same at the start and end of the commutation cycle. This means the overall change in the current (the sum of the changes) is zero:

Substituting ΔiL-on and ΔiL-off by their expressions yields:

Each module is a separate boost converter with switched inductors. Therefore, the voltage across the output capacitors C1 and C2 can be expressed as:

As clarified through the explanation of the different modes of operation, the two output capacitors are always in series with the input voltage source. Then, the output voltage can be given by:

From (12) and (13), the voltage gain of the proposed converter can be calculated by:

Design consideration

In this part, the main converter components are chosen using analytical relations derived from the converter operation. The design of inductors and capacitors depends on both the voltage across them and the current flowing through them.

Inductor Design

In case of D < 0.5, the inductors and input currents at t = T/2 can be obtained by;

The input current can be obtained by:

Using (15)–(16), the input current ripple can be expressed as:

The inductor current ripple can be expressed as:

From (17) and (18) the inductance can be obtained by:

where fS is the switching frequency.

In a similar way in case of D > 0.5, the inductors and input currents at t = T/2 can be obtained by,

Using (16) and (20), the input current ripple can be expressed as:

The inductor current ripple can be expressed as:

From (21) and (22) the inductance can be obtained by:

Finally, the larger value of the two calculated from (19) to (23) is chosen.

Capacitor Design

In case of D > 0.5, the capacitors and output voltages at t = D.T can be obtained by,

Using (13) and (24), the output voltage ripple can be expressed as:

The capacitor voltage ripple can be calculated by:

From (25) and (26), the capacitance can be obtained by:

In a similar way, in case of D < 0.5, capacitor and output voltages at t = D.T can be obtained by,

Using (13) and (28), the output voltage ripple can be expressed as:

The capacitor voltage ripple can be expressed as:

The capacitance can be obtained by:

Finally, the larger value of the two calculated from (27) and (30) is chosen.

Converter power losses and efficiency

In this section, the converter losses are analyzed by calculating the switching losses and conduction losses. The power losses of each device in the proposed converter are estimated, then the total power losses are investigated. Then, the converter efficiency is determined. The proposed converter model with the parasitic components is shown in Fig. 4. For the calculation of conduction loss in the converter, all diodes are considered with cut in voltages VD1, VD2, VD3, VD4, VD5, VD6, VD7 and VD8. Also, the internal resistances are rD1, rD2, rD3, rD4, rD5, rD6, rD7, and rD8. In a Similar way, all inductors and capacitors are also considered with a lumped DC resistance and an equivalent series resistance, respectively. They can be represented as rL1, rL2, rL3, rL4 and rC1, rC2, respectively. Both conduction and switching losses are considered for switch with on-state resistance taken as rsw1, rsw2 for both switches.

The switches losses

The practical power switch has conduction and switching losses. Assume that the two switches (SW1 and SW2) have the same rms value of current and on-state resistance.

The loss of the switching SW1 is the sum of the conduction and switching losses and can be written as:

where the switching loss of SW1 can be expressed as:

The switching loss (Ploss-switching) of the power switch SW1 can be determined by:

where trt and tft is the rise time and fall time of the switch, respectively.

Since the switches operate at ZCS during the turn-on transition period, the switching loss can be expressed as:

Then, the switching loss of SW1 is:

and the total switching loss can be expressed as:

The diodes losses

The diodes are assumed to have the same cut in voltages and equivalent series resistance,

The total diodes losses can be expressed as:

where

and,

Then, the total power loss in the diodes can be determined as:

The capacitors losses

The proposed converter contains two capacitors. The total power loss due to the two capacitors is given by:

The two capacitors are assumed have the same equivalent series resistance, then:

The rms value of current through the capacitor can be estimated using the expression:

Then total power loss due to the two capacitors is given by:

The inductors losses

The inductors loss can be expressed as

If the inductors are assumed to have the same internal resistance rL1 = rL2 = rL3 = rL4 = rL, and have the same rms value of the inductor currents.

Using the equations in the “Description and operating modes” section, the rms value of the inductor current can be noticed

Then, substituting in Eq. (45), the total power loss in the inductors can be stated as

Substituting from Eqs. (36), (40), (43), and (47) into the below equation, the total converter loss can be obtained.

The expression for total losses is as follows:

Finally, the efficiency (ɳ) of the proposed converter can now be determined as:

where Po is the output power.

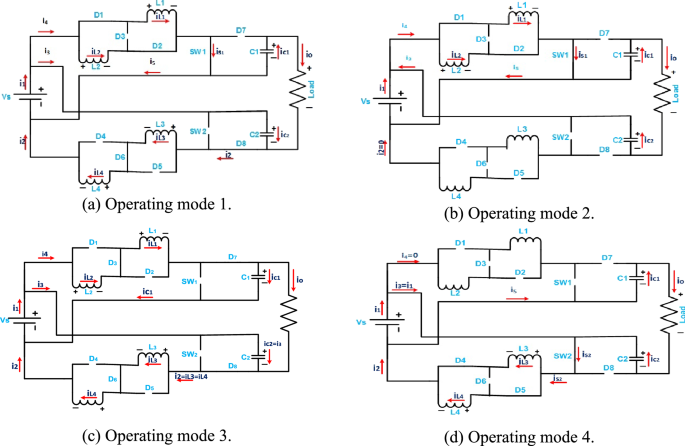

State space representation

This section presents the state space modelling of the proposed converter. The state variables in the proposed converter are selected as the inductor currents (iL1(t), iL2(t)), the capacitor voltages (vC1(t), vC2(t)), and the output voltage (vCo(t)). The input variables are chosen as the input voltage (Vs(t)) and the input current (i1(t)). The equivalent circuits showing the converter behavior of the four modes of operation are used as given in Fig. 2. The corresponding state space differential equations are obtained from these equivalent circuits. Kirchhoff’s voltage and current laws are applied for this purpose.

From equivalent circuit of Fig. 2a, the differential equations for operation mode 1 are derived as,

From equivalent circuit of Fig. 2b, the differential equations for operation mode 2 are derived as,

From equivalent circuit of Fig. 2, the differential equations for operation mode 3 are derived as,

From equivalent circuit of Fig. 2d, the differential equations for operation mode 4 are derived as,

To derive the transfer function of the proposed converter from the duty ratio to the output voltage, the previous differential equations are used.

The average state space model can be written as:

where the coefficient matrices A, B, and C are given by:

where

State space modeling of the proposed DC-DC converter is written as:

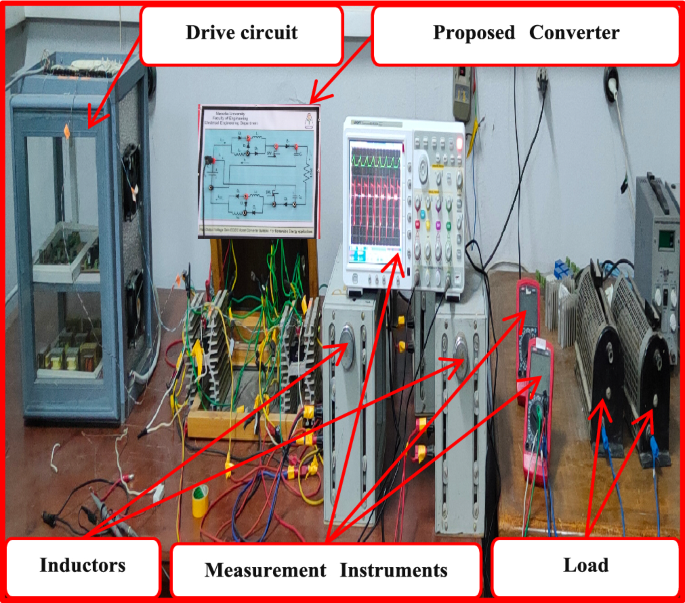

Experimental results

To prove the validity of the proposed converter, it is tested on the laboratory hardware platform as shown in Fig. 5. The schematic diagram of the experimental system is shown in Fig. 6. For experimental analysis, the converter parameters are listed in Table 1.

Open loop performance

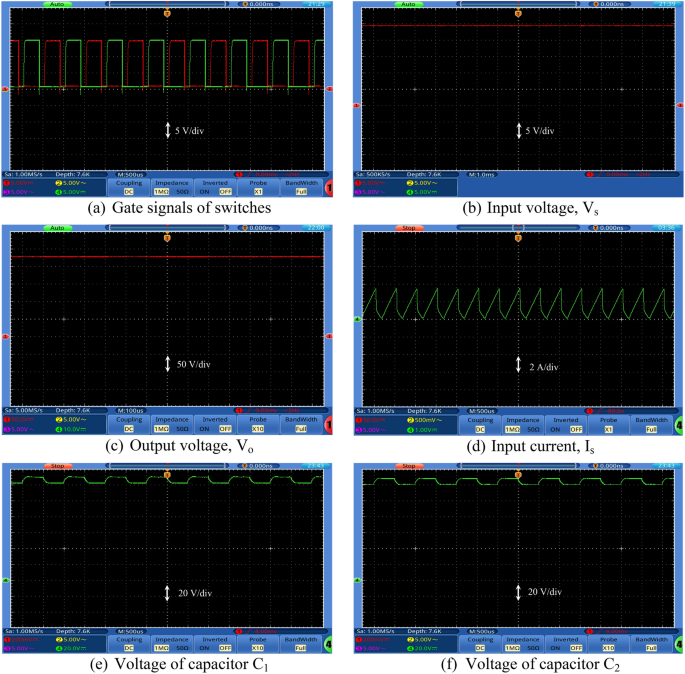

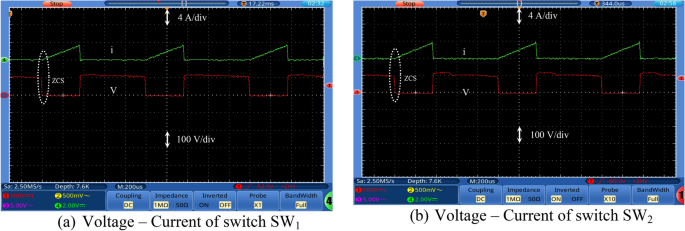

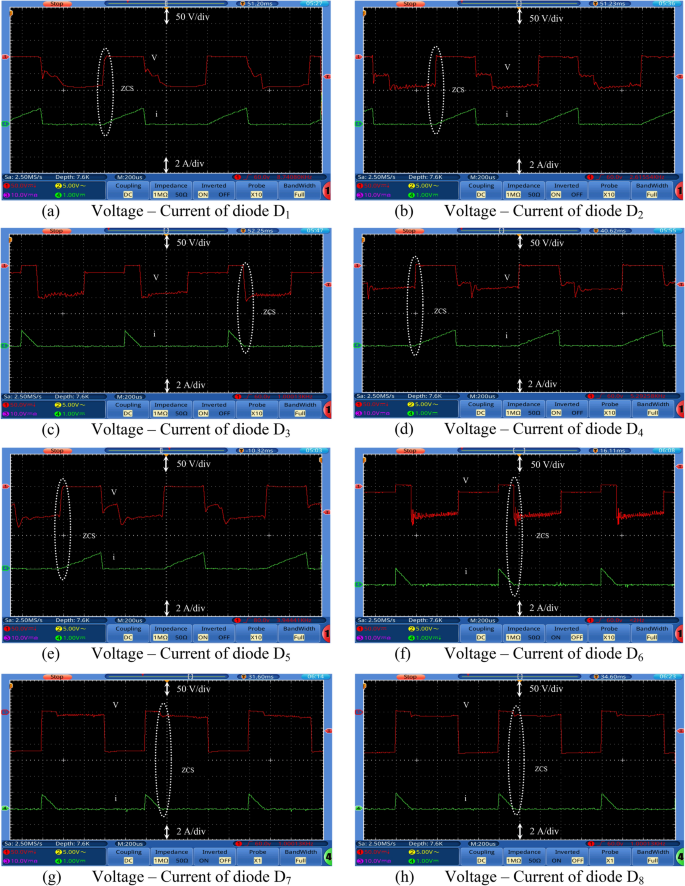

Figures 7, 8, 9 and 10 show the experimental waveforms of the proposed converter at duty cycle 0.4. These figures include the resulted waveforms of the gate signal of switches SW1 and SW2, the input and output voltages, the input current, the voltage across the capacitors, and the voltage-current of the switches, diodes, and inductors. Figure 7a shows the gate pulses of SW1 and SW2. The input voltage supplied from PV is shown in Fig. 7b and equal to 24 V. It can be seen from Fig. 7c that the output voltage equals to 226 V which gives a gain of 9.4. This performance proves that the proposed converter gives a high voltage gain at reasonable duty cycle. Figure 7d shows the continuous input current waveform. As shown in Fig. 7e,f, both the voltage of the capacitors is equal and has an average value of 125 V that is equal to 55.3% of output voltage. That ensures a low voltage stress of the capacitors, and it also achieves the Eq. (7). As shown from Fig. 8a,b, the maximum voltage across each switch (SW1 or SW2) is almost equal to 57.5% of the output voltage which shows a low voltage stress for all switches. Furthermore, all switches operate in soft switching mode (ZCS) that decrease the switching losses of the switches. Moreover, from Fig. 9, the absolute maximum voltages across diodes D1, D2, D3, D4, D5, and D6 and across diodes D7 and D8 are almost equal to 39.8% and 53.1% of the output voltage, respectively which show a low voltage stress for all diodes. Also, all diodes operate in soft switching mode (ZCS) that decrease the diodes losses.

Experimental waveforms of the proposed converter. Part III. (a) Voltage–Current of diode D1, (b) Voltage–Current of diode D2, (c) Voltage–Current of diode D3, (d) Voltage–Current of diode D4, (e) Voltage–Current of diode D5, (f) Voltage–Current of diode D6, (g) Voltage–Current of diode D7, and (f) Voltage–Current of diode D8.

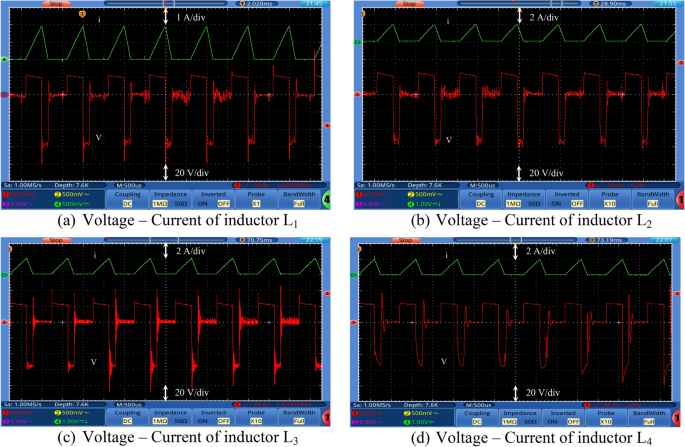

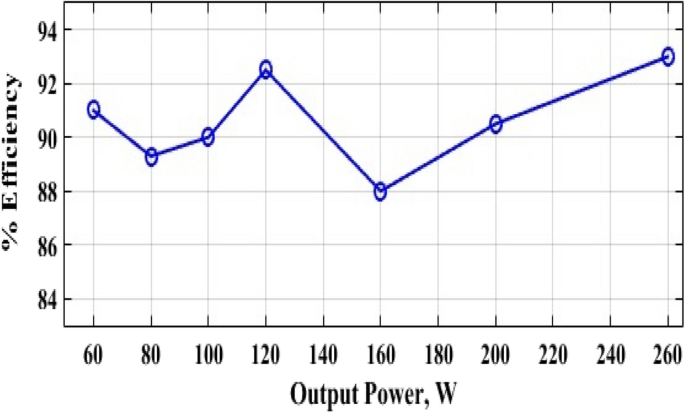

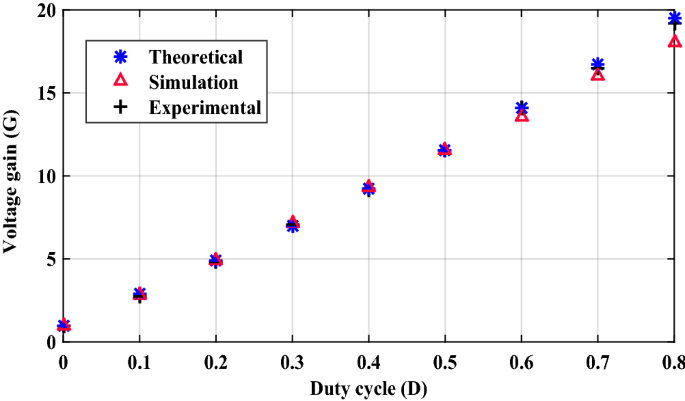

The inductor current (iL) is discontinuous as seen in Fig. 10 which shows that the converter is operating in DCM as mentioned before. Figure 11 shows the experimental measured efficiency of the proposed converter, in which it ascertains a high efficiency of the proposed topology. The maximum overall efficiency equals 93% measured at 120 W load. Figure 12 shows the voltage gain versus duty cycle of the theoretical equation, simulation results, and experimental results. It can be concluded that the experimental results are in good agreement with the theoretical analysis (Equation-14), and simulation results. From the previous experimental results, the proposed converter provides a high voltage gain with a low duty cycle, and it has small voltage stress of all semiconductor devices. Furthermore, a continuous input current is attained which a desirable feature of the DC/DC converter is making it suitable for PV applications. Therefore, it has low switching losses without any additional circuits. Also, it has components with a low nominal rating that makes the proposed converter small size, low price, and high overall efficiency. The aforementioned advantages make the proposed converter suitable for numerous industrial applications.

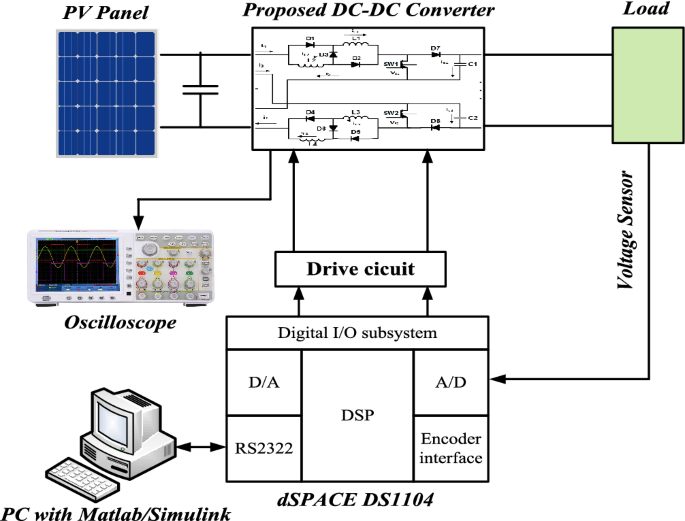

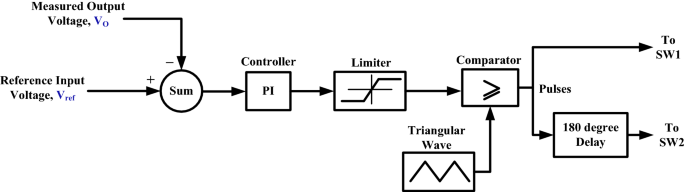

Closed loop performance

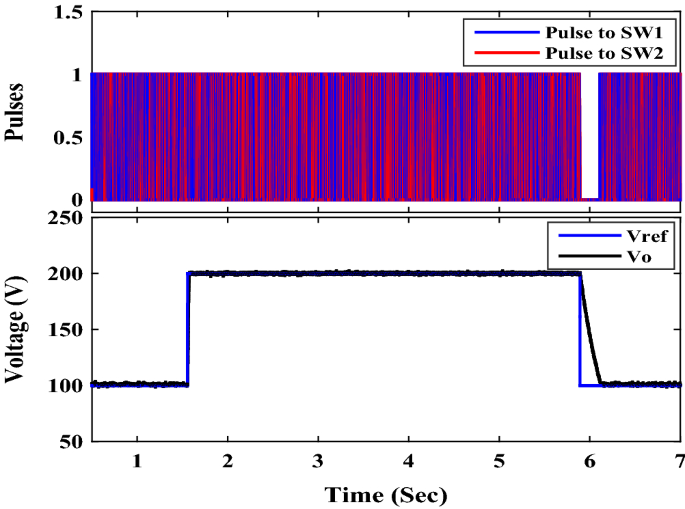

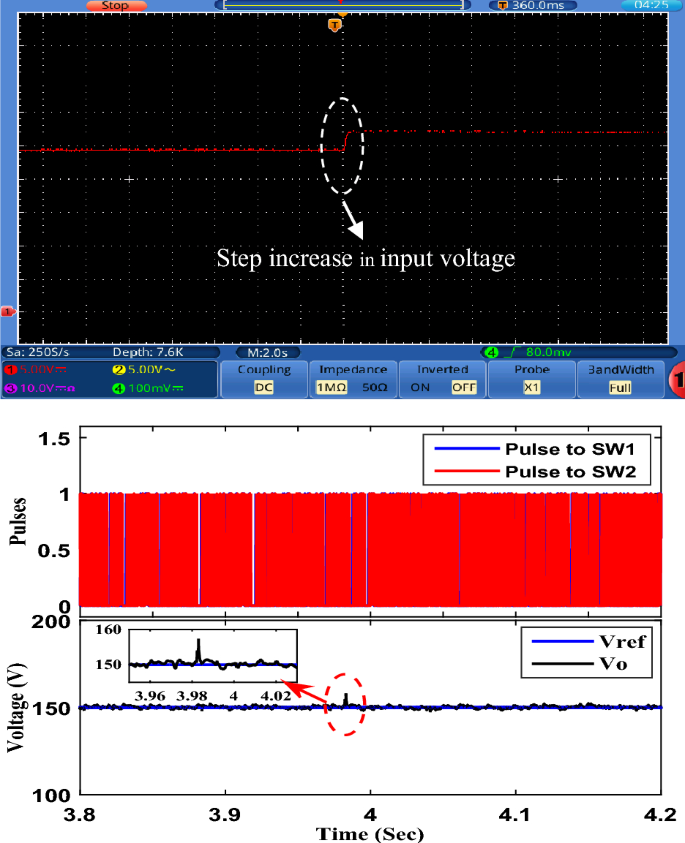

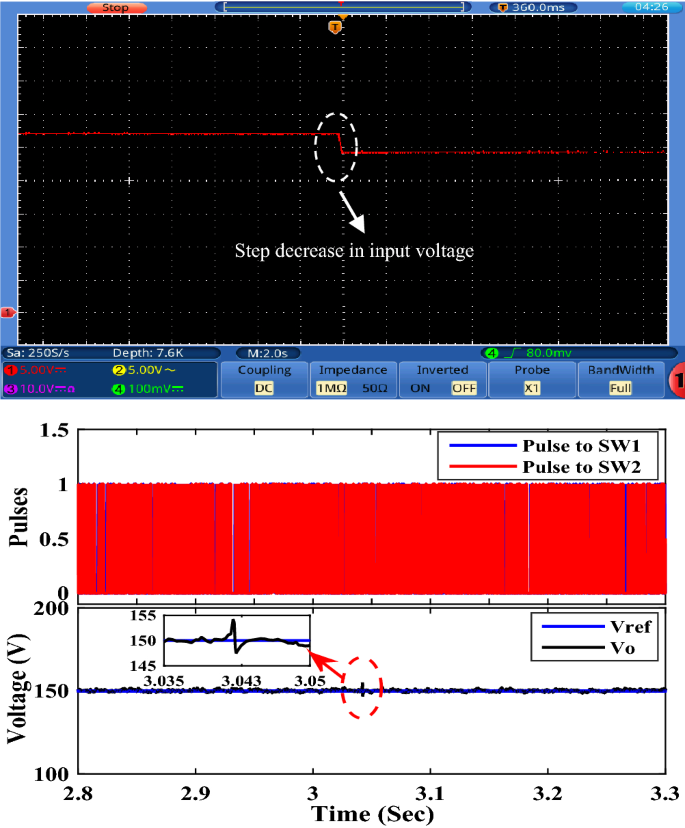

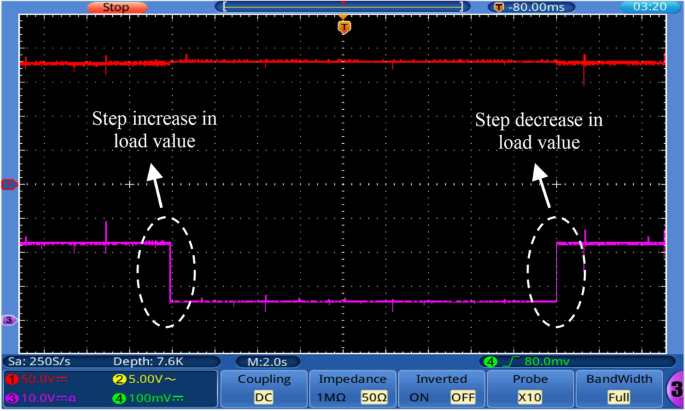

To examine the performance of the proposed converter under closed-loop control, the OWON TDS8204 oscilloscope and DSP1104 are used to record the results. PI controller is also used for control. The parameters for the PI controller are KP = 0.38 and KI = 200. A schematic diagram of the circuit that is used to control the output voltage of the proposed circuit is shown in Fig. 13. First, the proposed converter is tested by changing the reference voltage (increased/decreased) by 100 V. It can be seen from Fig. 14 that the output voltage of the proposed converter responds to the step change (increase/decrease) of the reference voltage and changes from 100 to 200 V and then from 200 to 100 V according to the value of reference voltage. Also, the transient period is found very small and less than 200 ms. Second, the proposed converter is tested by changing the input voltage source (increase/decrease) by 4 V. It can be seen from Figs. 15 and 16 that the output voltage value is remaining constant at the reference voltage value of 150 V. Also, the overshoot value is less than 7.5 V, and it is equal to 5% of the output voltage. Finally, the proposed converter is tested for variation in load values. The response to the step change (increase/decrease) in load is shown in Fig. 17. The converter is operating at 65% of full load. At first, the load increased by 35% of full load value to make the converter operate at full load, and then the load decreased by 35% of full load value to make the converter operate at 65% of the full load again. It is evident from the figure that the proposed converter operates at constant output voltage under load changes.

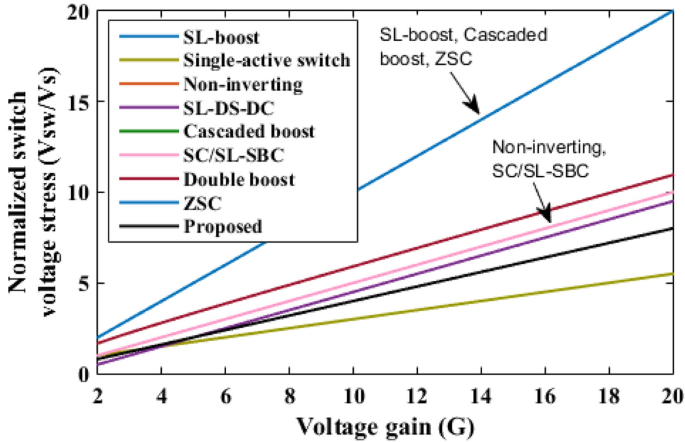

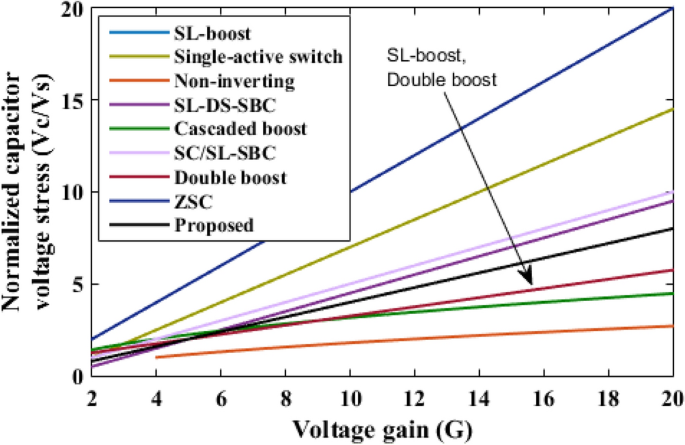

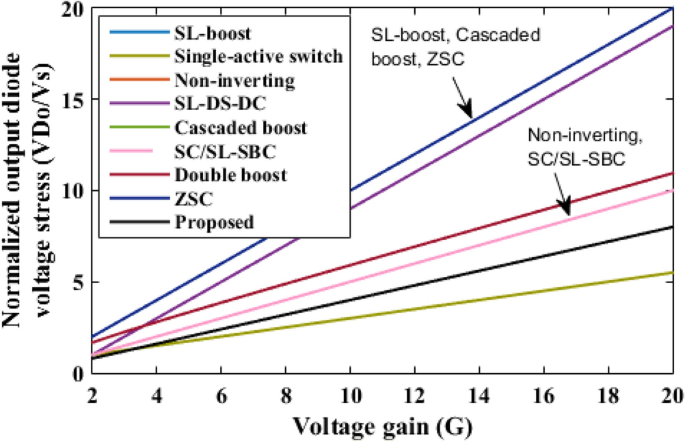

Comparison of the proposed converter with recent converters

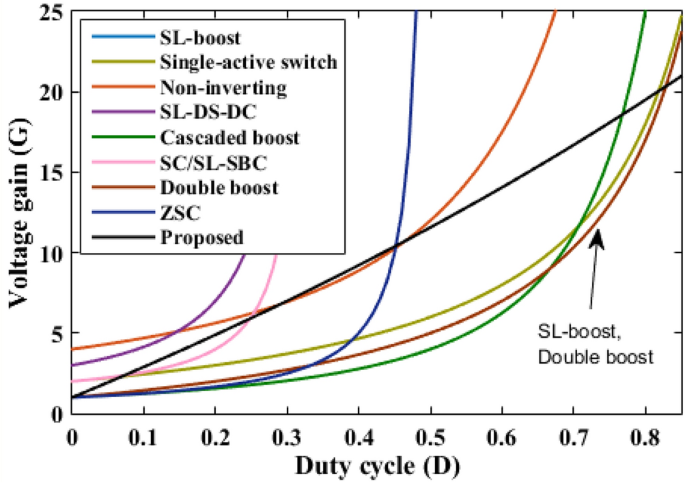

The proposed converter is compared with SL-Boost, single-active switch, non-inverting, SL-DS-DC, cascaded boost, SC/SL-SBC, double boost fly back, and ZSC converters. For a valid comparison, coupled inductor turns ratio (n) of the double boost-fly back converter was set to unity. The comparison results are presented in Table 2. The voltage gain comparison is presented in Fig. 18. It is clear that the proposed converter can operate with a wide range of duty cycle while the SL-DS-DC, and SC/SL-SBC converters operate only up to 0.3 duty cycle, and ZSC operates up to 0.5 duty cycle. Furthermore, the proposed converter has a higher gain at most of the duty cycle in comparison with SL-boost, single-active switch, cascaded boost, SC/SL-SBC, double boost fly back, and ZSC converters except SL-DS-DC converter that have the highest gain up to 0.3 only and the non-inverting converter. For the number of passive and active components, the proposed converter shows a modest number of active and passive components in comparison with SL-boost, single-active switch, non-inverting, SL-DS-DC, double boost fly back, and SC/L-SBC converters except cascaded boost and ZSC converters that have the lower components counts. However, they (cascaded boost and ZSC converters) operate at a larger duty cycle which may produce saturation problems in the inductor current or core. All the converters operate in continuous input current except the SL-boost, and ZSC converters. Also, the double boost fly back converter presents a discontinuous input current if it operates at a duty cycle of less than 0.5. The current ripple is low and within the allowed limit for all converters except the ZSC converter. Also, all converters operate with hard switching except the proposed converter that operates in soft switching for all semiconductor devices which makes lower losses and higher efficiency at higher gains. The switch voltage stress comparison is shown in Fig. 19. The proposed converter has a lower maximum switch voltage stress if it compared with all the converters except the single-active switch converter which has the smallest switch voltage stress. A lower switch voltage stress makes the losses lower and selecting a low nominal rating of switches that makes the converter small size, low price, and high overall efficiency. The capacitor voltage stress comparison is shown in Fig. 20. The proposed converter has a lower capacitor voltage stress if it compared with single-active switch, SL-DS-DC, SC/SL-SBC, and ZSC converters. A lower capacitor voltage stress gives a benefit of choosing a low nominal rating of capacitors that makes the converter smaller in size, and hence lower price. The output diode voltage stress is compared as shown in Fig. 21. The diode voltage stress of the proposed converter is lower than all the converters except the single-active switch converter. Lower voltage stress of output diode makes the nominal rating of diode much lower which affects the converter size and price. The efficiency of the proposed converter is reasonable compared to the other converters except for the cascaded boost converter which has the highest efficiency. However, the cascaded boost converter cannot accomplish a higher gain due to parasitic. Alternatively, a single-active switch converter has low voltage gain although it has similar elements count as the proposed converter. Theoretically, the converter power density depends on the number of semiconductor devices and the volume of the passive components. As known, the volume of passive components is proportional to the energy stored in them. So, if the stored energy is computed, then the volume of the passive components can be estimated. The total energy stored for the inductor is calculated by

where iL-av is average current through the inductor L, and the total energy stored for the capacitor is given as

where VC is voltage through the capacitor C.

While evaluating the energy stored in the inductor, it is assumed that the frequency and ripple currents are the same for all the compared converters. Furthermore, the energy stored in the capacitor is computed for a similar value of capacitances.

For voltage gain, G = 5, the total energy stored in the inductor and capacitor for all the converters is recorded in Table 2. It is obvious that the total energy stored, i.e., volume required is modest in the proposed topology (38). The double boost flyback converter is the smallest (27), however it has minimal voltage gain. The quantity of energy stored in inductors and capacitors that mentioned in Table 2 is made to be unitless.

Based on the previous various performance parameters and characteristics comparison, the proposed converter gives a high voltage gain at a low duty cycle. It has a modest number of semiconductor devices with low voltage stress and hence small nominal voltage rating, and lower losses making the converter smaller in size, higher efficiency, and has a good performance. According to these comparisons, the proposed converter is considered a strong competitor to the other converters.

Conclusion

In this paper, a new non-isolated high voltage gain DC/DC converter by integrating a dual boost converter with a switched inductor structure is proposed. The proposed converter operates with a modest duty cycle (less than 0.5) with a continuous input current. The converter operates with a soft switching (ZCS) for all diodes and switches which plays an important role in reducing the losses. A wide operating range of the duty cycle is available. An equal current sharing among boost inductors makes it easy to control. Also, the proposed converter offers high efficiency due to the low switching losses, lower voltage stress for all passive and active components, and the lack of reverse recovery loss on diodes. It requires a small inductor, and a small nominal rating for all semiconductor devices which reduces the size, weight, and price of the proposed converter. These features make the converter a good choice for many applications such as PV, x-ray, fuel cells, etc. Moreover, the description, operating modes in DCM, design guidelines, and open and closed-loop performance are presented. Besides, a comparative analysis with recent converters is presented. The converter is examined at various power ratings for efficiency analysis and maximum efficiency of 93% is achieved. Experimental results in open and closed-loop prove the good performance of the proposed converter.

Data availability

All data generated or analyzed during this study are included in this published article.

References

Ramanathan, J. G. G. & Urasak, N. Non-isolated interleaved hybrid boost converter for renewable energy applications. Energies 15(2), 1–14 (2022).

Paula, W., Oliveria, D. S., Pereira, D. C. & Tofoli, F. L. ‘Survey on non-isolated high-voltage step-up dc-dc topologies based on boost converter’. IET Power Elect. 8(10), 2044–2057 (2015).

Malik, M., Ali, A. & Kumar, D. A two cascaded boost converter with high voltage gain module. Int. J. Comput. Electr. Eng. 9(2), 476–483 (2017).

Karthikeyan, V., Kumaravel, S. & Gurukumar, G. High step-up gain DC–DC converter with switched capacitor and regenerative boost configuration for solar PV applications. IEEE Trans. Circuits Syst. II Exp. Briefs 66(12), 2022–2026 (2019).

Kumar, A. et al. A high voltage gain DC–DC converter with common grounding for fuel cell vehicle. IEEE Trans. Veh. Technol. 69(8), 8290–8304 (2020).

Axelrod B., Berkovich Y. & Ioinovici, A. Switched capacitor (SC)/switched inductor (SL) structures for getting hybrid step-down Cuk/Sepic/Zeta converters. In IEEE International Symposium Circuits Systems, Kos, Greece, 5063–5066 (2006).

Axelrod, B., Berkovich, Y. & Ioinovici, A. Switched capacitor/switched inductor structures for getting transformerless hybrid DC–DC PWM converters. IEEE Trans. Circuits Syst. Reg. Pap. 55(2), 687–696 (2008).

Tewari, N. & Thazhathu, S. Family of modular, extendable and high gain dc–dc converter with switched inductor and switched capacitor cells. IET Power Elect. 13(7), 1321–1331 (2020).

Kumar, A. et al. Switched-LC based high gain converter with lower component count. IEEE Trans. Ind. Appl. 56(3), 2816–2827 (2020).

Lu, J., Stegen, S. & Butler, D. High frequency and high-power density transformers for DC/DC converter used in solar PV system. In IEEE 2nd International Symposium on Power Electronics for Distributed Generation Systems, Hefei, China 481–484 (2010).

Suryadevara, R. & Parsa, L. Full-bridge ZCS-converter-based high-gain modular DC–DC converter for PV integration with medium-voltage DC grids. IEEE Trans. Energy Conv. 34(1), 302–312 (2019).

Chu, G. M. L., Lu, D. D. C. & Agelidis, V. G. Flyback-based high step-up converter with reduced power processing stages. IET Power Electron. 5(3), 349–357 (2012).

Joseph, P. & Devaraj, E. Design of hybrid forward boost converter for renewable energy powered electric vehicle charging applications. IET Power Electron. 12(8), 2015–2021 (2019).

Bilsalam, A., Boonyaroonate, I. & Chunkag, V. High-voltage gain zero-current switching push–pull resonant converter for small energy sources. IET Power Electron. 9(4), 835–845 (2016).

Fan, X. et al. High voltage gain DC/DC converter using coupled inductor and VM techniques. IEEE Access 8, 131975–131987 (2020).

Kumar, A. et al. Modified a-source converter operating at lower voltage stress. IEEE Access 7, 179670–179678 (2019).

Shi, Z. H., Cheng, K. W. E. & Ho, S. L. Static performance and parasitic analysis of tapped-inductor converters. IET Power Electron. 7(2), 366–375 (2014).

Wai, R. J. & Duan, R. Y. High step-up converter with coupled inductor. IEEE Trans. Power Electron. 20(5), 1025–1035 (2005).

Meinagh, F. A. A., Yuan, J. & Yang, Y. Analysis and design of a high voltage-gain quasi-Z-source DC–DC converter. IET Power Electron. 13(9), 1837–1847 (2020).

Mizani, M., Ansari, S. A., Shoulaie, A., Davidson, J. N. & Foster, M. P. ‘Single-active switch high-voltage gain DC–DC converter using a non-coupled inductor’. IET Power Electron. 14(2), 492–502 (2021).

Eshkevari, A. L., Mosallanejad, A. & Sepasian, M. S. Design, analysis, and implementation of a new high-gain P-type step-up dc/dc converter with continuous input current and common ground. IET Power Electron. 14(1), 225–238 (2021).

Zhang, G. et al. 3-Z-network boost converter. IEEE Trans. Ind. Electron. 62(1), 278–288 (2015).

Zhang, G. et al. An impedance network boost converter with a high-voltage gain. IEEE Trans. Power Electron. 32(9), 6661–6665 (2017).

Abbasi, M., Nazari, Y., Abbasi, E. & Li, L. A new transformer-less step-up DC–DC converter with high voltage gain and reduced voltage stress on switched-capacitors and power switches for renewable energy source applications. IET Power Electron. 14(7), 1347–1359 (2021).

Mahmood, A. et al. A non-inverting high gain DC–DC converter with continuous input current. IEEE Access. 9, 54710–54721 (2021).

Khan, S. et al. A new transformerless ultra high gain DC–DC converter for DC microgrid application. IEEE Access 9, 124560–124582 (2021).

Ghaffarpour, M., Ebrahimi, R., Kojabadi, H. M., Chang, L. & Guerrero, J. M. Novel high voltage gain DC–DC converter with dynamic analysis. IET Power Electron. 14(3), 562–583 (2021).

Bao, D. et al. Switched Inductor double switch high gain DC–DC converter for renewable applications. IEEE Access 9, 14259–14270 (2021).

Leyva-Ramos, J., Diaz-Saldierna, L. H., Morales-Saldaæa, J. A. & Ortiz-Lopez, M. G. Switching regulator using a quadratic boost converter for wide DC conversion ratios. IET Power Elect. 2(5), 605–613 (2009).

Zhu, X., Zhang, B., Li, Z., Li, H. & Ran, L. Extended switched-boost DC–DC converters adopting switched-capacitor/switched-inductor cells for high step-up conversion. IEEE J. Emerg. Sel. Top. Power Electron. 5(3), 1020–1030 (2017).

Zhao, J., Chen, D. & Jiang, J. A novel transformerless high step-Up DC–DC converter with active switched-inductor and quasi-Z-source network. IET Power Electron. 14(9), 1592–1605 (2021).

Cardos, V., Junior, S. L., Lazzarin, T. B. & Wattrich, G. Double boost—Fly back converter. IET Power Electron. 13(6), 1163–1171 (2020).

Yang, L., Qiu, D., Zhang, B., Zhang, G. & Xiao, W. A modified Z-source DC–DC converter. In IEEE 16th European Conference on Power Electronics and Applications, Lappeenranta 1–9 (2014).

Funding

Open access funding provided by The Science, Technology & Innovation Funding Authority (STDF) in cooperation with The Egyptian Knowledge Bank (EKB).

Author information

Authors and Affiliations

Contributions

A.S.M. performed visualization, data acquisition and curation, methodology, software, supervision and reviewing and editing. AL-H.H.A. performed conceptualization, writing- original draft preparation. E.E.El-K. performed supervision, visualization, validation, reviewing and editing. M.S.Z. helped with formal analysis, writing—review, and editing.

Corresponding author

Ethics declarations

Competing interests

The authors declare no competing interests.

Additional information

Publisher's note

Springer Nature remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

Rights and permissions

Open Access This article is licensed under a Creative Commons Attribution 4.0 International License, which permits use, sharing, adaptation, distribution and reproduction in any medium or format, as long as you give appropriate credit to the original author(s) and the source, provide a link to the Creative Commons licence, and indicate if changes were made. The images or other third party material in this article are included in the article's Creative Commons licence, unless indicated otherwise in a credit line to the material. If material is not included in the article's Creative Commons licence and your intended use is not permitted by statutory regulation or exceeds the permitted use, you will need to obtain permission directly from the copyright holder. To view a copy of this licence, visit http://creativecommons.org/licenses/by/4.0/.

About this article

Cite this article

Mansour, A.S., Amer, AH.H., El-Kholy, E.E. et al. High gain DC/DC converter with continuous input current for renewable energy applications. Sci Rep 12, 12138 (2022). https://doi.org/10.1038/s41598-022-16246-8

Received:

Accepted:

Published:

DOI: https://doi.org/10.1038/s41598-022-16246-8

This article is cited by

-

Non-isolated high gain DC–DC converter with ripple-free source current

Scientific Reports (2024)

-

A new extended single-switch high gain DC–DC boost converter for renewable energy applications

Scientific Reports (2023)

-

Optimized DC–DC converter based on new interleaved switched inductor capacitor for verifying high voltage gain in renewable energy applications

Scientific Reports (2023)

Comments

By submitting a comment you agree to abide by our Terms and Community Guidelines. If you find something abusive or that does not comply with our terms or guidelines please flag it as inappropriate.