Abstract

Bilayer graphene (BLG) gapped by a vertical electric field represents a valley-symmetry-protected topological insulating state. Emergence of a new topological zero-energy mode has been proposed in BLG at a boundary between regions of inverted band gaps induced by two oppositely polarized vertical electric fields. However, its realisation has been challenged by the enormous difficulty in arranging two pairs of accurately aligned split gates on the top and bottom surfaces of clean BLG. Here we report realisation of the topological zero-energy mode in ballistic BLG, with zero-bias differential conductance close to the ideal value of 4 e 2/h (e is the electron charge and h is Planck’s constant) along a boundary channel between a pair of gate-defined inverted band gaps. This constitutes the bona fide electrical-gate-tuned generation of a valley-symmetry-protected topological boundary conducting channel in BLG in zero magnetic field, which is essential to valleytronics applications of BLG.

Similar content being viewed by others

Introduction

Ever since the topological invariant was first identified in the quantum Hall effect1, 2, many efforts have been made to explore new topological phases in condensed matter. The efforts have led to the recent discovery of a time-reversal-symmetric topological phase3 (Z 2-topology) in two4, 5 and three dimensions6, 7. Emergence of a new one-dimensional (1D) valley-symmetry-protected topological zero-energy mode has recently been proposed in bilayer graphene (BLG)8,9,10 at a boundary between regions of inverted band gaps opened by a pair of oppositely polarized vertical electric fields. However, its realisation has been challenged by the enormous difficulty in arranging two pairs of accurately aligned split gates on the top and bottom surfaces of clean BLG. Here we accurately confirm the emergence of the valley-symmetry-protected topological phase in BLG. Encapsulation of a BLG layer within two hexagonal boron nitride crystals (hBNs) led to ballistic transport of carriers in our devices. We introduced novel schemes for fabricating vertically aligned four split gates attached onto top and bottom hBNs. By fine-tuning external electric field in each region in the BLG in opposite polarities, in the absence of an external magnetic field, we observed metallic conduction even with each region of the BLG in insulating state. The zero-bias conductance along the boundary between two insulating regions was very close to the theoretical prediction, 4 e 2/h (e is the electron charge and h is Planck’s constant). Current-voltage characteristics comparing with the numerical calculation for the topologically trivial bound states formed at the band-inversion boundary reveal that the zero-bias differential conductance is attributed to the topological zero-energy states confined at the boundary. This confirms the electrical-gate-tuned realisation of a valley-symmetry-protected topological boundary channel in BLG8,9,10,11 in zero magnetic field, which affords the essential building blocks of valleytronic applications and valley-associated functionalities.

Results

The zero-energy states in BLG

The low-energy state of intrinsic BLG, Bernal-stacked two monolayer graphene sheets, can be approximated by massive chiral quasiparticle bands without a band gap as the leading term of the interlayer coupling is considered in the Hamiltonian of BLG; however, a band gap is induced and tuned by the broken inversion symmetry in an external electric field applied perpendicular to the plane of a BLG layer12, 13. The gate-tunability of the band gap and carrier density of BLG has been conveniently utilized for effective carrier confinement14,15,16,17 and has led to a theoretical proposition for a new type of symmetry-protected topological one-dimensional (1-D) channel of zero-energy mode in BLG8, 9, 11, 18.

Figure 1a,b and c illustrate schematically how the topological zero-energy mode emerges in BLG. A vertical electric field \({\overrightarrow{E}}_{{\rm{L}}}({\overrightarrow{E}}_{{\rm{R}}})\) generated by the left (right) gate voltage V L (V R) induces a band gap on the left (right) side of the BLG layer (Fig. 1a and b). For opposite polarities of \({\overrightarrow{E}}_{{\rm{L}}}\) and \({\overrightarrow{E}}_{{\rm{R}}}\), the band gap closes and reopens with inverted chirality at the boundary between the two gapped BLG regions. Thus, the gapless boundary is topologically protected in the absence of valley-mixing perturbations8, 10. There are two 1-D valley-momentum-locked zero-energy states with opposite chirality for each valley (Fig. 1c). Thus, the zero-bias differential conductance (dI/dV) along the boundary has a quantized conductance of 4 e 2/h as long as inter-valley scattering is absent. Here, the factor of 4 comes from the spin degeneracy and the two copropagating modes in a valley in the current direction. Because the symmetry-protected topological zero-energy mode in BLG is vulnerable to valley-mixing perturbations19, prevention of inter-valley scattering is key to demonstrating the topological 1-D mode with ideal 4 e 2/h conductance. Conductance values falling short of 4 e 2/h observed in a previous study20 for an AB-BA-stacked domain boundary in BLG were caused by valley-mixing scattering with diffusive transport in the device. Also a recent report on the zero-bias conductance in split dual-gated BLG21 similar to ours showed much smaller values (~0.5 e 2/h) than the prediction by disorder-induced high backward scattering at the domain boundary. In the study, the conductance of ~4 e 2/h were attained only when the 1-D backward scattering was suppressed in a high magnetic field. In this case, however, the quantized conductance of the ordinary quantum Hall edge transport may have contributed to the intended boundary-channel conductance. Thus, to clearly confirm the formation of the valley-symmetry-protected topological 1-D zero-energy mode at the boundary between the inverted band-gap regions in BLG, observation of the conductance of 4 e 2/h is highly required without applying a high magnetic field.

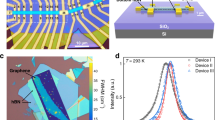

Topological zero-energy mode in bilayer graphene. (a,b) Gapped band structures of BLG corresponding to the (a) left and (b) right half. (c) Schematic illustration of the topological zero-energy mode in BLG. Different colours in a and b indicate opposite chiralities. The schematic highlighted view in c illustrates the electric current direction of each valley-momentum-locked zero-energy mode at the boundary between two oppositely dual-gated regions in BLG. (d) False-coloured scanning electron microscopy (SEM) image of the four-gated device. (e,f) Cross-sectional view along the dotted line in region I and II in d, respectively (see Method and Supplementary Fig. 7 for details).

Zero-bias conductance along the kink-potential

Figure 1d is a false-coloured scanning electron microscopy (SEM) image of our device. The extension lead of the left (right) split bottom gate is denoted as VBL (VBR). Figure 1e (f) shows a schematic cross-sectional view of the narrow corridor along the dotted line in region I (II) of Fig. 1d. The dimensions in Fig. 1e were determined by SEM and atomic force microscopy (AFM)22, 23. A negative resistance in the van der Pauw configuration confirms the ballistic transport of carriers within the device size (see Supplementary Fig. 1).

Figures 2a–c show zero-bias dI/dV obtained for the measurement configurations shown in Fig. 2d–f, respectively, for different bottom- and top-gate voltages, V BL, V BR, V TL, and V TR. Transport measurements were made using the standard lock-in technique with a frequency of 17.77 Hz at 0.3 K. We define the symmetric-gate (asymmetric-gate) configuration as that where a pair of top and bottom split gates are connected to the respective voltage sources, as shown schematically in Fig. 2d (e and f).

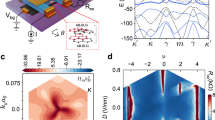

Symmetric- and asymmetric-gate configurations. (a) V TL,TR and V BL,BR (b,c) (V TR and V BR) dependence of the conductance (G) in coded colours. The white conductance region corresponds to the value of G = 4 e 2/h. Each rounded box illustrates the band gap profile of the corresponding conductance region along the dotted line in the region I in Fig. 1d. (d–f) Schematic measurement configuration. (g–i) Slice traces corresponding to dashed lines in the conductance maps in a–c. The horizontal solid lines are the quantum conductance of G = 4 e 2/h.

The colour map of Fig. 2a shows the V TL,TR and V BL,BR gate-voltage dependence of the zero-bias dI/dV in the symmetric-gate configuration. A typical feature of this dual-gated BLG is clearly seen in Fig. 2a with suppressed conductance (insulating behaviour, see Supplementary Note 1) at the upper-left and lower-right regions, even with a narrow corridor that was not covered by top and bottom gates at the centre of the device (see Fig. 1). The gating effect of the split gates was maintained across the corridor with little degradation compared with dual-gated BLG (see Method and Supplementary Fig. 2). Following the convention of the previous study12, we define the displacement field as \({\overrightarrow{D}}_{{\rm{T}}}=-{\varepsilon }_{{\rm{hBN}}}\frac{{V}_{{\rm{T}}}-{V}_{{\rm{T}}}^{0}}{{d}_{{\rm{T}}}}\hat{z}\) and \({\overrightarrow{D}}_{{\rm{B}}}={\varepsilon }_{{\rm{hBN}}}\frac{{V}_{{\rm{B}}}-{V}_{{\rm{B}}}^{0}}{{d}_{{\rm{B}}}}\hat{z}\), where, ε hBN is the dielectric constant of hBN22 (~3.9), d T (d B ) is the thickness of the top (bottom) hBN, \({V}_{{\rm{T}}}^{0}({V}_{{\rm{B}}}^{0})\) is the charge neutrality point (CNP) of V T (V B), and \(\hat{z}\) is the unit vector normal to the BLG sheet. From Fig. 2a, the CNP was determined to be \(({V}_{{\rm{T}}}^{0},\,{V}_{{\rm{B}}}^{0})=(-0.7\,{\rm{V}},1\,{\rm{V}})\). The magnitude of the average displacement field, \(|\overrightarrow{D}|=|({\overrightarrow{D}}_{{\rm{T}}}+{\overrightarrow{D}}_{{\rm{B}}})/2|\), determines the size of the band gap (E gap), and the total carrier density in BLG is estimated by \(n=\frac{{{\rm{\varepsilon }}}_{0}}{e}({\overrightarrow{D}}_{{\rm{B}}}-{\overrightarrow{D}}_{{\rm{T}}})\cdot \hat{z}\). Along the diagonal track from region ‘α’ to ‘β’ in Fig. 2a, the Fermi level (E F) is maintained in the middle of the E gap while E gap increases away from the CNP.

Figure 2b shows the conductance for an asymmetric-gate configuration with fixed V TL (=12.9 V) and V BL (=−16 V), while V TR and V BR were varied as shown in Fig. 2e. Thus, the left region of the BLG was fixed in an insulating state (at the region β in Fig. 2a), while the right region covered the entire state in Fig. 2a. Device conductance in region α is drastically enhanced in Fig. 2b, although the right region in the BLG remains in an insulating state similar to the left half. The difference in the upper left region of Figs. 2a and b results from inverted relative polarity between \({\overrightarrow{D}}_{{\rm{L}}}\) (left region) and \({\overrightarrow{D}}_{{\rm{R}}}\) (right region), i.e. depending on whether \({\overrightarrow{D}}_{{\rm{L}}}\cdot {\overrightarrow{D}}_{{\rm{R}}} > 0\) or \({\overrightarrow{D}}_{{\rm{L}}}\cdot {\overrightarrow{D}}_{{\rm{R}}} < 0\). This indicates the emergence of a topological conducting channel between the two inversely gapped regions. This feature was reproduced in another measurement configuration of Fig. 2f, plotted in Fig. 2c using the same colour scheme. In this case, the set of values for V TL and V BL were fixed at (−17.7 V, 18 V) while V TR and V BR were varied. Compared with Fig. 2b, the positions of the insulating (red) and conducting (white) regions were reversed.

The common features in Fig. 2a–c are as follows. The device exhibits insulating behaviour for \({\overrightarrow{D}}_{{\rm{L}}}\cdot {\overrightarrow{D}}_{{\rm{R}}} > 0\) (red region) and conducting behaviour for \({\overrightarrow{D}}_{{\rm{L}}}\cdot {\overrightarrow{D}}_{{\rm{R}}} < 0\) (white region) although both regions in the BLG remain in the insulating state by themselves. Figure 2g (h,i) shows slice traces corresponding to the dashed lines in Fig. 2a (b,c) for given values of V BL,BR (V BR). It is clear that the minimum conductance in each trace (corresponding to a charge neutral state in the right region) approaches 4 e 2/h of the valley-symmetric topological mode (horizontal solid lines) only for \({\overrightarrow{D}}_{{\rm{L}}}\cdot {\overrightarrow{D}}_{{\rm{R}}} < 0\).

Current-voltage characteristics of the 1-D conducting channel in BLG

Topologically trivial (non-chiral) bound states also form at the potential well (kink-potential) along the corridor. However, these bound states are separated by a finite energy from E F, which remains in the middle of the band gap along the diagonal track in Fig. 2a. Thus, the zero-bias dI/dV plotted in Fig. 2a–c is attributed to the zero-energy state formed at the kink-potential well. This fits with the theoretical prediction of valley-symmetry-protected topological zero-energy mode in the BLG8, 10.

This assertion is more clearly justified by examining the current–voltage (I–V) characteristics of the 1-D conducting channel along the corridor for \({\overrightarrow{D}}_{{\rm{L}}}\cdot {\overrightarrow{D}}_{{\rm{R}}} > 0\) and \({\overrightarrow{D}}_{{\rm{L}}}\cdot {\overrightarrow{D}}_{{\rm{R}}} < 0\), with E F fixed in the middle of the band gap. Figure 3a (b) shows I–V curves obtained for the asymmetric-gate configuration illustrated in Fig. 2e (f). For the measurements, the value of \({\overrightarrow{D}}_{{\rm{L}}}\cdot \hat{z}\) was fixed at −1.0 V/nm (+1.12 V/nm) while that of \({\overrightarrow{D}}_{{\rm{R}}}\cdot \hat{z}\) was varied from positive (the region α in Fig. 2a) to negative (the region β in Fig. 2a). Each trace in Fig. 3a and b is shifted vertically for clarity. The dotted lines indicate 4 e 2/h, to highlight the difference in the zero-bias slope for \({\overrightarrow{D}}_{{\rm{R}}}\cdot \hat{z} > 0\) and \({\overrightarrow{D}}_{{\rm{R}}}\cdot \hat{z} < 0\). The band gap profiles along the dotted line in region I of Fig. 1d are illustrated for the corresponding I–V curves denoted by the arrows.

Current–voltage (I-V) characteristics in asymmetric-gate configurations. (a,b) I–V curves obtained at different points along the diagonal track (from α to β) in (a) Fig. 2b and (b) Fig. 2c, respectively. Upper illustrations represent measurement configurations for the two sets of I–V curves. Dotted lines correspond to the slope of 4 e 2/h.

For \({\overrightarrow{D}}_{{\rm{L}}}\cdot {\overrightarrow{D}}_{{\rm{R}}} > 0\), I–V curves exhibit the typical nonlinear feature of the insulating state with a finite transport gap, which increases with E gap. Although I–V curves for \({\overrightarrow{D}}_{{\rm{L}}}\cdot {\overrightarrow{D}}_{{\rm{R}}} < 0\) also show nonlinearity for high biases, the high zero-bias dI/dV (~4 e 2/h) cannot be associated with the insulating state of the BLG. It can be explained only by assuming a conducting channel at zero energy. The slope of I-V for \({\overrightarrow{D}}_{{\rm{L}}}\cdot {\overrightarrow{D}}_{{\rm{R}}} < 0\) increases for high values of V b as additional conducting channels existing at finite energies participate in conduction.

The increase of channel conductance in the higher bias range in Fig. 3 is due to the emergence of the topologically trivial additional transverse conducting modes that are confined in the kink potential well along the corridor. Calculation of the energy levels in the kink potential based on the full structure of the Hamiltonian in BLG has been reported previously18, 21. It predicts that the energy of the lowest bound level of the trivial conducting state is a few tens of meV. In fact, in Fig. 3, the observed differential conductance dI/dV starts to increase abruptly for the bias voltage V b above a certain threshold value larger than ~10 meV. We believe that the threshold voltage corresponds to the lowest bound energy level ε 1 of the topologically trivial modes. Thus, the trivial conducting channels are distinctly separated from the topological zero-energy mode and the zero energy conductance observed in this study corresponds entirely to the topological conducting modes predicted theoretically. However, the conductance in Fig. 3 increases without any step-like features at the quantized eigenenergies of the trivial conducting levels, ε n . This feature arises because transport in the topologically trivial non-chiral bound states along the narrow conducting channel was not necessarily ballistic, as these states were not protected from non-valley-mixing perturbations, such as long-range scattering. The rapid increase of the conductance for high biases is due to conduction through the continuum state. The probing voltage level for the conductance map in Fig. 2 is ~0.5 mV which is far less than the lowest bound-state level of ~10 mV for the trivial bound states. The chiral zero-energy modes are clearly differentiated from the contribution of the topologically trivial non-chiral conducting channels.

An analysis in association with another four-gated device indicates that the precise alignment of two pairs of split gates within a few nanometres is of prime importance for observing topological 1-D conduction. In addition, controlling the thicknesses of the bottom and top hBN layers as close as possible is also essential, as the thickness ratio of the two hBN layers governs the symmetry of the top and bottom gating (see Supplementary Figs 3–5 and Supplementary Note 2). The thickness ratio was ~1.26 for the device in Fig. 1d.

Discussion

The zero-energy conducting mode observed in this study is robust as long as the valley symmetry is conserved along the corridor, similar to the robustness of the chiral edge mode protected by the time reversal symmetry in a quantum spin Hall insulator. The BLG layer in our device, encapsulated by two clean hBN single crystals, leads to the ballistic transport within the device size as shown in Supplementary Fig. 1. In addition, since the conducting channel is established inside the BLG away from the atomically rugged edge, valley-mixing scattering is suppressed significantly24. Although there may be some scattering sources such as localized states confined in the kink-potential corridor, the energy levels of those confined states are located sufficiently away from the zero energy and thus the ZBDC is hardly affected by them.

In our device, two ends of the corridor are connected to each wide region of BLG encapsulated by two hBN layers with only bottom gate. Therefore, in these two wide regions of BLG, the Fermi levels are located at the conduction bands with ballistic transport. In this case, the wide regions of the BLG become the electron reservoirs, taking a role of source and drain contacts to the 1-D conducting channel at the corridor. According to the Landauer-Buttiker formalism, the conductance of a 1-D conducting channel is determined by the potential drop at the interfaces between the reservoirs and the constricted 1-D channel. Thus, the potential drop between the wide BLG regions, on the sides of source and drain, and the corridor in our device are already included in the measured channel conductance.

The manipulation of the valley degrees of freedom, which is at the core of this study, in various two-dimensional (2-D) materials has attracted enormous attention due to their possible utilization in dissipationless valleytronics applications. However, most previous studies on the subject have focused on optical manipulation. The study of transport based on the valley degrees of freedom is still in its infancy; a valley-specific transport signal has been reported only for non-local measurements in Hall-bar-type devices25, 26. The 1-D topological carrier guiding demonstrated in this study affords a promising route to valleytronic applications and sophisticated valley associated functionalities based on 2-D materials.

Methods

Stacking procedure

For device preparation, we first encapsulated a BLG sheet between two atomically clean hexagonal boron nitride (hBN) single crystals22, 23, 27. A Gel-film (Gel-Pak, PF-30/17-X4) was attached to a slide glass, to be used as a stamp. The hBN flakes (bottom hBN) were then mechanically exfoliated onto the Gel-film using the ‘Scotch tape’ method27. The prepared stamp (bottom hBN/Gel-film/slide glass) was affixed to an optical microscope to pick up a piece of BLG, which was transferred onto a highly doped silicon wafer capped with 90-nm-thick SiO2 (SiO2/Si). After picking up the BLG, the assembled stack (bottom hBN/BLG) was deposited onto the target hBN (top hBN), which had been exfoliated onto another SiO2/Si substrate coated with double layers of polymer film consisting of water soluble poly(4-styrene sulfonic acid) (PSS) and poly(methyl methacrylate) (PMMA). Then the prepared substrate was floated on deionised water, which dissolves the PSS layer. When the SiO2/Si substrate was detached from the PMMA film, which supported the hBN/BLG/hBN heterostructure, the PMMA membrane was affixed to an optical microscope to transfer the assembled structure onto the split bottom gates patterned on another SiO2/Si substrate using standard electron-beam lithography (see Supplementary Fig. 6).

Patterning procedure

After patterning the split bottom gates, which consisted of Cr/Au (5 nm/15 nm) double layers, the hBN/BLG/hBN heterostructure was transferred onto the double layers within sub-micrometre accuracy by a similar technique to that used in the stacking processes. After patterning the bottom-gate extension leads, electrical contacts to the BLG were made by atomic edge contact, which is a method modified from a previous study23 (without removal of the bottom hBN). The pair of split-gate pads (1.5 × 1 μm2) consisting of Cr/Au (3 nm/12 nm) double layers were then deposited onto the top hBN with lateral positions aligned within a few nm accuracy by electron-gun evaporation together with electron-beam nanofabrication. During the CF4/O2 plasma etching of the device geometry, each boundary of the two split dual-gated regions in the BLG was removed using the pair of split top gates as etching stencils. To prevent electrical shortage between the BLG and top-gate extension leads, the edge of the BLG was covered with double insulating layers (120 nm-thick Al2O3 and 130-nm-thick cross-linked PMMA), followed by electron-gun evaporation of the top-gate extension leads. See Supplementary Fig. 7 for details and image for each step.

References

Thouless, D. J., Kohmoto, M., Nightingale, M. P. & den Nijs, M. Quantized Hall conductance in a two-dimensional periodic potential. Phys. Rev. Lett. 49, 405–408 (1982).

Klitzing, Kv, Dorda, G. & Pepper, M. New method for high-accuracy determination of the fine-structure constant based on quantized Hall resistance. Phys. Rev. Lett. 45, 494–497 (1980).

Kane, C. L. & Mele, E. J. Z 2 topological order and the quantum spin Hall effect. Phys. Rev. Lett. 95, 146802 (2005).

Bernevig, B. A. & Zhang, S.-C. Quantum spin Hall effect. Phys. Rev. Lett. 96, 106802 (2006).

König, M. et al. Quantum spin Hall insulator state in HgTe quantum wells. Science 318, 766–770 (2007).

Hsieh, D. et al. A topological Dirac insulator in a quantum spin Hall phase. Nature 452, 970–974 (2008).

Chen, Y. L. et al. Experimental realization of a three-dimensional topological insulator, Bi2Te3. Science 325, 178–181 (2009).

Martin, I., Blanter, Y. M. & Morpurgo, A. F. Topological confinement in bilayer graphene. Phys. Rev. Lett. 100, 036804 (2008).

Killi, M., Wei, T.-C., Affleck, I. & Paramekanti, A. Tunable Luttinger liquid physics in biased bilayer graphene. Phys. Rev. Lett. 104, 216406 (2010).

Qiao, Z., Jung, J., Niu, Q. & MacDonald, A. H. Electronic highways in bilayer graphene. Nano Lett. 11, 3453–3459 (2011).

Vaezi, A., Liang, Y., Ngai, D. H., Yang, L. & Kim, E.-A. Topological edge states at a tilt boundary in gated multilayer graphene. Phys. Rev. X 3, 021018 (2013).

Zhang, Y. et al. Direct observation of a widely tunable bandgap in bilayer graphene. Nature 459, 820–823 (2009).

Edward, M. & Mikito, K. The electronic properties of bilayer graphene. Rep. Prog. Phys. 76, 056503 (2013).

Müller, A. et al. Bilayer graphene quantum dot defined by topgates. J. Appl. Phys. 115, 233710 (2014).

Goossens, A. M. et al. Gate-defined confinement in bilayer graphene-hexagonal boron nitride hybrid devices. Nano Lett. 12, 4656–4660 (2012).

Allen, M. T., Martin, J. & Yacoby, A. Gate-defined quantum confinement in suspended bilayer graphene. Nat. Commun. 3, 934 (2012).

Varlet, A. et al. Fabry-Pérot interference in gapped bilayer graphene with broken anti-Klein tunneling. Phys. Rev. Lett. 113, 116601 (2014).

Zarenia, M., Pereira, J. M., Farias, G. A. & Peeters, F. M. Chiral states in bilayer graphene: Magnetic field dependence and gap opening. Phys. Rev. B 84, 125451 (2011).

Jung, J., Zhang, F., Qiao, Z. & MacDonald, A. H. Valley-Hall kink and edge states in multilayer graphene. Phys. Rev. B 84, 075418 (2011).

Ju, L. et al. Topological valley transport at bilayer graphene domain walls. Nature 520, 650–655 (2015).

Li, J. et al. Gate-controlled topological conducting channels in bilayer graphene. Nat. Nanotech. doi:10.1038/nnano.2016.158 http://www.nature.com/nnano/journal/vaop/ncurrent/abs/nnano.2016.158.html#supplementary-information (2016).

Dean, C. R. et al. Boron nitride substrates for high-quality graphene electronics. Nat. Nanotech. 5, 722–726 (2010).

Wang, L. et al. One-dimensional electrical contact to a two-dimensional material. Science 342, 614–617 (2013).

Kim, M. et al. Valley-symmetry-preserved transport in ballistic graphene with gate-defined carrier guiding. Nat. Phys. 12, 1022–1026 (2016).

Shimazaki, Y. et al. Generation and detection of pure valley current by electrically induced Berry curvature in bilayer graphene. Nat. Phys. 11, 1032–1036 (2015).

Sui, M. et al. Gate-tunable topological valley transport in bilayer graphene. Nat. Phys. 11, 1027–1031 (2015).

Andres, C.-G. et al. Deterministic transfer of two-dimensional materials by all-dry viscoelastic stamping. 2D Materials 1, 011002 (2014).

Acknowledgements

This work was supported by the National Research Foundation (NRF) through the SRC Center for Topological Matter, POSTECH, Korea (Grant No. 2011-0030046 for H.-J.L.) and the Elemental Strategy Initiative conducted by the MEXT and JSPS KAKENHI, Japan (Grant Numbers JP26248061, JP15K21722, and JP25106006 for K.W. and T.T.).

Author information

Authors and Affiliations

Contributions

J.L. and H.-J.L. conceived the idea and designed the project. J.L. performed the device fabrication, transport measurements, and numerical calculation. K.W. and T.T. supplied high-quality hexagonal boron nitride single crystals. J.L. and H.-J.L. analysed the results and wrote the manuscript. H.-J.L. supervised the project.

Corresponding author

Ethics declarations

Competing Interests

The authors declare that they have no competing interests.

Additional information

Publisher's note: Springer Nature remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

Electronic supplementary material

Rights and permissions

Open Access This article is licensed under a Creative Commons Attribution 4.0 International License, which permits use, sharing, adaptation, distribution and reproduction in any medium or format, as long as you give appropriate credit to the original author(s) and the source, provide a link to the Creative Commons license, and indicate if changes were made. The images or other third party material in this article are included in the article’s Creative Commons license, unless indicated otherwise in a credit line to the material. If material is not included in the article’s Creative Commons license and your intended use is not permitted by statutory regulation or exceeds the permitted use, you will need to obtain permission directly from the copyright holder. To view a copy of this license, visit http://creativecommons.org/licenses/by/4.0/.

About this article

Cite this article

Lee, J., Watanabe, K., Taniguchi, T. et al. Realisation of topological zero-energy mode in bilayer graphene in zero magnetic field. Sci Rep 7, 6466 (2017). https://doi.org/10.1038/s41598-017-06902-9

Received:

Accepted:

Published:

DOI: https://doi.org/10.1038/s41598-017-06902-9

This article is cited by

-

Topological valley transport at the curved boundary of a folded bilayer graphene

Communications Physics (2019)

Comments

By submitting a comment you agree to abide by our Terms and Community Guidelines. If you find something abusive or that does not comply with our terms or guidelines please flag it as inappropriate.