Abstract

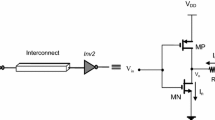

Interconnect resistance dissipates a portion of the total transient power in CMOS circuits. Conduction losses increase with larger interconnect resistance. It is shown in this paper that these losses do not add to the total power dissipation of a CMOS circuit through I 2 R losses. Interconnect resistance can, however, increase the short-circuit power of both the driver and load gates.

Similar content being viewed by others

References

S.R. Vemuru and N. Scheinberg, “Short-circuit power dissipation estimation for CMOS logic gates.” IEEE Transactions on Circuits and Systems I: Fundamental Theory and Applications, vol. 41, no. 11, pp. 762–765, 1994.

L. Bisdounis and O. Koufopavlou, “Short-circuit energy dissipation modeling for submicrometer CMOS gates.” IEEE Transactions on Circuits and Systems I: Fundamental Theory and Applications, vol. 47, no. 9, pp. 1350–1361, 2000.

L. Bisdounis, S. Nikolaidis, and O. Koufopavlou, “Propagation delay and short-circuit power dissipation modeling of theCMOS inverter.” IEEE Transactions on Circuits and Systems I: Fundamental Theory and Applications, vol. 45, no. 3, pp. 259–270, 1998.

V. Adler and E.G. Friedman, “Repeater design to reduce delay and power in resistive interconnect.” IEEE Transactions on Circuits and Systems II: Analog and Digital Signal Processing, vol. 45, no. 5, pp. 607–616, 1998.

V. Adler and E.G. Friedman, “Delay and power expressions for a CMOS inverter driving a resistive-capacitive load.” Analog Integrated Circuits and Signal Processing, vol. 14, no. 1/2, pp. 29–39, 1997.

A. Chatzigeorgiou, S. Nikolaidis, and I. Tsoukalas, “Modeling CMOS gates driving RC interconnect loads.” IEEE Transactions on Circuits and Systems II: Analog and Digital Signal Processing, vol. 48, no. 4, pp. 413–418, 2001.

Y.I. Ismail, E.G. Friedman, and J.L. Neves, “Dynamic and short-circuit power of CMOS gates driving lossless transmission lines.” IEEE Transactions on Circuits and Systems I: Fundamental Theory and Applications, vol. 46, no. 8, pp. 950–961, 1999.

G. Cappuccino and G. Cocorullo, “Time-domain model for power dissipation of CMOS buffers driving lossy lines.” IEE Electronics Letters, vol. 35, no. 12, pp. 959–960, 1999.

K.T. Tang and E.G. Friedman, “Delay and power expressions characterizing a CMOS inverter driving an RLC load,” in Proceedings of the IEEE International Symposium on Circuits and Systems, May 2000, vol. III, pp. 283–286.

A. Chandrakasan, W.J. Bowhill, and F. Fox, Design of High-Performance Microprocessor Circuits. IEEE Press, 2001.

A.S. Sedra and K.C. Smith, Microelectronic Circuits. Oxford University Press, 1998.

M.A. El-Moursy and E.G. Friedman, “Resistive power inCMOS circuits,” in Proceedings of the IEEE Midwest Symposium on Circuits and Systems, Dec. 2003.

Author information

Authors and Affiliations

Corresponding author

Rights and permissions

About this article

Cite this article

El-Moursy, M.A., Friedman, E.G. Resistive Power in CMOS Circuits. Analog Integrated Circuits and Signal Processing 41, 5–11 (2004). https://doi.org/10.1023/B:ALOG.0000038278.71500.0c

Issue Date:

DOI: https://doi.org/10.1023/B:ALOG.0000038278.71500.0c