Abstract

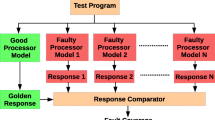

Recent studies show that at-speed functional tests are better for finding realistic defects than tests executed at lower speeds. This advantage has led to growing interest in design for at-speed tests. In addition, time-to-market requirements dictate development of tests early in the design process. In this paper, we present a new methodology for synthesis of at-speed self-test programs for microprocessors. Based on information about the instruction set, this high-level test generation methodology can generate instruction sequences that exercise all the functional capabilities of complex processors. Modern processors have large memory modules, register files and powerful ALUs with comprehensive operations, which can be used to generate and control built-in tests and to evaluate the response of the tests. Our method exploits the functional units to compress and check the test response at chip internal speeds. No hardware test pattern generators or signature analyzers are needed, and the method reduces area overhead and performance impact as compared to current BIST techniques. A novel test instruction insertion technique is introduced to activate the control/status inputs and internal modules related to them. The new methodology has been applied to an example processor much more complex than any benchmark circuit used in academia today. The results show that our approach is very effective in achieving high fault coverage and automation in at-speed self-test generation for microprocessor-like circuits.

Similar content being viewed by others

References

M.S. Abadir and M.A. Breuer, “A Knowledge Based System for Designing Testable VLSI Chips,” IEEE Design and Test of Computers, Vol. 2, No. 4, pp. 56–68, Aug. 1985.

L. Avra, “Allocation and Assignment in High-Level Synthesis for Self-Testable Data Paths,” Proc. Intl. Test Conf., 1991, pp. 463–472.

N. Mukherjee, M. Kassab, J. Rajski, and J. Tsyzer, “Arithmetic Built-In Self Test for High-Level Synthesis,” Proc. IEEE VLSI Test Symposium, 1995, pp. 132–139.

A.P. Stroele, “BIST Pattern Generators Using Addition and Subtraction Operations,” Journal of Electronic Testing: Theory and Applications, Vol. 11, No. 1, pp. 69–80, 1997.

J.E. Carletta and C.A. Papachristou, “Behavioral Testability Insertion for Datapath/Controller Circuits,” Journal of Electronic Testing: Theory and Applications, Vol. 11, No. 1, pp. 9–28, 1997.

C.A. Papachristou, S. Chiu, and H. Harmamnani, “A Data Path Synthesis Method for Self-Testable Designs,” Proc. of the Design Automation Conf., 1991, pp. 378–384.

B. Krishnamurthy, “A Dynamic Programming Approach to the Test Point Insertion Problem,” Proc. of the Design Automation Conf., 1987, pp. 695–705.

P.C. Maxwell, R.C. Aitken, V. Johnson, and I. Chiang, “The Effect of Different Test Sets on Quality Level Prediction: When is 80% better than 90%?” Proc. Intl. Test Conf., 1991, pp. 358–364.

C. Robach and G. Saucier, “Flexible Test Method for Microprocessors,” Proc. Euromicro Symposium, 1980, pp. 329–339.

M.A. Annaratone and M.G. Sami, “An Approach to Functional Testing for Microprocessors,” Proc. International Symposium on Fault-Tolerant Computing, 1982, pp. 158–164.

S.K. Jain and A.K. Susskind, “Test Strategy for Microprocessors,” Proc. of the Design Automation Conf., 1983, pp. 703- 708.

C. Bellon, R. Velazco, and H. Ziade, “Analysis of Experimental Results on Functional Testing and Diagnosis of Complex Circuits,” Proc. Intl. Test Conf., 1988, pp. 64–72.

J. Shen and J.A. Abraham, “Native Mode Functional Test Generation for Microprocessors with Applications to Self Test and Design Validation,” Proc. Intl. Test Conf., 1998.

J.A. Abraham and K.P. Parker, “Practical Microprocessor Testing: Open and Closed Loop Approaches,” Proc. COMPCON, 1981, pp. 308–311.

C. Hinchcliff, “Simplified Microprocessor Test Generation,” Proc. Intl. Test Conf., 1982, pp. 176–180.

A.J. van de Goor and O. Jansen, “Self Test for the Intel 8085,” Microprocessing and Microprogramming, Vol. 29, pp. 165–175, 1990.

T. Nierman, W.T. Cheng, and J.H. Patel, “PROOFS: A Fast, Memory-Efficient Sequential Circuit Fault Simulator,” IEEE Trans. on Computer-Aided Design of Integrated Circuits and Systems, Vol. 11, No. 2, pp. 198–207, Feb. 1992.

T. Nierman and J.H. Patel, “HITEC: A Test Generation Package for Sequential Circuits,” Proc. European Design and Test Conference, Feb. 1991, pp. 214–218.

D.G. Saab, Y.G. Saab, and J.A. Abraham, “CRIS: A Test Cultivation Program for Sequential VLSI Circuits,” Proc. Intl. Conf. on Computer-Aided Design, 1992, pp. 216–219.

K.K. Saluja and S.M. Reddy, “On Minimally Testable Logic Networks,” IEEE Transactions on Computers, Vol. 23, pp. 552–554, May 1974.

Author information

Authors and Affiliations

Rights and permissions

About this article

Cite this article

Shen, J., Abraham, J.A. Synthesis of Native Mode Self-Test Programs. Journal of Electronic Testing 13, 137–148 (1998). https://doi.org/10.1023/A:1008305820979

Issue Date:

DOI: https://doi.org/10.1023/A:1008305820979