Abstract

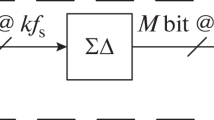

The paper presents a VHDL model of an oversampling ΣΔ analog-to-digital converter created on the behavioral hierarchy level. Although VHDL has been primarily devoted to digital circuit design, it can also be applied to certain mixed-signal circuits. The model of the analog part is as simple as possible and includes only necessary parameters that enable to determine the potential resolution of a converter. The model of the digital part is described in the synthesizable subset of VHDL and parameterized according to the word length and the type of arithmetic applied. The validation process of the converter model is also shown. It is performed by a VHDL simulator and a postprocessor tool enabling to carry out FFT. Simulation results enclosed prove the efficiency of the design approach presented.

Similar content being viewed by others

References

J. C. Candy and G. C. Temes. “Oversampling Delta-Sigma Data Converters.” IEEE Press, 1992.

W. Chou, P. W. Wong, and R. H. Gray. “Multistage sigma-delta modulation.” IEEE Trans. Inform. Theory 35(4), pp. 784–796, July 1989.

K. Hejn, P. Murphy, and I. Kale. “Measurement and Enhancement of Multistage Sigma-Delta Modulators.” IEEE Instrumentation and Measurement Technology Conference, New York, pp. 545–551, 12–14 May 1992.

R. A. Valenzuela and A. G. Constantinides. “Digital signal processing schemes for efficient interpolation and decimation.” IEE Proceedings 130, Pt. G, No. 6, pp. 225–235, December 1983.

Author information

Authors and Affiliations

Rights and permissions

About this article

Cite this article

Baraniecki, R., Dabrowski, P. & Hejn, K. Oversampling ΣΔ Analog-to-Digital Converters Modeling Based on VHDL. Analog Integrated Circuits and Signal Processing 16, 101–109 (1998). https://doi.org/10.1023/A:1008211605358

Issue Date:

DOI: https://doi.org/10.1023/A:1008211605358