Abstract

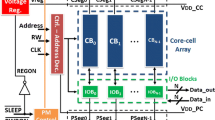

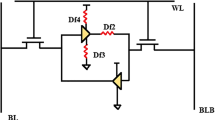

We describe the design and implementation of a dynamic power supply current sensor which is used to detect SRAM faults such as disturb faults as well as logic cell faults. A formal study is presented to assess the parameters that influence the sensor design. The sensor detects faults by detecting abnormal levels of the power supply current. The sensor is embedded in the SRAM and offers on-chip detectability of faults. The sensor detects abnormal dynamic current levels that result from circuit defects. If two or more memory cells erroneously switch as a result of a write or read operation, the level of the dynamic power supply current is elevated. The sensor can detect this elevated value of the dynamic current. The dynamic power supply current sensor can supplement the observability associated with any test algorithm by using the sensor as a substitute for the read operations. This significantly reduces the test length and the additional observability enhances defect coverages.

Similar content being viewed by others

References

W.C. Rhines, “Emerging Technologies Drive Domain-specific Solution,” Proc. of International Conference, 1996, p. 10.

S. Su and R. Makki, “Testing Random Access Memories by Monitoring Dynamic Power Supply Current,” Journal of Electronic Testing, Vol. 3, pp. 265-278, 1992.

A.J. Van de Goor, Testing of Semiconductor Memories-Theory and Practice, A.J. Van de Goor/Verzijl, The Netherlands, 1998.

W. Maly and P. Nigh, “Built-in Current Testing-A Feasibility Study,” Proc. of International Conference on Computer-Aided Design, November 1988, pp. 340-343.

J. Sas, U. Swerts, and M. Darquennes, “Towards an Effective IDDQ Vector Selection and Application Methodology,” Proc. of International Test Conference, 1996, pp. 491-500.

T. Powell, J. Pair, and B. Garbajal III, “Correlating Defects to Functional and IDDQ Tests,” Proc. of International Test Conference, 1996, pp. 501-510.

C. Hawkins, J. Soden, R. Fritzemeier, and L. Horing, “Quiescent Power Supply Current Measurement for CMOS IC Defect Detection,” IEEE Tran. on Industrial Electronics, Vol. 36, No. 2, pp. 211-218, 1989.

Y. Okudo, I.Kubota, and M.Watanabe, “Defect Level Prediction for IDDQTesting,” Proc. of International Test Conference, 1998, p. 909.

R. Rodriguez-Montanes, J. Segura,V. Champac, J. Figueras, and J. Rubio, “Current vs. Logic Testing of Gate Oxide Short, Floating Gate and Bridging Failures in CMOS,” Proc. of International Test Conference, 1991, pp. 510-519.

P. Nigh, and W. Maly, “Test Generation for Current Testing,” IEEE Design and Testing of Computers, pp. 26-38, Feb. 1990.

R. Fritzemeier, J. Soden, R. Treece, and C. Hawkins, “Increased Stuck-at Fault Coverage with Reduced IDDQ Test Sets,” Proc. of International Test Conference, 1990, pp. 427-433.

C. Thibeault and L. Boisvert, “Diagnosis Method Based on 1Iddq Probabilistic Signatures: Experimental Results,” Proc. of International Test Conference, 1998, pp. 1019-1026.

J. Liu, R. Makki, A. Kayssi, and S. Su, “An Economical Method For Detecting Disturb Faults in CMOS SRAMs,” IEEE Proceedings of the Economics of Design, Test and Manufacture, Oct. 1996, pp. 39-47.

Bram Kruseman, Peter Janssen, and Victor Zieren,“Transient Current Testing of 0.25 mm CMOS Devices,” Proc. of International Test Conference, 1999, pp. 47-56.

Wanli Jiang, Bapiraju Vinnakota, “Statistical Threshold Formulation For Dynamic Idd Test,” IEEE Proc. of International Test Conference, 1999, pp. 57-66.

Amy Germida, Zheng Yan, James F. Plusquellic, and Fidel Muradali, “Defect Detection Using Power Supply Transient Signal Analysis,” Proc. of International Test Conference, 1999, pp. 67-76.

Y. Min and Z. Li, “IDDT Testing versus IDDQ Testing,” Journal of Electronic Testing, Vol. 13, pp. 51-55, 1998.

J. Rius and J. Figueras, “Exploring the Combination of IDDQ and iDDT Testing: Energy Testing,” IEEE Proceedings of the European Design Automation Copnference, 1999, pp. 538-542.

R. Makki, S. Su, and T. Nagle, “Transient Power Supply Current Testing of Digital CMOS Circuits,” Proc. of International Test Conference, 1995, pp. 892-901.

P.E. Allen, CMOS Analog Circuit Design, Harcourt Brace Jovanovich, Inc. Orlando, Florida, 1987.

E. Vittoz and J. Fellrath, “CMOS Analog Integrated Circuits Based on Weak Inversion Operation,” IEEE Journal of Solid-State Circuits, Vol. SC-12, No. 3, pp. 231-244, 1977.

Rights and permissions

About this article

Cite this article

Liu, J., Makki, R.Z. & Kayssi, A. Dynamic Power Supply Current Testing of CMOS SRAMs. Journal of Electronic Testing 16, 499–511 (2000). https://doi.org/10.1023/A:1008324900917

Issue Date:

DOI: https://doi.org/10.1023/A:1008324900917