Abstract

A novel high-performance and miniaturized fin-shaped field effect transistor has been proposed which has been named as rectzoidal (rectz) because of its origin from the existing rectangular (rect) and trapezoidal (trap) structures. The rationale behind proposing this structure is to sustain the integration of millions of transistors on integrated circuits (ICs), further utilizing these scaled transistors in advanced processors of leading semiconductor industries. The work presented here is divided into two phases: first phase presents the proposed transistor design at 20 nm gate length and its comparative simulation analysis with the previous rect and trap transistor structures in terms of short channel effects and other analog and RF parameters like transconductance, output conductance, intrinsic gain, gate capacitance, unity gain frequency etc. using Cogenda three-dimensional Technology Computer-Aided Design (TCAD) tool. In the subsequent phase, i.e., optimization phase, artificial neural network was trained with design parameters of proposed structure and fitness function was formulated using weighted sum approach. Evolutionary and swarm-based optimization algorithms have been applied to obtain optimum design parameters of proposed transistor structure corresponding to minimum fitness function value. Results obtained through these optimizers are in good consistence with TCAD simulation results.

Similar content being viewed by others

References

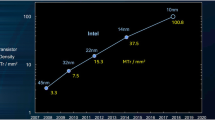

Schaller, R.R.: Moore’s law: past, present, and future. IEEE Spectr. 34, 53–59 (1997)

Tsuchiya, T.; Sato, Y.; Tomizawa, M.: Three mechanisms determining short-channel effects in fully-depleted SOI MOSFETs. IEEE Trans. Electron Dev. 45, 1116–1121 (1998)

Pierret, R.F.: Semiconductor Device Fundamentals. Pearson Education, Delhi, India (1996)

Chang, L.; Tang, S.; King, T.J.; Bokor, J.; Hu, C.: Gate length scaling and threshold voltage control of double-gate MOSFETs. In: International Electron Devices Meeting, pp. 719–722 (2000)

Chang, L.; Choi, Y.K.; Ha, D.; Ranade, P.; Xiong, S.; Bokor, J.; Hu, C.; King, T.J.: Extremely scaled silicon nano-CMOS devices. Proc. IEEE 91, 1860–73 (2003)

Ernst, T.; Cristoloveanu, S.; Ghibaudo, G.; et al.: Ultimately thin double-gate SOI MOSFETs. IEEE Trans. Electron Dev. 50, 830–838 (2003)

Hisamoto, D.; Lee, W.C.; Kedzierski, J.; et al.: FinFET-a self- aligned double-gate MOSFET scalable to 20 nm. IEEE Trans. Electron Dev. 47, 2320–25 (2000)

Kawa, J.: The Use of FinFETs in IP Design. Chip Design Magazine: Tools, Technologies and Methodologies (2013)

Islam, R.; Baten, M.Z.; Amin, E.M.; Khosru, Q.D.M.: On the distinction between triple gate (TG) and double gate (DG) SOI FinFETs: a proposal of critical top oxide thickness. In: IEEE International Conference on Electrical and Computer Engineering (ICECE), Dhaka, pp. 434–437 (2013)

Chandorkar, A.; Mande, S.; Iwai, H.: Estimation of process variation impact on DG-FinFET device performance using Plackett-Burman design of experiment method. In: 9th International Conference on Solid-State and Integrated-Circuit Technology, Beijing, pp. 215–218 (2008)

Sivasankaran, K.; Chitroju, T.R.K.; Reddy, K.S.A.; Subrahmanyam, M.S.; Harsha, M.V.S.; Mallik, P.S.: Effect of gate engineering in FinFET for RF applications. In: IEEE International Conference on Advances in Electrical Engineering (ICAEE), Vellore, pp. 1–6 (2014)

Clarke, P.: EE Times. Intel’s FinFETs are less fin and more triangle. http://www.eetimes.com/electronics-news/4373195/Intel-FinFETs-shape-revealed/ (2012). Accessed 25 Jan 2015

Fasarakis, N.; Karatsori, T.A.; Tsormpatzoglou, A.; et al.: Compact modeling of nanoscale trapezoidal FinFETs. IEEE Trans. Electron Dev. 61, 324–32 (2014)

Gaurav, A.; Gill, S.S.; Kaur, N.: Performance analysis of rectangular and trapezoidal TG bulk FinFETs for 20 nm gate length. In: Annual IEEE India Conference (INDICON), New Delhi, pp 1–5 (2015)

Gaynor, B.D.; Hassoun, S.: Fin shape impact on FinFET leakage with application to multithreshold and ultralow-leakage FinFET design. IEEE Trans. Electron Dev. 61, 2738–2744 (2014)

Nam, H.; Shin, C.: Impact of current flow shape in tapered (versus rectangular) FinFET on threshold voltage variation induced by work-function variation. IEEE Trans. Electron Dev. 61, 2007–2011 (2014)

Dubey, S.; Kondekar, P.N.: Fin shape dependent variability for strained SOI FinFETs. Microelectron. Eng. 162, 63–68 (2016)

Kurniawan, E.D.; Yang, H.; Lin, C.-C.; Wu, Y.-C.: Effect of fin shape of tapered FinFETs on the device performance in 5-nm node CMOS technology. Microelectron. Reliab. (2017) (in press)

Yu, Z.; Chang, S.; He, J.; Huang, Q.; Yu, Z.; Chang, S.; Wang, H.; Wang, H.; et al.: Effects of fin shape on sub-10 nm FinFETs. J. Comput. Electron. 14, 515–523 (2015)

TSMC. Leading Edge Technology. http://www.tsmc.com/english/dedicatedFoundry/technology/16nm.htm. Accessed 1 Mar 2017

Semiconductor Engineering. IBM, Intel and TSMC Roll out FinFETs. http://semiengineering.com/ibm-intel-and-tsmc-roll-out-finfets. Accessed 1 Mar 2017

Global Foundries. 7nm FinFET. https://www.globalfoundries.com/technology-solutions/cmos/performance. Accessed 1 Mar 2017

Andrade, M.G.C.; de Martino, J.A.; Aoulaiche, M.; Collaert, N.; Simoen, E.; Claeys, C.: Behavior of triple-gate bulk FinFETs with and without DTMOS operation. Solid State Electron. 71, 63–68 (2012)

Mohapatra, S.K.; Pradhan, K.P.; Singh, D.; Sahu, P.K.: The role of geometry parameters and fin aspect ratio of sub-20 nm SOI-FinFET: an analysis towards analog and RF circuit design. IEEE Trans. Nanotechnol. 14, 546–554 (2015)

Pradhan, K.P.; Priyanka,; Sahu, P.K.: Temperature dependency of double material gate oxide (DMGO) symmetric dual-k spacer (SDS) wavy FinFET. Superlattices Microstruct. 89, 355–361 (2016)

Pradhan, K.P.; Priyanka,; Mallikarjunarao,; Sahu, P.K.: Exploration of symmetric high-k spacer (SHS) hybrid FinFET for high performance application. Superlattices Microstruct. 90, 191–197 (2016)

Pradhan, K.P.; Sahu, K.P.: Benefits of asymmetric underlap dual-k spacer hybrid fin field-effect transistor over bulk fin field-effect transistor. IET Circuits Devices Syst. 10, 441–447 (2016)

Pradhan, K.P.; Mohapatra, S.K.; Sahu, P.K.; Behera, D.K.: Impact of high-k gate dielectric on analog and RF performance of nanoscale DG-MOSFET. Microelectron. J. 45, 144–151 (2014)

Grewal, N.S.; Rattan, M.; Patterh, M.S.: A linear antenna array failure correction with null steering using firefly algorithm. Def. Sci. J. 64, 136–142 (2014)

Kaur, R.; Rattan, M.: Optimization of the return loss of differentially fed microstrip patch antenna using ANN and firefly algorithm. Wireless Pers. Commun. 80, 1547–1556 (2015)

Dhaliwal, B.S.; Pattnaik, S.S.: Performance comparison of bio-inspired optimization algorithms for Sierpinski gasket fractal antenna design. Neural Comput. Appl. 27, 585–592 (2016)

Gaurav, A.; Gill, S.S.; Kaur, N.; Rattan, M.: Density gradient quantum corrections based performance optimization of triangular TG bulk FinFETs using ANN and GA. In: 20th International Symposium VLSI Design and Test (VDAT), Guwahati, pp. 1–5 (2016)

Kaur, J.; Gill, S.S.; Kaur, N.: Optimization of CMOS repeater driven interconnect RC line using genetic algorithm. J. Shanghai Univ. Nat. Sci. 22, 167–172 (2017)

Xie, X-F.; Zhang, W-J.; Bi, D-C.: Optimizing semiconductor devices by self-organizing particle swarm. In: Congress on Evolutionary Computation (CEC), Oregon, pp. 2017–2022 (2004)

Bendib, T.; Djeffal, F.: Electrical performance optimization of nanoscale double-gate MOSFETs using multiobjective genetic algorithms. IEEE Trans. Electron Dev. 58, 3743–3750 (2011)

Bendib, T.; Djeffal, F.; Meguellati, M.: An optimized junctionless GAA MOSFET design based on multi-objective computation for high-performance ultra-low power devices. J. Semicond. 35, 074002 (2014)

Bendib, T.; Djeffal, F.; Bentrcia, T.; Arar, D.; Lakhdar, N.: Multi-objective genetic algorithms based approach to optimize the small signal parameters of gate stack double gate MOSFET. In: Proceedings of World Congress on Engineering (WCE), London (2012)

Holland, J.H.: Adaptation in Natural and Artificial Systems: An Introductory Analysis with Applications to Biology, Control and Artificial Intelligence. MIT Press, Cambridge (1992)

Kennedy, J.; Eberhart, R.: Particle swarm optimization. In: Proceedings of International Conference on Neural Networks, Perth, WA, vol. 4, pp. 1942–1948 (1995)

Yang, X.-S.: Firefly algorithms for multimodal optimization. In: Watanabe, O., Zeugmann, T. (eds.) Stochastic Algorithms: Foundations and Applications (SAGA), pp. 169–178. Springer, Berlin (2009)

Cogenda User’s Guides. http://www.cogenda.com/article/downloads. Accessed 3 Aug 2015

Taur, Y.: CMOS design near the limit of scaling. IBM J. Res. Dev. 46, 213–222 (2002)

Lombardi, C.; Manzini, S.; Saporito, A.; Vanzi, M.: A physically based mobility model for numerical simulation of nonplanar devices. IEEE Trans. Comput. Aided Des. Integr. Circuits Syst. 7, 1164–1171 (1988)

3D FinFET simulation with Density Gradient (DG) quantum correction model. http://www.cogenda.com/article/examples#FinFET-dg. Accessed 15 Nov 2016

Li, Y.; Hwang, C.-H.: Nanoscale transistors. In: Wiederrecht, G.P. (ed.) Handbook of Nanoscale Optics and Electronics, pp. 167–238. Elsevier, The Netherlands (2010)

Abraham, A.: Artificial neural networks. In: Sydenham, P.H., Thorn, R. (eds.) Handbook of Measuring System Design. Wiley, Hoboken (2005)

Mathworks\({}^{\textregistered }\). Neural Network Toolbox. https://in.mathworks.com/help/nnet/getting-started-with-neural-network-toolbox.html

Cheung, N.J.; Ding, X.-M.; Shen, H.-B.: Adaptive firefly algorithm: parameter analysis and its application. PLoS ONE 9(1–12), e112634 (2014)

Author information

Authors and Affiliations

Corresponding author

Rights and permissions

About this article

Cite this article

Kaur, N., Rattan, M. & Gill, S.S. Design and Optimization of Novel Shaped FinFET. Arab J Sci Eng 44, 3101–3116 (2019). https://doi.org/10.1007/s13369-018-3428-3

Received:

Accepted:

Published:

Issue Date:

DOI: https://doi.org/10.1007/s13369-018-3428-3