Abstract

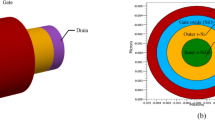

In this work, we have proposed and analysed the Triple Material Dual Gate Cylindrical Nanowire (TMDG CNW) device structure at the 10 nm technology node for improved device performance over conventional nanowire. The proposed structure was validated using the Sentaurus TCAD tool. By incorporating three materials with different work functions as gate electrodes, using a dielectric stack and halo doping in the channel region, the device performance has been enhanced and immunity to short channel effects (SCE) has been improved further. An additional gate-coaxial inner gate other than the outer gate has been added to the TMDG CNW structure, which further improves the device performance. The proposed device has higher drain current, good immunity to SCE and process variations, better gate control over the channel, and overall better device performance. This gate/channel engineered nanowire FET with an additional coaxial inner gate has been reported for the first time.

Similar content being viewed by others

Data Availability

Not Applicable.

References

Kumar A, Saini S, Gupta A, Gupta N, Tripathi MM, Chaujar R (2020) Sub-10 nm high-k dielectric SOI-FinFET for High Performance low power applications. International Conference on Signal Processing and Communication: 310–314

Sreenivasulu B, Narendar V (2021) Performance improvement of spacer engineered n-type SOI FinFET at 3- nm gate length. International Journal of Electronic Communication 137:153803

Munjal S, Prakash NR, Kaur J (2021) Evolution of junctionless field effect transistors in semiconductor industry: a review. International Journal of Innov Sci Eng Technol 8(8):94–103

Das UK, Bhattacharyya TK (2020) Opportunities in device scaling for 3-nm node and beyond: FinFET versus GAA-FET versus UFET. IEEE Tran Electron Devices 67(6):2633–2638

Mohan C, Choudhary S, Prasad B (2017) Gate all around FET: an alternative of FinFET for future technology nodes. Int J Adv Res Sci Eng 6(7):561–569

Nagy D, Indalecio G, Garcia Loureiro NJ (2018) FinFET versus gate-all-around nanowire FET: performance, scaling, and variability. J Electron Devices Soc 6:332–340

Kumar S, Goel E, Singh K (2017) 2-D analytical modeling of the electrical characteristics of dual-material double-gate TFETs With a SiO2/HfO2 stacked gate-oxide structure. IEEE Trans Electron Devices 64(3):960–968

Li Y, Chen H-M, Yu S-M, Hwang J-R, Yang F-L (2008) Strained CMOS Devices with Shallow-Trench-Isolation Stress Buffer Layers. IEEE Trans Electron Devices 55(4):1085–1089

Hui-Wen Cheng, C. -H. Hwang and Y. Li (2009) Propagation delay dependence on channel fins and geometry aspect ratio of 16-nm multi-gate MOSFET inverter. 1st Asia Symposium on Quality Electronic Design:122–125

Vallabhuni RR, Yamini G, Vinitha T (2020) Performance analysis:D-Latch modules designed using 18nm FinFET Technology. International Conference on Smart Electronics and Communication September: 1169–1174

Kajal, Sharma VK (2021) Design and Simulation of FinFET Circuits at Different Technologies. International Conference on Inventive Computational Technologies: 1–6

Zhang S (2020) Review of Modern Field Effect Transistor Technologies for Scaling. 2nd International Conference on Electronic Engineering and Informatics 1617:012054

Uddin M, Athiya M, Masud NLA, Chowdhury H (2021) FinFET based SRAMs in sub-10nm domain. Microelectron J 114(5):105116

Ratnaa VR, Sarithab M, Saipreethi V, Vijayb PC, Shaker MD, Sadullae S (2020) High speed energy efficient multiplier using 20nm FinFET technology. International Conference on IoT based Control Network Intelligent Systems

Gadarapulla R, Sriadibhatla S (2021) Tunnel FET based SRAM cells – a comparative review. Int Conf Microelectron Devices Circuits System 1392:217–228

Kim SD, Guillom M (2015) Performance tradeoffs in FinFET and gate all around device architectures for 7 nm node and beyond. IEEE SOI-3D-Subthreshold Microelectronics Technology Unified Conference: 1–3

Mohan C (2017) Gate all around FET: an alternative of FinFET for future technology nodes. Int J Adv Res Sci Technol 6(7):561–569

Liu TY, Pan FM (2015) Characteristics of gate-all-around Junctionless polysilicon nanowire transistors with twin 20-nm gates. J Electron Dev Soc 3(5):405–409

Zhuge J, Wang R, Huang R, Tian Y, Zhang L, Kim D-W, Park D, Wang YY (2009) High-performance silicon nanowire gate-all-around nMOSFETs fabricated on a bulk substrate using CMOS compatible process. IEEE Electron Device Lett 31(12):57–60

Huang R, Wang R, Zhuge J, Liu C, Yu T, Zhang L, Huang X, Zou J, Liu Y, Fan J, Wang Y (2011) Characterization and Analysis of Gate-All-Around Si Nanowire Transistors for Extreme Scaling. IEEE Custom Integrated Circuit’s Conference: 1–8

Moezi N, Karbalaei M (2020) Predictive physics based simulation of Nano scale gate-all-around field effect transistor under the influence of high-k gate dielectrics. J Nanostruct 10(4):736–743

Zhang C, Li X (2016) III–V nanowire transistors for low-power logic applications: a review and outlook. IEEE Trans Electron Devices 63(1):223–234

Bufler FM, Ritzenthaler R, Mertens H, Eneman G, Mocuta A, Horiguchi N (2018) Performance comparison of n– type Si nanowires, Nanosheets, and FinFETs by MC device simulation. IEEE Electron Device Lett 39(11):1628–1631

Pindoo IA, Sinha SK, Chander S (2021) Performance analysis of heterojunction tunnel FET device with variable temperature. Applied Physics. 10. 1007/ s00339- 021- 04891–1

Vanlalawmpuia K, Bhowmick B (2021) Optimization of a heterostructure vertical tunnel FET for enhanced electrical performance and effects of temperature variation on RF/linearity parameters. SILICON 13:155–166

Kumar S, Goel E, Singh K, Singh B, Kumar M (2016) A Compact 2-D Analytical Model for Electrical Characteristics of Double-Gate Tunnel Field-Effect Transistors With a SiO2/High- $k$ Stacked Gate-Oxide Structure. IEEE Trans Electron Devices 63(8):3291–3299

Liu C (2020) New Challenges of Design for Reliability in Advanced Technology Node. IEEE Electron Devices Technology & Manufacturing Conference: 1–4

Razavieh A, Zeitzoff P, Nowak EJ (2019) Challenges and limitations of CMOS scaling for FinFET and beyond architectures. IEEE Trans Nanotechnol 18:999–1004

Vashishtha V, Clark LT (2021) Comparing bulk-Si FinFET and gate-all-around FETs for the 5 nm technology node. Microelectronics J 107:104942

Kang Y, Liang G, Gong X (2021) Ge0.95Sn0.05 gate-all-around p-channel metal-oxide-semiconductor field-effect transistors with Sub-3 nm nanowire width. Nano Lett 21(13):5555–5563

Song T (2022) A 3-nm gate-all-around SRAM featuring an adaptive dual-Bitline and an adaptive cell-power assist circuit. IEEE J Solid State Circuits 57(1):236–244

Li C, Liu F, Han R, Zhuang Y (2021) A vertically stacked Nanosheet gate-all-around FET for biosensing application. IEEE Access 9:63602–63610

Seifollahi S, Ziabari SAS, Sarkaleh AK (2021) A design of nanoscale double-gate FET based ring oscillator with improved oscillation frequency using device engineering. Int J Electron Commun 134:153701

Rajveer K, Balwinder S (2020) Comparative Study of Single and Double gate ALL Around Cylindrical FET Structures for High –K Dielectric Materials. Trans Electr Electron Mater 22(4):509–514

Kosmani NF, Hamid FA, Razali MA (2020) Effects of high-k dielectric materials on electrical performance of double gate and gate-all-around MOSFET. Int J Integr Eng 12(2):81–88

Lee BH, Kang L, Nieh R, Qi WJ, Lee JC (2000) Thermal stability and electrical characteristics of ultrathin hafnium oxide gate dielectric reoxidized with rapid thermal annealing. Appl Phys Lett 76(14):1926–1928

Nirmal D, Vijayakumar P, Thomas DM, Jebalin BK, N. Mohan kumar, (2013) Subthreshold performance of gate engineered FinFET devices and circuit with high-k dielectrics. Microelectron Reliab 53(3):499–504

Charles JP, Nirmal D, Prajoon P, Ajayan J (2016) Implementation of nanoscale circuits using dual metal gate engineered nanowire MOSFET with high-k dielectrics for low power application. Physica E 83:95–100

Acknowledgements

Authors are thankful to Electronics and Communication Department, JIIT for providing Sentaurus TCAD Tool for simulation work.

Author information

Authors and Affiliations

Contributions

Work has been done by Mr. Mandeep Singh Narula under the supervision of Dr. Archana Pandey.

Corresponding author

Ethics declarations

Ethical approval

Not Applicable.

Competing Interests

The authors declare no competing interests.

Financial Interests

The authors have no relevant financial or non-financial interests to disclose.

The contents of this manuscript are not under consideration for publication anywhere else.

Consent to participate

Not Applicable.

Consent for publication

Not Applicable.

Conflict of Interest

The author has no conflicts of interest relevant to the content of this manuscript.

Additional information

Publisher's Note

Springer Nature remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

Rights and permissions

Springer Nature or its licensor (e.g. a society or other partner) holds exclusive rights to this article under a publishing agreement with the author(s) or other rightsholder(s); author self-archiving of the accepted manuscript version of this article is solely governed by the terms of such publishing agreement and applicable law.

About this article

Cite this article

Narula, M.S., Pandey, A. Gate Engineered Silicon Nanowire FET with Coaxial Inner Gate for Enhanced Performance. Silicon 15, 4217–4227 (2023). https://doi.org/10.1007/s12633-023-02340-7

Received:

Accepted:

Published:

Issue Date:

DOI: https://doi.org/10.1007/s12633-023-02340-7