Abstract

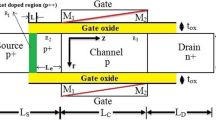

In this paper, a charge plasma-based phosphorene double-gate tunnel FET (CP-BPDGTFET) is investigated. A hybrid simulation technique involving both atomistic and technology computer-aided design (TCAD) has been used to simulate the device characteristics. First, the density functional theory has been used to simulate phosphorene electrical characteristics (monolayer to few-layer, including armchair and zigzag directions). The parameters such as band gap and effective mass obtained using an atomistic simulator tool are exported into Sentaurus TCAD to simulate the device characteristics. The drain current characteristics are calibrated for conventional double gate phosphorene tunnel FET with non-equilibrium Green's function results. The DC characteristics of the proposed device are studied. The device performance is analysed by varying the device parameters such as gate length (Lg), spacer length (Ls), and gate workfunction (ϕm). Based on the study, an optimised device is designed, and its characteristics are obtained. The optimised device offers an on-current value of 405 µA/µm, SS = 79 mV/dec, Ion/Ioff = 1.13 × 106 for 30 nm gate length. It establishes that CP-BPDGTFET is a suitable candidate for energy-efficient circuit applications.

source to channel (arrow mark) are shown. (b) Shows carrier density for off-state (dotted line) and on state (solid line) (blue-electron/red-hole). It is found that the electron density in the channel dominates in both states. Energy bands and electron density are taken at 0.1 nm from the surface (Color figure online).

Similar content being viewed by others

References

F. Schwierz, J. Pezoldt, and R. Granzner, Nanoscale 7, 8261 (2015).

S. Das, M. Demarteau, and A. Roelofs, ACS Nano 8, 11730 (2014).

H. Qu, S. Guo, W. Zhou, and S. Zhang, IEEE Electron Device Lett. 42, 66 (2021).

X.B. Li, P. Guo, T.F. Cao, H. Liu, W.M. Lau, and L.M. Liu, Sci. Rep. 5, 1 (2015).

A. Castellanos-Gomez, L. Vicarelli, E. Prada, J. O. Island, K. L. Narasimha-Acharya, S. I. Blanter, D. J. Groenendijk, M. Buscema, G. A. Steele, J. V. Alvarez, H. W. Zandbergen, J. J. Palacios, and H. S. J. Van Der Zant, 2D Mater. 1 (2014).

X. Ling, H. Wang, S. Huang, F. Xia, and M.S. Dresselhaus, Proc. Natl. Acad. Sci. U. S. A. 112, 4523 (2015).

A. Goswami, and M.B. Gawande, Front. Chem. Sci. Eng. 13, 296 (2019).

F. Xia, H. Wang, J.C.M. Hwang, A.H.C. Neto, and L. Yang, Nat. Rev. Phys. 1, 306 (2019).

A. Carvalho, M. Wang, X. Zhu, A.S. Rodin, H. Su, and A.H. Castro-Neto, Nat. Rev. Mater. 1, 16031 (2016).

X. Feng, L. Wang, X. Huang, L. Chen, and K.-W. Ang, IEEE Trans. Electron Devices 1 (2018).

H. Wang, X. Wang, F. Xia, L. Wang, H. Jiang, Q. Xia, M.L. Chin, M. Dubey, and S.J. Han, Nano Lett. 14, 6424 (2014).

M. Navid, A. Aadit, S. N. Juthi, and S. G. Kirtania, 7 (2017).

F.W. Chen, H. Ilatikhameneh, T.A. Ameen, G. Klimeck, and R. Rahman, IEEE Electron Device Lett. 38, 130 (2017).

S. Kim, G. Myeong, W. Shin, H. Lim, B. Kim, T. Jin, S. Chang, K. Watanabe, T. Taniguchi, and S. Cho, Nat. Nanotechnol. 15, 203 (2020).

A. Szabo, S.J. Koester, and M. Luisier, IEEE Electron Device Lett. 36, 514 (2015).

P.K. Dubey, and B.K. Kaushik, IEEE Trans. Electron Devices 66, 2837 (2019).

R.J.E. Hueting, B. Rajasekharan, C. Salm, and J. Schmitz, IEEE Electron Device Lett. 29, 1367 (2008).

B. Rajasekharan, R.J.E. Hueting, C. Salm, T. Van Hemert, R.A.M. Wolters, and J. Schmitz, IEEE Electron Device Lett. 31, 528 (2010).

A. Pon, A. Bhattacharyya, B. Padmanaban, and R. Ramesh, J. Comput. Electron. (2019).

W. Wan, H. Lou, Y. Xiao, and X. Lin, IEEE Trans. Electron Devices 65, 1873 (2018).

D. Soni, D. Sharma, S. Yadav, M. Aslam, and N. Sharma, Superlattices Microstruct. 113, 97 (2018).

D. Singh, S. Pandey, K. Nigam, D. Sharma, D.S. Yadav, and P. Kondekar, IEEE Trans. Electron Devices 64, 271 (2017).

M.J. Kumar, and S. Janardhanan, IEEE Trans. Electron Devices 60, 3285 (2013).

Y. Pan, Y. Dan, Y. Wang, M. Ye, H. Zhang, R. Quhe, X. Zhang, J. Li, W. Guo, L. Yang, J. Lu, and A.C.S. Appl, Mater. Interfaces 9, 12694 (2017).

A. Blom, U. M. Pozzoni, T. Markussen, and K. Stokbro, Int. Conf. Simul. Semicond. Process. Devices, SISPAD 2015-Octob, 52 (2015).

Á. Szabó, C. Klinkert, D. Campi, C. Stieger, N. Marzari, and M. Luisier, IEEE Trans. Electron Devices 65, 4180 (2018).

C. Nanmeni Bondja, Z. Geng, R. Granzner, J. Pezoldt, and F. Schwierz, Electronics 5, 3 (2016).

C. Maneux, S. Fregonese, T. Zimmer, S. Retailleau, H.N. Nguyen, D. Querlioz, A. Bournel, P. Dollfus, F. Triozon, Y.M. Niquet, and S. Roche, Solid State Electron. 89, 26 (2013).

S. Carapezzi, S. Eberle, S. Reggiani, E. Gnani, C. Roman, C. Hierold, and A. Gnudi, Solid-State Device Res. 1, 3 (2018).

Y. Du, H. Liu, Y. Deng, and P.D. Ye, ACS Nano 8, 10035 (2014).

S. Luo, K.T. Lam, B. Wang, C.H. Hsu, W. Huang, L.Z. Yao, A. Bansil, H. Lin, and G. Liang, IEEE Trans. Electron Devices 64, 579 (2017).

G. Mirabelli, F. Gity, S. Monaghan, P. K. Hurley, and R. Duffy, Eur. Solid-State Device Res. Conf. 288 (2017).

G. Shine, and K.C. Saraswat, IEEE Trans. Electron Devices 64, 3768 (2017).

A. Pon, K.S.V.P. Tulasi, R. Ramesh, and A.E.U. Int, J. Electron. Commun. 102, 1 (2019).

A. Pon, S. Carmel, A. Bhattacharyya, and R. Rathinam, in 2019 IEEE International Conference on Electron Devices Solid-State Circuits, EDSSC 2019 (Institute of Electrical and Electronics Engineers (IEEE), 2019), pp. 1–3.

R. Rathinam, A. Pon, S. Carmel, A. Bhattacharyya, and I.E.T. Circuits, Devices Syst. 14, 1167 (2020).

J. Tao, J. Chem. Phys. 116, 2335 (2002).

H. Liu, A.T. Neal, Z. Zhu, Z. Luo, X. Xu, D. Tománek, and P.D. Ye, ACS Nano 8, 4033 (2014).

J. Qiao, X. Kong, Z.X. Hu, F. Yang, and W. Ji, Nat. Commun. 5, 1 (2014).

A. Ojha, and N.R. Mohapatra, Solid. State. Electron. 160, 107625 (2019).

N. Ma, and D. Jena, Device Res. Conf. Conf. Dig. DRC 132102, 103 (2013).

J. Hur, W.J. Jeong, M. Shin, and Y.K. Choi, IEEE Trans. Electron Devices 64, 5223 (2017).

J. Madan, R. Pandey, R. Sharma, and R. Chaujar, Appl. Phys. A 125, 600 (2019).

T.A. Ameen, H. Ilatikhameneh, G. Klimeck, and R. Rahman, Sci. Rep. 6, 1 (2016).

H. Ilatikhameneh, T. Ameen, B. Novakovic, Y. Tan, G. Klimeck, and R. Rahman, Sci. Rep. 6, 1 (2016).

T. Agarwal, I. Radu, P. Raghavan, G. Fiori, A. Thean, M. Heyns, and W. Dehaene, Eur. Solid-State Circuits Conf. 2016-Octob, 55 (2016).

Acknowledgment

The authors would like to gratefully acknowledge DST Extra Mural Research funding Scheme (SERB/F/4240/2016-2017).

Author information

Authors and Affiliations

Corresponding author

Ethics declarations

Conflict of interest

The authors declare that they have no conflict of interest.

Additional information

Publisher's Note

Springer Nature remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

Rights and permissions

About this article

Cite this article

Pon, A., Bhattacharyya, A. & Ramesh, R. Charge Plasma-Based Phosphorene Tunnel FET Using a Hybrid Computational Method. J. Electron. Mater. 50, 3624–3633 (2021). https://doi.org/10.1007/s11664-021-08882-z

Received:

Accepted:

Published:

Issue Date:

DOI: https://doi.org/10.1007/s11664-021-08882-z