Abstract

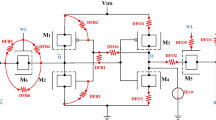

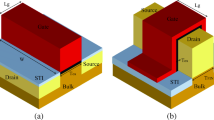

In recent years, FinFET-based Static Random Access Memories (SRAMs) have become a viable solution to provide the storage of big data volume in Systems-on-Chip (SoCs) as well as to assure high performance deep-scaled devices. As consequence, FinFET-based SRAMs are an extremely viable solution to guarantee the high-performance requirements of deep-scaled devices. However, FinFET-based SRAMs can also be affected by resistive defects that may lead to dynamic faults, which are considered one of the most important causes of manufacturing test escape in deep-submicron technologies. Hence, this paper proposes to evaluate the impact of temperature on the dynamic faulty behaviour of 20 nm FinFET-based SRAM cells affected by weak resistive defects. In more details, the critical resistances and the number of consecutive operations necessary to sensitize faults at the logic level are investigated. Additionally, the concept of Dynamic Behaviour Window (DBW) is defined. Results showed that temperature plays a major part in the sensitization of dynamic faults. Thus, the occurrence of dynamic faults has been mapped combining temperature as well as defect size, and the DBW has been defined considering resistive defects. The proposed evaluation helps to understand the behaviour of dynamic faults in memory cells even better and therefore can be used to improve the test procedures for deep-scaled FinFET memory devices. The proposed analysis has been performed using HSPICE simulations adopting a 20 nm Predictive Technology Model (PTM) of multi-gate transistors based on bulk FinFET.

Similar content being viewed by others

References

Adams RD, Cooley ES (1996) Analysis of a deceptive destructive read memory fault model and recommended testing. In: Proc. IEEE North Atlantic Test Workshop (NATW)

Bhattacharya D, Jha NK (2014) FinFETs: from devices to architectures. Adv Electron 2014:1–21. https://doi.org/10.1155/2014/365689

Borri S, Hage-Hassan M, Girard P, Pravossoudovitch S, Virazel A (n.d.) Defect-oriented dynamic fault models for embedded-SRAMs. In: Eighth IEEE Eur Test Work 2003. Proceedings IEEE Comput Soc, pp 23–28. https://doi.org/10.1109/ETW.2003.1231664

Bosio A, Dilillo L, Girard P, Pravossoudovitch S, Virazel A (2012) Advanced test methods for SRAMs, in: 2012 IEEE 30th VLSI Test Symp. IEEE:300–301. https://doi.org/10.1109/VTS.2012.6231070

Burnett D, Parihar S, Ramamurthy H, Balasubramanian S (2014) FinFET SRAM design challenges. In: 2014 IEEE Int. Conf. IC des. Technol. IEEE, pp 1–4. https://doi.org/10.1109/ICICDT.2014.6838606

Colinge JP (2008) FinFETs and other multi-gate transistors. Springer US, Boston, MA. https://doi.org/10.1007/978-0-387-71752-4

Copetti TS, Balen TR, Medeiros GC, Poehls LMB (2017) Analyzing the behavior of FinFET SRAMs with resistive defects. In: 2017 IFIP/IEEE Int. Conf. Very large scale Integr. IEEE, pp 1–6. https://doi.org/10.1109/VLSI-SoC.2017.8203483

Deshmukh R, Khanzode A, Kakde S, Shah N (2015) Compairing FinFETs: SOI Vs Bulk: Process variability, process cost, and device performance. In: Proc. Int. Conf. Comput. Commun. Control, IEEE, pp 1–4. https://doi.org/10.1109/IC4.2015.7375645

Dilillo L, Girard P, Pravossoudovitch S, Virazel A, Borri S, Hage-Hassan M (2004) Resistive-open defects in embedded-SRAM Core cells: analysis and march test solution, in: 13th Asian test Symp. IEEE:266–271. https://doi.org/10.1109/ATS.2004.75

Dilillo L, Girard P, Pravossoudovitch S, Virazel A, Borri S, Hage-Hassan M (n.d.) Dynamic read destructive fault in embedded-SRAMs: analysis and march test solution. In: Proceedings Ninth IEEE Eur Test Symp 2004. ETS 2004. IEEE, pp 140–145. https://doi.org/10.1109/ETSYM.2004.1347645

Fonseca RA, Dilillo L, Bosio A, Girard P, Pravossoudovitch S, Virazel A, Badereddine N (2010) Analysis of resistive-bridging defects in SRAM core-cells: a comparative study from 90nm down to 40nm technology nodes. In: 2010 15th IEEE Eur. Test Symp. IEEE, pp 132–137. https://doi.org/10.1109/ETSYM.2010.5512768

Hamdioui S, Al-Ars Z, van de Goor AJ (2002) Testing Static and Dynamic Faults in Random Access Memories. In: Proc. 20th IEEE VLSI Test Symp. (VTS 2002). IEEE Comput. Soc:395–400. https://doi.org/10.1109/VTS.2002.1011170

Harutyunyan G, Shoukourian S, Vardanian V, Zorian Y (2013) Impact of process variations on read failures in SRAMs. In: East-west des. Test Symp. (EWDTS 2013). IEEE, pp 1–4. https://doi.org/10.1109/EWDTS.2013.6673115

Heinig A, Dietrich M, Herkersdorf A, Miller F, Wild T, Hahn K, Grunewald A, Bruck R, Krohnert S, Reisinger J (2014) System integration -The bridge between More than Moore and More Moore, in: Proc. Des. Autom. Test Eur. Conf. Exhib. (DATE), pp 1–9. https://doi.org/10.7873/DATE.2014.145

Huang XHX, Lee W-CLW-C, Kuo CKC, Hisamoto D, Chang LCL, Kedzierski J, Anderson E, Takeuchi H, Choi Y-KCY-K, Asano K, Subramanian V, King T-JKT-J, Bokor J, Hu CHC (1999) Sub 50-nm FinFET: PMOS. Int Electron Devices Meet:67–70. https://doi.org/10.1109/IEDM.1999.823848

M. R. Jan, C. Anantha, N. Borivoje. Digital integrated circuits--a design perspective (2003)

Medeiros G, Brum E, Poehls LB, Copetti T, Balen T (2018) Influence of temperature on dynamic fault behavior due to resistive defects in FinFET-based SRAMs. In: 2018 IEEE 19th Latin-American test Symp. IEEE, pp 1–6. https://doi.org/10.1109/LATW.2018.8349697

Montañés RR (2002) Resistance characterization for weak open defects. IEEE Des Test Comput 19:18–26. https://doi.org/10.1109/MDT.2002.1033788

Nanoscale Integration and Modeling (NIMO), Predictive Technology Model (PTM), (2012)

Needham W, Prunty C, Yeoh EH (n.d.) High volume microprocessor test escapes , an analysis of defects. MIC:25–34

Roy K, Mukhopadhyay S, Mahmoodi-Meimand H (2003) Leakage current mechanisms and leakage reduction techniques in deep-submicrometer CMOS circuits. Proc IEEE 91:305–327. https://doi.org/10.1109/JPROC.2002.808156

Roy K, Jung B, Peroulis D, Raghunathan A (2016) Integrated Systems in the More-Than-Moore era: designing low-cost energy-efficient systems using heterogeneous components. IEEE Des Test 33:56–65. https://doi.org/10.1109/MDT.2011.49

Simsir MO, Bhoj A, Jha NK (2010) Fault modeling for FinFET circuits. In: 2010 IEEE/ACM Int. Symp. Nanoscale Archit. IEEE, pp 41–46. https://doi.org/10.1109/NANOARCH.2010.5510927

Tang SH, Chang L, Lindert N, Choi Y-K, Lee W-C, Huang X, Subramanian V, Bokor J, King T-J, Hu C (2001) FinFET - a quasi-planar double-gate MOSFET, in: Digest of Papers of IEEE Int. Solid-State Circuits Conf., ISSCC, pp 118–119. https://doi.org/10.1109/ISSCC.2001.912568

van de Goor AJ, Al-Ars Z (2000) Functional memory faults: a formal notation and a taxonomy, Proc. 18th IEEE VLSI Test Symp., pp 281–289. https://doi.org/10.1109/VTEST.2000.843856

van de Goor AJ, Gaydadjiev GN, Mikitjuk VG, Yarmolik VN (1996) March LR: a test for realistic linked faults. Proc. 14th VLSI Test Symp., pp 272–280. https://doi.org/10.1109/VTEST.1996.510868

Acknowledgments

This study was financed in part by the Coordenação de Aperfeiçoamento de Pessoal de Nivel Superior – Brasil (CAPES) - Finance code 001.

Author information

Authors and Affiliations

Corresponding author

Additional information

Responsible Editor: P. Girard

Publisher’s Note

Springer Nature remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

Rights and permissions

About this article

Cite this article

Medeiros, G.C., Brum, E., Poehls, L.B. et al. Evaluating the Impact of Temperature on Dynamic Fault Behaviour of FinFET-Based SRAMs with Resistive Defects. J Electron Test 35, 191–200 (2019). https://doi.org/10.1007/s10836-019-05784-1

Received:

Accepted:

Published:

Issue Date:

DOI: https://doi.org/10.1007/s10836-019-05784-1