Abstract

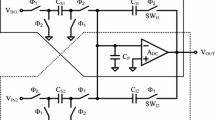

This paper proposes a circuit-level model of an inverter-based switched-capacitor (SC) integrator involved in a previously published incremental sigma-delta analog-to-digital converter (I\(\Sigma {\Delta }\) ADC) to explain the ADC resolution degradation observed in the post-layout simulation. A fine analysis of post-layout signals led to a new model of the integrator with parasitic capacitors. Then the model has been included in the I\(\Sigma {\Delta }\) ADC model, which has been simulated with Matlab. To get detailed results and be able to handle comparisons, various calibration techniques have been applied to the I\(\Sigma {\Delta }\) ADC outputs coming from post-layout simulation and from the new model so that a better resolution is achieved. The results show a good likeness of the error shapes and magnitudes for the new model compared to post-layout simulations. We deduce that the proposed model is a good representation of the degradation phenomena, this with a high level of confidence.

Similar content being viewed by others

References

Markus, J., Deval, P., Quiquempoix, V., Silva, J., & Temes, G. C. (2006). Incremental delta-sigma structures for DC measurement: An overview. IEEE Custom Integrated Circuits Conference, 2006, 41–48.

Chae, Y., & Han, G. (2007). A low power sigma-delta modulator using class-C inverter. In 2007 IEEE symposium on VLSI circuits (pp. 240–241). IEEE.

Wang, B., Zhang, M., Cheng, X., Feng, Q., & Zeng, X. (2013). A 1.8-v 14-bit inverter-based incremental \(\sigma \delta\) ADC for CMOS image sensor. In 2013 IEEE 10th international conference on ASIC (pp. 1–4). IEEE.

Torkzadeh, P., Tajalli, A., & Atarodi, M. (2005). Modeling of non-ideal switch-capacitor integrator and its effect on baseband sigma-delta modulator stability and output dynamic range. In 2005 international conference on microelectronics. IEEE.

Georgiev, V., & Stantchev, K. (1986). Adequate SC model of op-amp with finite DC gain and bandwidth suitable for two-op-amp SC biquad analysis. Electronics Letters, 22(19), 996–997.

Wolski, W. J. (1988). Influence of op-amp nonidealities and switch-on resistances on SC integrator. In 1998 IEEE international symposium on circuits and systems (pp. 1995–1998). IEEE.

Leuciuc, A., & Mitrea, C. (2000). On the effect of op-amp finite gain in delta-sigma modulators. In 2000 IEEE international symposium on circuits and systems. Emerging technologies for the 21st century. Proceedings (IEEE Cat No. 00CH36353) (Vol. 3, pp. 754–757). IEEE.

Zare-Hoseini, H. & Kale, I. (2005). On the effects of finite and nonlinear DC-gain of the amplifiers in switched-capacitor/spl Delta//spl Sigma/modulators. In 2005 IEEE international symposium on circuits and systems (pp. 2547–2550). IEEE.

Bisiaux, P., Lelandais-Perrault, C., Kolar, A., Benabes, P., & Dos Santos, F. V. (2016). A new two-step \(\sigma \delta\) architecture column-parallel adc for cmos image sensor. In Proceedings of the 29th symposium on integrated circuits and systems design: Chip on the mountains (p. 29). IEEE Press.

Huang, L., Lelandais-Perrault, C., Kolar, A., & Benabes, P. (2019). A new algorithm for an incremental sigma-delta converter reconstruction filter. In 2019 32nd symposium on integrated circuits and systems design (SBCCI) (pp. 1–6). IEEE.

Lee, S.-C., & Chiu, Y. (2010). Digital calibration of nonlinear memory errors in sigma-delta modulators. IEEE Transactions on Circuits and Systems I: Regular Papers, 57(9), 2462–2475.

Tao, S., & Rusu, A. (2015). A power-efficient continuous-time incremental sigma-delta adc for neural recording systems. IEEE Transactions on Circuits and Systems I: Regular Papers, 62(6), 1489–1498.

Garcia, J., Rodriguez, S., & Rusu, A. (2012a). A low-power CT incremental 3rd order \(\sigma \delta\) ADC for biosensor applications. IEEE Transactions on Circuits and Systems I: Regular Papers, 60(1), 25–36.

Garcia, J., Rodriguez, S., & Rusu, A. (2012b). On continuous-time incremental \(\sigma \delta\) ADCs with extended range. IEEE Transactions on Instrumentation and Measurement, 62(1), 60–70.

Steensgaard, J., Zhang, Z., Yu, W., Sárhegyi, A., Lucchese, L., Kim, D.-I., & Temes, G. C. (2008). Noise-power optimization of incremental data converters. IEEE Transactions on Circuits and Systems I: Regular Papers, 55(5), 1289–1296.

Funding

Funding was provided by Université Paris-Saclay (FR); Sorbonne Université; Centralesupélec; CNRS; Laboratoire GEEPS.

Author information

Authors and Affiliations

Corresponding author

Additional information

Publisher's Note

Springer Nature remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

Rights and permissions

About this article

Cite this article

Huang, L., Lelandais-Perrault, C., Kolar, A. et al. A circuit-level inverter-based switched capacitor integrator model justified by post-layout simulations of an incremental sigma-delta converter. Analog Integr Circ Sig Process 107, 51–64 (2021). https://doi.org/10.1007/s10470-021-01813-2

Received:

Revised:

Accepted:

Published:

Issue Date:

DOI: https://doi.org/10.1007/s10470-021-01813-2