Abstract

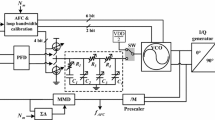

A new adaptive bandwidth, adaptive jitter frequency synthesizer is proposed. This synthesizer is designed in such a way that the ratio of bandwidth to the reference frequency is kept approximately fixed in order to maintain the optimum jitter performance. The proposed structure employs a novel programmable charge pump and a charge pump controller circuit. Regarding the control voltage of the LC voltage controlled oscillator (VCO), the charge pump controller determines the output sink/source current of the charge pump and maintains the ratio of the charge pump current to the VCO oscillation frequency fixed. It is shown that using this idea and proposed building blocks, variations of the desired ratio of the bandwidth to the reference frequency are canceled and thus, the optimum output jitter manner of the frequency synthesizer is preserved. The proposed structure is simulated in 0.18 µm CMOS technology and simulation results are presented and discussed.

Similar content being viewed by others

References

Razavi, B. (2000). Phase locking in high-performance systems. Washington: IEEE Press.

Rogers, J., Plett, C., & Dai, F. (2006). Integrated circuit design for high-speed frequency synthesis. Norwood: Artech House.

Maniatis, J. G. (1996). Low-jitter process-independent DLL and PLL based on self-biased techniques. IEEE Journal of Solid-State Circuits, 31(11), 1723–1732.

Esmaeili Taheri, H. (2017). A 4–4.8 GHz adaptive bandwidth, adaptive jitter phase locked loop. Engineering, Technology & Applied Science Research, 7(2), 1473–1477.

Wu, T., Hanumolu, P. K., Mayaram, K., & Moon, U. (2009). Method for a constant loop bandwidth in LC-VCO PLL frequency synthesizers. IEEE Journal of Solid-State Circuits, 44(2), 427–435.

Shu, K., & Sinencio, E. S. (2005). CMOS PLL synthesizers, analysis, and design. Boston: Springer.

Kim, J. (2009). Adaptive bandwidth phase locked loop with continuous background frequency calibration. IEEE Transactions on Circuits and Systems—II: Express Briefs, 56(3), 205–209.

Lee, J., & Kim, B. (2000). A low noise fast lock phase locked loop with adaptive bandwidth control. IEEE Journal of Solid-State Circuits, 35(8), 1137–1145.

Mansouri, M., & Yang, C. (2003). A low power adaptive bandwidth PLL and clock buffer with supply noise compensation. IEEE Journal of Solid-State Circuits, 38(1), 1804–1812.

Author information

Authors and Affiliations

Corresponding author

Rights and permissions

About this article

Cite this article

Esmaeili Taheri, H., Ehsanian, M. A new adaptive bandwidth, adaptive jitter frequency synthesizer using programmable charge pump circuit. Analog Integr Circ Sig Process 96, 373–384 (2018). https://doi.org/10.1007/s10470-018-1228-z

Received:

Revised:

Accepted:

Published:

Issue Date:

DOI: https://doi.org/10.1007/s10470-018-1228-z