Abstract

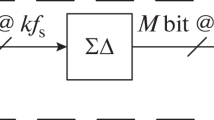

We present a novel delta–sigma digital-to-analog converter (DSDAC) using a jitter shaper to augment the noise caused by clock jitter. The jitter shaper is designed for a 0.18 µm CMOS and comprises switched capacitor and sample-and-hold circuits. We simulate the DSDAC in MATLAB and design and simulate the complete jitter shaper circuit in SPICE. We predict that the jitter shaper will improve the signal-to-noise ratio by 47.2 dB (MATLAB) up to 24.6 dB (SPICE).

Similar content being viewed by others

References

Schreier, R., & Temes, G. C. (2004). An introduction to ΔΣ analog/digital converters (translated from the Japanese by T. Waho & A. Yasuda). Maruzen Co., Ltd.

Cherry, J. A., & Snelgrove, W. M. (1999). Clock jitter and quantizer metastability in continuous-time delta–sigma modulators. IEEE Transactions on Circuits and Systems II, 46, 376–389.

Fujimori, I., Nogi, A., & Sugimoto, T. (2000). A multibit delta–sigma audio DAC with 120-dB dynamic range. IEEE Journal of Solid-State Circuits, 35(8), 1066–1073.

Kobayashi, H., Kurosawa, N., Miyauchi, I., Kawakami, S., Kogure, H., Komuro, T., & Sakayori, H. (2003). Timing error analysis in digital-to-analog converter—effects of sampling clock jitter and timing skew (Glitch). In 10th electronic devices and systems conference 2003, Brno, pp. 212–299.

Acknowledgments

This work was supported by the VLSI Design and Education Center (VDEC), University of Tokyo, in collaboration with Cadence Design Systems, Inc., San Jose, California, U.S.A.

Author information

Authors and Affiliations

Corresponding author

Rights and permissions

About this article

Cite this article

Watanabe, Y., Saikatsu, S., Yoshino, M. et al. Delta–sigma DAC with jitter-shaper-reducing jitter noise. Analog Integr Circ Sig Process 85, 243–251 (2015). https://doi.org/10.1007/s10470-015-0600-5

Received:

Revised:

Accepted:

Published:

Issue Date:

DOI: https://doi.org/10.1007/s10470-015-0600-5