Abstract

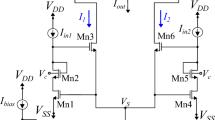

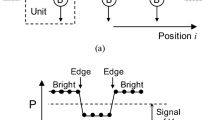

In this study, the design and realization of an analogue CMOS prototype vision chip with Prewitt edge processing is presented. The chip is designed with voltage and current mode and the main parts are one 16 × 16 pixel array, one pair of absolute value circuits and two transimpedance amplifiers. The technology process is TSMC 0.35 μm. The edge processing is performed parallely on pixel level. The performance of the sensor comprises a processing time of 450 ns; optical dynamic range of 53 dB; power consumption at 30 frames per second of 1.5 mW; peak signal to noise ratio of 44 dB.

Similar content being viewed by others

References

Moini, A. (1997). Vision chips or seeing silicon. Adelaide: University of Adelaide.

Wilson, M., Kannangara, K., Smith, G., Simmons, M., & Raguse, B. (2002). Nanotechnology. Sydney, Florida: University of New South Wales Press, Chapman & Hall/CRC.

Davies, E. R. (2005). Machine vision: theory, algorithms and practicalities. San Francisco, CA: Morgan Kauffman Elsevier.

Roska, T., & Rodriguez-Vazquez, A. (2001). Toward the visual microprocessor. New York: Wiley.

Mead, C. (1989). Analog VLSI and neural systems. New York: Addison-Wesley.

Kagawa, K., Yasuoka, K., Ng, D. C., Furumiya, T., Tokuda, T., Ohta, J., et al. (2004). Pulse-domain digital image processing for vision chips employing low voltage in deep-submicrometer technologies. IEEE Journal of Selected Topics in Quantum Electronics, 10, 816–828.

Garcia-Lamont, J., Moreno-Cadenas, J. A., & Gomez-Castaneda, F. (2004). Analogue CMOS prototype vision chip with fuzzy kohonen network processing for grey level image segmentation. International Journal of Electronics, 91, 697–717.

Garcia-Lamont, J., Villa-Vargas, L. A., & Romero-Salcedo, M. (2009). CMOS prototype visión chip with digital pixel structure for grey level image segmentation by means of thresholding and time multiplexing. International Journal of Electronics, 96(8), 795–802.

Haralick, R. M., & Shaphiro, L. G. (1992). Computer and robot vision. New York: Addison-Wesley.

Castleman, K. R. (1996). Digital image processing. Englewood cliffs, NJ: Prentice Hall.

Nakamura, J. (2006). Image sensors and signal processing for digital still cameras. Boca Raton, FL: CRC Taylor & Francis.

Cherem Schneider, M., & Galup-Montoro, C. (2010). CMOS analog design using all-region mosfet modeling. Cambridge, UK: Cambridge University Press.

Tänzer, M., Graupner, A., & Schüffny, R. (2004). Design and evaluation of current-mode image sensors in CMOS technology. IEEE Transactions on Circuits and Systems-II: Express Briefs, 51(10), 566–570.

Huang, Y., & Horney, R. I. (2003). Current-mode CMOS image sensor using lateral bipolar phototransistors. IEEE Transactions on electron devices, 50(12), 2570–2573.

Baturone-Castillo, I. (1996). Implementation of fuzzy controllers, chap. 4. Spain: Universidad de Sevilla.

Baker, R. J. (2005). CMOS, circuit design, layout and simulation, Chap. 21. Hoboken, NJ: Wiley-Interscience.

Oguey, H., & Aebischer, D. (1997). CMOS current reference without resistance. IEEE Journal of Solid State, 32(7), 1132–1135.

Author information

Authors and Affiliations

Corresponding author

Rights and permissions

About this article

Cite this article

Garcia-Lamont, J. Analogue CMOS prototype vision chip with prewitt edge processing. Analog Integr Circ Sig Process 71, 507–514 (2012). https://doi.org/10.1007/s10470-011-9694-6

Received:

Revised:

Accepted:

Published:

Issue Date:

DOI: https://doi.org/10.1007/s10470-011-9694-6