Abstract

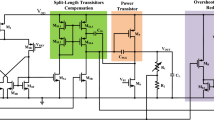

A 3-A CMOS low-dropout regulator (LDO) is presented by utilizing adaptive Miller compensation (AMC) technique, which provides high stability, as well as fast line and load transient responses. The proposed LDO has been fabricated in a standard 0.5 μm CMOS technology, and the die area is small as 1330 μm × 1330 μm with the area-efficient waffle layout for power transistors. Both load and line regulation are less than ±0.1%. And the output voltage can recover within 80 μs for full load changes. The power–supply rejection ratio (PSRR) at 20 KHz is −30 dB. Moreover, it is stable enough with a ceramic capacitor small to 2.2 μF, and the added series resistance is not needed.

Similar content being viewed by others

Reference

K.N. Leung and P.K.T. Mok, “A capacitive-free CMOS low-dropout regulator with damping-factor-control frequency compensation.” IEEE J. Solid-State Circuits, vol. 38, pp. 1691–1702, Oct. 2003.

G.A. Rincon-Mora and P.E. Allen, “A low-voltage, low quiescent current, low drop-out regulator.” IEEE J. Solid-State Circuits, vol. 33, pp. 36–44, Jan. 1998.

X.Q. Lai, J.Z. Xie, P.C. Du, and Z.Z. Sun, “A dynamic Miller compensation circuit for LDO regulator.” Research & Progress of SSE, vol. 25, pp. 380–385, Aug. 2005.

K.N. Leung and P.K.T. Mok, “Analysis of multistage amplifier-frequency compensation.” IEEE Trans. Circuits Syst. I, vol. 48, pp. 146–150, Sept. 2001.

Phillip E. Allen and Douglas R. Holberg, CMOS Analog Circuit Design, 2nd edition. Oxford Press, 2002, pp. 253–269.

J.C. Teel, “Understanding noise in linear regulator.” Texas Instruments Analog Applicant, 2005.

J.C. Teel, “Understanding PSRR in linear regulator.” Texas Instruments Analog Applicant, 2005.

Alan Hastings, The Art of Analog Layout. Prentice Hall, Dec. 2000, pp. 407–417.

Alan B. Grebene, Bipolar and MOS Analog Integrated Circuit Design. John Wily & Sons, New York, 1991, pp. 509–512.

Author information

Authors and Affiliations

Corresponding author

Additional information

Xinquan Lai received his BSc degree in Technical Physics in 1987, and MSc degree in Electronic Engineering in 1993, both from the Xidian University, Xi’an, China. And he received a PhD degree in Computer Science & Engineering from the Northwestern Polytechnical University (NPU) in 1998. He is currently a professor in Xidian University. His present research interests include mixed signal VLSI/ASIC and SOC design, CMOS Sensor, and power management IC design, validation, test and other relative theories.

Jianping Guo was born in Jiangxi, P.R. China in 1981. He received the BSc and MSc degrees in electronic engineering from Xidian University, Xi’an, China, in 2003 and 2006, respectively. He is currently severed as power management IC engineer in Xi’an Deheng Microelectronic Inc. His research interest involves power management IC design such as LDO linear regulator, DC-DC switching regulator etc.

Zuozhi Sun was born in Zhejiang, P. R. China in 1978. He received the BSc and MSc degrees in electronic engineering from Xidian University, Xi’an, China, in 2000 and 2003, respectively. He joined Xi’an Deheng Microelectronic Inc. in 2003, where he works on development of power management IC. His research interest involves power management IC, audio amplifier etc.

Jianzhang Xie received his BSc and MSc degrees in electronic engineering from Xidian University, Xi’an, China, in 1998 and 2005, respectively. He joined AIWA (Shenzhen) Ltd. as an electronic circuit designer in 1998, and now he is severed as an analog and mixed IC engineer in RENEX Technology (Shanghai) Ltd. His research interest involves power management IC, PLLs and high speed communication circuits.

Rights and permissions

About this article

Cite this article

Lai, X., Guo, J., Sun, Z. et al. A 3-A CMOS low-dropout regulator with adaptive Miller compensation. Analog Integr Circ Sig Process 49, 5–10 (2006). https://doi.org/10.1007/s10470-006-8697-1

Received:

Revised:

Accepted:

Published:

Issue Date:

DOI: https://doi.org/10.1007/s10470-006-8697-1