Abstract

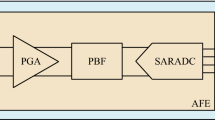

This paper presents a capacitive analog front-end (AFE) integrated circuit (IC) with a dual-mode automatic parasitic cancellation loop. Capacitive AFEs are widely used for various capacitive microsensors based on micro-electro-mechanical system technologies. This paper presents a capacitive AFE IC with a dual-mode automatic parasitic cancellation loop. The capacitive AFE adopts the correlated double-sampling technique for low-noise characteristics. The automatic parasitic cancellation loop removes the unwanted offset caused by the input parasitic capacitances by implementing a successive approximation register scheme. The automatic parasitic cancellation loop includes two parts: a capacitor domain cancellation loop and a charge domain cancellation loop. The capacitor domain loop and charge domain loop execute coarse parasitic and fine parasitic cancellations, respectively. The chip is fabricated using the 0.18-μm complementary metal–oxide–semiconductor process and has an active area of 2.39 mm2. With the dual-mode parasitic cancellation loop, the input parasitic capacitance, ranging from −10.6 to 10.6 pF, can be cancelled with a resolution of 0.224 fF. The measured automatic offset cancellation time is lower than 14 ms. The power consumption is 928 μW with a 3.3 V supply.

Similar content being viewed by others

References

Aaltonen L, Halonen KAI (2009) Pseudo-continuous-time readout circuit for a 300°/s capacitive 2-axis micro-gyroscope. IEEE J Solid State Circuits 44:3609–3620

Dobrzynska JA, Gijs MAM (2013) Polymer-based flexible capacitive sensor for three-axial force measurements. J Micromech Microeng 23:1–11

Enz CC, Temes GC (1996) Circuit techniques for reducing the effects of op-amp imperfections: autozeroing, correlated double sampling, and chopper stabilization. Proc IEEE 84:1584–1614

Ha H, Suh Y, Lee S, Park H, Sim J (2012) A 0.5 V 11.3-μW 1-kS/s resistive sensor interface circuit with correlated double sampling. In: Proceedings of the IEEE custom integrated circuits conference (CICC), pp 1–4

Lee S, Ko H, Choi B, Cho D (2010) Optimal and robust design method for two-chip out-of-plane microaccelerometers. Sensors 10:10524–10544

Liu CC, Chang SJ, Huang GY, Lin YZ (2009) A 0.92 mW 10-bit 50-MS/s SAR ADC in 0.13 μm CMOS process. In: Symposium on VLSI circuits, pp 236–237

Ouh HK, Choi J, Lee J, Han S, Kim S, Seo J, Lim K, Seok C, Lim S, Kim H, Ko H (2014) Capacitive readout circuit for tri-axes microaccelerometer with sub-fF offset calibration. J Semicond Tech Sci 14:83–91

Ranganathan S, Inerfield M, Roy S, Garverick SL (2000) Sub-femtofarad capacitive sensing for microfabricated transducers using correlated double sampling and delta modulation. IEEE Trans Circuit Syst II 47:1170–1176

Shiah J, Mirabbasi S (2013) A 5-V 555-μW 0.8-μm CMOS MEMS capacitive sensor interface using correlated level shifting. In: Proceedings of the IEEE international symposium on circuits system (ISCAS), pp 1504–1507

Shiah J, Mirabbasi S (2014) A 5-V 290-μW low-noise chopper-stabilized capacitive-sensor readout circuit in 0.8-μm CMOS using a correlated-level-shifting technique. IEEE Trans Circuit Syst II 61:254–258

Shin DY, Lee H, Kim S (2011) A delta–sigma interface circuit for capacitive sensors with an automatically calibrated zero point. IEEE Trans Circuit Syst II 58:90–94

Song H, Park Y, Kim H, Cho D, Ko H (2015) Fully integrated low-noise readout circuit with automatic offset cancellation loop for capacitive microsensors. Sensors 15:26009–26017

Sun H, Fang D, Jia K, Maarouf F, Qu H, Xie H (2011) A low-power low-noise dual-chopper amplifier for capacitive CMOS-MEMS accelerometers. IEEE Sens J 11:925–933

Tan SS, Liu CY, Yeh LK, Chiu YH, Lu MSC, Hsu KYJ (2011) An integrated low-noise sensing circuit with efficient bias stabilization for CMOS MEMS capacitive accelerometers. IEEE Trans Circuit Syst I 58:2661–2672

Tan Z, Shalmany SH, Meijer GCM, Pertijs MAP (2012) An energy-efficient 15-bit capacitive-sensor interface based on period modulation. IEEE J Solid State Circuits 47:1703–1711

Tez S, Akin T (2013) Fabrication of a sandwich type three axis capacitive MEMS accelerometer. In: Proceedings of the IEEE sensor, pp 1–4

Wong SS, Chio UF, Zhu Y, Sin SW, Seng-Pan U, Martins RP (2013) A 2.3 mW 10-bit 170 MS/s two-step binary-search assisted time-interleaved SAR ADC. IEEE J Solid State Circuits 48:1783–1794

Yole Developpement and System Plus Consulting (2014) Inertial MEMS Manufacturing Trends. http://www.systemplus.fr/reverse-costing-reports/inertial-mems-inertial-memsmanufacturing-trends-2014-volumes-1-2. Accessed 10 Oct 2015

Yu HY, Qin N, Huang JQ, Huang QA (2012) A MEMS capacitive pressure sensor compatible with CMOS process. In: Proceedings of the IEEE sensors, pp 1–4

Zhao M, Lu W, Chen Z, Zhang T, Wu F, Zhang Y, Liu D (2015) A low-noise switched-capacitor interface for a capacitive micro-accelerometer. In: Proceedings of the IEEE international symposium circuits on systems (ISCAS), pp 337–340

Acknowledgements

This research was supported by Nano. Material Technology Development Program through the National Research Foundation of Korea (NRF) funded by the Ministry of Science, ICT and Future Planning (NRF-2015M3A7B7046616). This research was also supported by IDEC.

Author information

Authors and Affiliations

Corresponding author

Rights and permissions

About this article

Cite this article

Mun, Y., Kim, H., Ko, Y. et al. Capacitive analog front-end circuit with dual-mode automatic parasitic cancellation loop. Microsyst Technol 23, 515–523 (2017). https://doi.org/10.1007/s00542-017-3288-x

Received:

Accepted:

Published:

Issue Date:

DOI: https://doi.org/10.1007/s00542-017-3288-x