Abstract

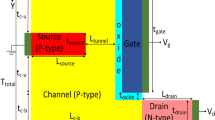

In this paper, we present a rigorous numerical simulation study on temperature sensitivity for tunnel field effect transistor (TFET). The presented temperature sensitivity analysis is studied on different digital, analog and RF figure of merits for conventional TFETs. In addition, sensitivities of the conventional TFETs are compared with proposed vertical tunneling-based TFET (V-DMGTFET) and detailed discussion is presented for the same. In comparative study, we observed that proposed V-DMGTFET is less sensitive to temperature variations compared to the conventional TFETs. This indicates that proposed V-DMGVTFET is more reliable to use in low power application at high temperatures compared to the conventional TFET.

Similar content being viewed by others

References

A.M. Ionescu, H. Riel, Tunnel field effect transistors as energy efficient electronic switches. Nature 479, 329–337 (2011)

N. Guenifi, S.B. Rahi, T. Ghodbane, Rigorous study of double gate tunneling field effect transistor structure based on silicon. Mater. Focus 7, 1–7 (2018)

M. R. Salehi, E. Abiri, S. E. Hosseini and B. Dorostkar, Analysis and optimization of tunnel FET with band gap engineering. In: 1st Iranian Conference on Electrical Engineering (ICEE), Iran, May 2013

P. Jain, P. Rastogi, C. Yadav, A. Agarwal, Y.S. Chauhan, Band-to-band tunneling in Γ valley for Ge source lateral tunnel field effect transistor: thickness scaling. J. Appl. Phys. 122(1), 0145021–0145027 (2017)

K. Boucart, A.M. Ionescu, Double-gate tunnel FET with high-k gate dielectric. IEEE Trans. Electron Dev. 54(7), 1725–1733 (2007)

S.B. Rahi, P. Asthana, S. Gupta, Heterogate junctionless tunnel field-effect transistor: future of low-power devices. J. Comput. Electron. 16(1), 30–38 (2017)

P.K. Asthana, Y. Goswami, S. Basak, S.B. Rahi, B. Ghosh, Improved performance of a junctionless tunnel field effect transistor with a Si and SiGe heterostructure for ultra low power applications. RSC Adv. 60(5), 48779–48785 (2015)

N. Sharma, S.S. Chauhan, Enhancing Analog Performance suppression of subthreshold swing using hetero-junctionless double gate TFETs. Superlattices Microstruct. 112, 257–261 (2017)

S.B. Rahi, B. Ghosh, High-k double gate junctionless tunnel FET with a tunable bandgap. RSC Adv. 67(5), 54544–54550 (2015)

M.J. Kumar, S. Janardhanan, Doping-less tunnel field effect transistor: design and investigation. IEEE Trans. Electron Dev. 60(10), 3285–3290 (2013)

N. Sharma, S.S. Chauhan, Dual metal drain Ge-source dopingless TFET with enhanced turn-ON steep subthreshold swing and high ON-current. Electron. Lett. 53(14), 960–962 (2017)

Y. Wang, W.H. Zhang, C.H. Yu, F. Cao, Sandwich double gate vertical tunneling field-effect transistor. Superlattices Microstruct. 93, 138–143 (2016)

Y.J. Yoon, S.Y. Woo, J.H. Seo, Design optimization of vertical double-gate tunneling field-effect transistors. J. Kor. Phys. Soc. 61(10), 1679–1682 (2012)

X. Wang, W. Cho, H.W. Baac, D. Seo, I.H. Cho, Optimization of double-gate vertical channel tunneling field effect transistor (DVTFET) with dielectric sidewall. J. Semicond. Technol. Sci. 17(2), 192–198 (2017)

S.S. Chauhan, Design of double gate vertical tunnel field effect transistor using HDB and its performance estimation. Superlattices Microstruct. 117, 1–8 (2018)

N. Paras, S.S. Chauhan, Vertical tunneling based tunnel field effect transistor with workfunction engineered hetero-gate to enhance DC characteristics. J. Nanoelectron. Optoelectron. 14(1), 50–53 (2019)

M.H. Chiang, J.N. Lin, K. Kim, C.T. Chuang, Random dopant fluctuation in limited-width FinFET technologies. IEEE Trans. Electron Dev. 54(8), 2055–2060 (2007)

C. Shan, Y. Wang, M.T. Bao, A charge-plasma-based transistor with induced graded channel for enhanced analog performance. IEEE Trans. Electron Dev. 63(6), 2275–2281 (2016)

S.B. Rahi, B. Ghosh, B. Bishnoi, Temperature effect on hetero structure junctionless tunnel FET. J. Semicond. 36(3), 0340021–0340025 (2015)

M. Born, K.K. Bhuwalka, M. Schindler, U. Abilene, M. Schmidt, T. Sulima, I. Eisele, Tunnel FET: a CMOS device for high temperature applications. In: 25th International Conference on Microelectronics, Serbia, pp. 124–127 (2006)

P.F. Guo, L.T. Yang, Y. Yang, L. Fan, G.Q. Han, G.S. Samudra, Y.C. Yeo, Tunneling field-effect transistor: effect of strain and temperature on tunneling current. IEEE Electron Dev. Lett. 30, 981–983 (2009)

J. Wan, C.L. Royer, A. Zaslavsky, S. Cristoloveanu, SOI TFETs: Suppression of ambipolar leakage and low-frequency noise behavior. In: Proceedings of the European Solid-State Device Research Conference (ESSDERC), pp. 341–344 (2010)

T. Nirschl, P-F. Wang, W. Hansch, D. Schmitt-Landsiedel, The tunneling field effect transistors (TFET): the temperature dependence, the simulation model, and its application. In: Proceedings of the 2004 International Symposium on Circuits and Systems, pp. 713–716 (2004)

H. Schmid, M.T. Bjrk, J. Knoch, S. Karg, H. Riel, W. Riess, Doping limits of grown in situ doped silicon nanowires using phosphine. Nano Lett. 57(4), 820–826 (2009)

R. Asra, M. Shrivastava, K.V.R.M. Murali, R.K. Pandey, H. Gossener, V.R. Rao, A tunnel FET for VDD scaling below 0.6 V with a CMOS comparable performance. IEEE Trans. Electron Dev. 58(7), 1855–1863 (2011)

W. Long, H. Ou, J.M. Kuo, K.K. Chin, Dual-material gate (DMG) field effect transistor. IEEE Trans. Electron Dev. 46(5), 865–870 (1999)

A. Goel, S.K. Gupta, K. Roy, Asymmetric drain spacer extension (ADSE) FinFETs for low power and robust SRAMs. IEEE Trans. Electron Dev. 58(2), 296–308 (2011)

Sentaurus Device User Guide, Synopsys Inc., Mountain View (2013)

J. Wan, C.L. Royer, A. Zaslavsky, S. Cristoloveanu, Tunneling FETs on SOI: Suppression of ambipolar leakage, low-frequency noise behavior, and modeling. Solid-State Electron. 65–66, 226–233 (2011)

Y. Wang, Y.-F. Wang, F. Cao, Asymmetric dual-gate tunneling FET with improved performance. Superlattices Microstruct. 91, 216–224 (2016)

Author information

Authors and Affiliations

Corresponding author

Additional information

Publisher's Note

Springer Nature remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

Rights and permissions

About this article

Cite this article

Paras, N., Chauhan, S.S. Temperature sensitivity analysis of vertical tunneling based dual metal Gate TFET on analog/RF FOMs. Appl. Phys. A 125, 316 (2019). https://doi.org/10.1007/s00339-019-2621-x

Received:

Accepted:

Published:

DOI: https://doi.org/10.1007/s00339-019-2621-x