Abstract

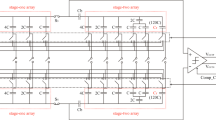

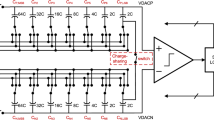

A high energy efficiency and linearity switching scheme is proposed for the successive approximation register (SAR) analog-to-digital converter (ADC). With the tri-level switching scheme, the capacitor area is reduced by 75% compared with the conventional switching scheme. In addition, the proposed switching scheme also combines the most significant bit (MSB) splitting method and the monotonic switching scheme for linearity and energy efficiency improvement. Furthermore, by inserting a connection switch between the MSB splitting capacitors and the least significant bit (LSB) capacitors, the reset energy can be avoided. The MATLAB simulation results show that compared to the monotonic switching scheme, the proposed switching scheme achieves a 93.29% reduction in average switching energy and 50% capacitor area saving without the reset energy when the parasitic capacitance is taken into consideration. Meanwhile, the linearity is enhanced by √2 × from the Monte Carlo simulation. The post-simulation results indicate that a 10-bit SAR ADC with the proposed switching scheme can achieve a signal-to-noise distortion ratio (SNDR) of 57.81 dB and a spurious-free dynamic range (SFDR) of 68.63 dB at the sampling rate of 1 MS/s in a 180-nm CMOS process. The SAR ADC consumes 15.25 μW power at a 1 V supply, resulting in a figure of merit (FoM) of 24.03 fJ/conv.-step. The active area of this ADC is only 0.057 mm2.

Similar content being viewed by others

Data availability

Date sharing is not applicable to this article as no datasets were generated or analyzed during the current study.

References

S.U. Baek, K.Y. Lee, M. Lee, Energy-efficient switching scheme for SAR ADC using zero-energy dual capacitor switching. Analog Integr. Circ. Signal Process. 94(2), 317–322 (2018)

L Chen, A Sanyal, J Ma et al. (2016) Comparator common-mode variation effects analysis and its application in SAR ADCs. In: IEEE International symposium on circuits and systems (ISCAS), Montreal, pp. 2014–2017

T. Chen, J. Cai, X. Li et al., High-efficient two-step switching scheme for SAR ADC with dual-capacitive arrays and four-input comparator. Analog Integr. Circ. Signal Process. 101, 363–373 (2019)

A.R. Ghasemi, M. Saberi, R. Lotfi, A low-power capacitor switching scheme with low common-mode voltage variation for successive approximation ADC. Microelectron. J. 61, 15–20 (2017)

S. Hsieh, C. Hsieh, 0.4-V 13-bit 270-kS/s SAR-ISDM ADC with Opamp-Less Time-Domain integrator. IEEE J. Solid-State Circuits 54(6), 1648–1656 (2019)

M. Hu, J. Jin, Y. Guo et al., A power-efficient SAR ADC with optimized timing-redistribution asynchronous SAR logic in 40-nm CMOS. Circuits. Syst. Signal Process. 40, 3125–3142 (2021)

Y. Hu, A. Liu, B. Li, Z. Wu, Closed-loop charge recycling switching scheme for SAR ADC. Electron. Lett. 53(2), 66–68 (2016)

J. Lin, C. Hsieh, A 0.3-V 10-bit 1.17 f SAR ADC with merge and split switching in 90 nm CMOS. IEEE Trans. Circuits. Syst. I Regul. Pap. 62(1), 70–79 (2015)

C.C. Liu, S.J. Chang, G.Y. Huang, Y.Z. Lin, A 10-bit 50-MS/s SAR ADC with a monotonic capacitor switching procedure. IEEE J. Solid-State Circuits. 45(4), 731–740 (2010)

S. Liu, H. Han, R. Ding, Z. Zhu, Energy-efficient switching scheme for SAR ADC with only two reference voltages. Analog Integr. Circ. Signal Process. 97(3), 603–613 (2018)

S. Liu, Y. Shen, Z. Zhu, A 12-Bit 10 MS/s SAR ADC with high linearity and energy-efficient switching. IEEE Trans. Circuits. Syst. I Regul. Pap. 63(10), 1616–1627 (2016)

J. Luo, Y. Liu, J. Li et al., A low voltage and low power 10-bit Non-Binary 2b/Cycle time and voltage based SAR ADC. IEEE Trans. Circuits. Syst. I Regul Pap. 67(4), 1136–1148 (2020)

Y. Shen, X. Tang, L. Shen et al., A 10-bit 120-MS/s SAR ADC with reference ripple cancellation technique. IEEE J. Solid-State. Circuits. 55(3), 680–692 (2020)

X. Tang, X. Yang, W. Zhao et al., 13.5-ENOB, 107-µW Noise-Shaping SAR ADC with PVT-Robust Closed-Loop dynamic amplifier. IEEE J. Solid-State. Circuits. 55(12), 3248–3258 (2020)

X. Tong, Y. Chen, Low-Power High-Linearity switching procedure for Charge-Redistribution SAR ADC. Circuits Syst. Signal Process. 36(9), 3825–3834 (2017)

X. Tong, M. Song, Y. Chen, S. Dong, A 10-Bit 120-kS/s SAR ADC without reset energy for biomedical electronics. Circuits Syst. Signal Process. 38(12), 5411–5425 (2019)

A. Wu, J. Wu, J. Huang, Energy-efficient switching scheme for ultra-low voltage SAR ADC. Analog Integr. Circ. Signal Process. 90(2), 507–511 (2017)

L. Xie, Y. Wang, J. Su et al., Switching scheme with 984% switching energy reduction and high accuracy for SAR ADCs. Analog Integr. Circ. Signal Process. 90(3), 681–686 (2017)

X. Xin, J. Cai, T. Chen, Q. Yang, A 04-V 10-bit 10-kS/s SAR ADC in 018-µm CMOS for low energy wireless senor network chip. Microelectron. J. 83, 104–116 (2019)

C. Yang, E. Olieman, A. Litjes et al., An area-efficient SAR ADC with mismatch error shaping technique achieving 102-dB SFDR 90.2-dB SNDR over 20-kHz bandwidth. IEEE Trans. Very Large Scale Integr. Syst. 29(8), 1575–1585 (2021)

W. Yu, S. Sen, B.H. Leung, Distortion analysis of MOS track-and-hold sampling mixers using time-varying Volterra series. IEEE Trans. Circuits Syst. II Express. Briefs. 46(2), 101–113 (1999)

C. Yuan, Y. Lam, Low-energy and area-efficient tri-level switching scheme for SAR ADC. Electron. Lett. 48(9), 482–483 (2012)

H. Zhang, H. Zhang, R. Zhang, Energy-efficient higher-side-reset-and-set switching scheme for SAR ADC. Electron. Lett. 53(18), 1238–1240 (2017)

Y. Zhang, Y. Li, Z. Zhu, A charge-sharing switching scheme for SAR ADCs in biomedical applications. Microelectron. J. 75, 128–136 (2018)

Y. Zhu, C.H. Chan, U.F. Chio et al., A 10-bit 100-MS/s reference-free SAR ADC in 90 nm CMOS. IEEE J. Solid-State Circuits. 45(6), 1111–1121 (2010)

Z. Zhu, Z. Qiu, M. Liu et al., A 6-to-10-bit 05 V-to-09 V reconfigurable 2 MS/s power scalable SAR ADC in 018-µm CMOS. IEEE Trans. Circuits Syst. I Regul. Pap. 62(3), 689–696 (2015)

Acknowledgements

This work was supported by the National Natural Science Foundation of China under Grant 62104193 and Grant 61674122.

Author information

Authors and Affiliations

Corresponding author

Additional information

Publisher's Note

Springer Nature remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

Rights and permissions

About this article

Cite this article

Tong, X., Zhao, S. & Xin, X. High Energy Efficiency and Linearity Switching Scheme Without Reset Energy for SAR ADC. Circuits Syst Signal Process 41, 5872–5894 (2022). https://doi.org/10.1007/s00034-022-02038-y

Received:

Revised:

Accepted:

Published:

Issue Date:

DOI: https://doi.org/10.1007/s00034-022-02038-y