Abstract

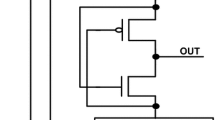

The leakage power, a.k.a. static power, increases in deep-submicron technologies due to short-channel effects. This article proposes a novel input-controlled leakage restrainer transistor (ICLRT)-based technique to reduce leakage power as well as the short-circuit power. The main idea is to place a PMOS and an NMOS ICLRT on top of the pull-up network (PUN) and at the bottom of the pull-down network (PDN), respectively, on all paths from either the supply voltage or the ground to the output. The ICLRTs are deliberately used as a stack structure while being controlled by the input signals to lead the output to stronger low and high logic levels. In fact, the proposed technique reduces the leakage and short-circuit currents and, consequently, powers by increasing the threshold voltage and decreasing the gate-source voltage of the main transistors. Using the proposed technique, logical NOT, NAND, NOR, XOR, and XNOR static gates are designed and evaluated by SPICE simulations in 22-nm BSIM4 (level-54 parameters) CMOS technology. Simulation results with 0.9-V power supply voltage show that power–delay product (PDP) is reduced by 27.66%, 16.7%, and 21.58% for NOT, NOR, and XOR with respect to its best counterpart and by 32.62%, 47%, 49.23%, and 38.77% for NOT, NAND, NOR, and XOR with respect to the conventional static CMOS structures. Furthermore, Monte Carlo analysis is also performed to ensure the stability and robustness of the circuit’s performance in the presence of the process, voltage, and temperature (PVT) variations.

Similar content being viewed by others

Data Availability

The datasets generated and analyzed during the current study are available from the first author on reasonable request.

References

M. Aguirre, M. Linares, CMOS full-adders for energy-efficient arithmetic applications. IEEE Trans. Very Large Scale Integr. Syst. 19, 718–721 (2011)

B.H. Calhoun, F.A. Honoré, A.P. Chandrakasan, A leakage reduction methodology for distributed MTCMOS. IEEE J. Solid-State Circuits 39, 818–826 (2004)

J.P. Cerqueira, J. Li, M. Seok, A fW- and kHz-class feed-forward leakage self-suppression logic requiring no external sleep signal to enter the leakage suppression mode. IEEE Solid-State Circuits Lett. 1, 150–153 (2018)

J.P. Cerqueira, M. Seok, Temporarily fine-grained sleep technique for near- and subthreshold parallel architectures. IEEE Trans. Very Large Scale Integr. Syst. 25, 189–197 (2017)

J.-H. Choi, Y. Xu, T. Sakurai, Statistical leakage current reduction in high-leakage environments using locality of block activation in time domain. IEEE J. Solid-State Circuits 39, 1497–1503 (2004)

P. Corsonello, M. Lanuzza, S. Perri, Gate-level body biasing technique for high speed sub-threshold CMOS logic gates. Int. J. Circuit Theory Appl. 42, 65–70 (2014)

S. Cserveny, L. Sumanen, J.-M. Masgonty, Ch. Piguet, Locally switched and limited source-body bias and other leakage reduction techniques for a low-power embedded SRAM. IEEE Trans. Circuits Syst. 52, 636–640 (2005)

V. Dokania, A. Islam, Circuit-level design technique to mitigate impact of process, voltage and temperature variations in complementary metal-oxide semiconductor full adder cells. IET Circuits Devices Syst. 9, 204–212 (2015)

A. J. Drake, N. Zamdmer, K. J. Nowka, R. B. Brown, Analysis of the impact of gate body signal phase on DTMOS inverters in 0.13μm PD-SOI. In: IEEE International SOI Conference, pp. 99–100, 2003

S. Goel, A. Kumar, M. Bayoumi, Design of robust, energy-efficient full adders for deep-submicrometer design using hybrid-CMOS logic style. IEEE Trans. Very Large Scale Integr. Syst. 14, 1309–1321 (2006)

N. Hanchate, N. Ranganathan, LECTOR: a technique for leakage reduction in CMOS circuits. IEEE Trans. Very Large Scale Integr. Syst. 12, 196–205 (2004)

J.R. Hauser, Noise margin criteria for digital logic circuits. IEEE Trans. Educ. 36, 363–368 (1993)

H.J. Jeon, Y.-B. Kim, M. Choi, Standby leakage power reduction technique for nanoscale CMOS VLSI systems. IEEE Trans. Instrum. Meas. 59, 1127–1133 (2010)

M.C. Johnson, D. Somasekhar, L.-Y. Chiou, K. Roy, Leakage control with efficient use of transistor stacks in single threshold CMOS. IEEE Trans. Very Large Scale Integr. Syst. 10, 1–5 (2002)

T. Kuroda et al., A 0.9-V, 150 MHz, 10-mW, 4 mm2, 2-D discrete cosine transform core processor with variable threshold-voltage (VT) scheme. IEEE J. Solid-State Circuits 31, 1770–1779 (1996)

W. Lim, I. Lee, D. Sylvester, D. Blaauw, Batteryless sub-nW cortex-M0+ processor with dynamic leakage-suppression logic. In: IEEE International Solid-State Circuits Conference (ISSCC), pp. 146–147, 2015

R. Lorenzo, S. Chaudhury, LCNT-an approach to minimize leakage power in CMOS integrated circuits. Microsyst. Technol. 23, 4245–4253 (2017)

R. Lorenzo, S. Chaudhury, Dynamic threshold sleep transistor technique for high speed and low leakage in CMOS circuits. Circuits Syst. Signal Process 36, 2654–2671 (2017)

N. Maeda et al., A 0.41 µA standby leakage 32 kb embedded SRAM with low-voltage resume-standby utilizing all digital current comparator in 28 nm HKMG CMOS. IEEE J. Solid-State Circuit 48, 917–923 (2013)

M. Morsali, M.H. Moaiyeri, Ultra-high-performance magnetic nonvolatile level converter flip-flop with spin-hall assistance for dual-supply systems with power gating architecture. Circuits Syst. Signal Process (2020). https://doi.org/10.1007/s00034-020-01532-5

M. Morsali, M.H. Moaiyeri, NVLCFF: an energy-efficient magnetic nonvolatile level converter flip-flop for ultra-low-power design. Circuits Syst. Signal Process 39, 2841–2859 (2020)

S. Mutoh et al., 1-V power supply high-speed digital circuit technology with multi-threshold-voltage CMOS. IEEE J. Solid-State Circuits 30, 847–854 (1995)

JCh. Park, V.J. Mooney, Sleepy stack leakage reduction. IEEE Trans. Very Large Scale Integr. Syst. 14, 1250–1263 (2006)

E. Sanchez-Sinencio, A.G. Andreou, Low-Voltage/Low-Power Integrated Circuits (IEEE Press, New York, 1999).

A. Sathanur, L. Benini, A. Macii, E. Macii, M. Poncino, Row-based power-gating: a novel sleep transistor insertion methodology for leakage power optimization in nanometer CMOS circuits. IEEE Trans. Very Large Scale Integr. Syst. 19, 469–482 (2011)

A. Shams, T. Darwish, M. Bayoumi, Performance analysis of low power 1-bit CMOS full adder cells. IEEE Trans. Very Large Scale Integr. Syst. 20, 20–29 (2002)

P.K. Sharma, B. Bhargava, S. Akashe, Reduction of leakage power in digital logic circuits using stacking technique in 45 nanometer regime. Int. J. Electron. Commun. Eng. 7, 60–65 (2013)

V.K. Sharma, M. Pattanaik, B. Raj, ONOFIC approach: low power high speed nanoscale VLSI circuits design. Int. J. Electron. 101, 61–73 (2014)

S. Shigemitsu et al., A 1-V high-speed MTCMOS circuit scheme for power-down application circuits. IEEE J. Solid-State Circuits 32, 861–869 (1997)

N. Sirisantana, L. Wei, K. Roy, High-performance low-power CMOS circuits using multiple channel length and multiple oxide thickness. In: Proceedings International Conference on Computer Design, pp. 227–232, 2000

K. Srikanth, K. Dhireesha, GALEOR: leakage reduction for CMOS circuit. In: Proceedings of 15th IEEE International Conference on Electronics Circuits and Systems, pp. 574–577, 2008

Y. Thonnart, E. Beigné, A. Valentian, P. Vivet, Power reduction of asynchronous logic circuits using activity detection. IEEE Trans. Very Large Scale Integr. Syst. 17, 893–906 (2009)

C. Toumazou, G. Moschytz, B. Gilbert, Trade-Offs in Analog Circuit Design, The Designer’s Companion (Kluwer Academic Publishers, Amsterdam, 2002).

J.W. Tschanz et al., Dynamic sleep transistor and body bias for active leakage power control of microprocessors. IEEE J. Solid-State Circuits 38, 1838–1845 (2003)

P. Upadhyay, R. Kar, D. Mandal, S.P. Ghoshal, A design of low swing and multi threshold voltage based low power 12T SRAM cell. Comput. Electr. Eng. 45, 108–121 (2015)

Y. Wang et al., A 1.1 GHz 12 μA/Mb-leakage SRAM design in 65 nm ultra-low-power CMOS technology with integrated leakage reduction for mobile applications. IEEE J. Solid-State Circuits 43, 172–179 (2008)

L. Wei, Zh. Chen, K. Roy, M.C. Johnson, Y. Ye, V.K. De, Design and optimization of dual-threshold circuits for low-voltage low-power applications. IEEE Trans. Very Large Scale Integr. Syst. 7, 16–24 (1999)

N.H.E. Weste, D. Harris, CMOS VLSI Design: A Circuits and Systems Perspective, 4th edn. (Pearson Education, Delhi, 2011).

H. Wong, H. Iwai, On the scaling issues and high-k replacement of ultrathin gate dielectrics for nanoscale MOS transistors. Microelectron. Eng. 83, 1867–1904 (2006)

K. Zhang et al., SRAM design on 65-nm CMOS technology with dynamic sleep transistor for leakage reduction. IEEE J. Solid-State Circuits 40, 895–901 (2005)

Author information

Authors and Affiliations

Corresponding author

Rights and permissions

About this article

Cite this article

Moradinezhad Maryan, M., Amini-Valashani, M. & Azhari, S.J. A New Circuit-Level Technique for Leakage and Short-Circuit Power Reduction of Static Logic Gates in 22-nm CMOS Technology. Circuits Syst Signal Process 40, 3536–3560 (2021). https://doi.org/10.1007/s00034-020-01639-9

Received:

Revised:

Accepted:

Published:

Issue Date:

DOI: https://doi.org/10.1007/s00034-020-01639-9