Abstract

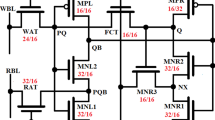

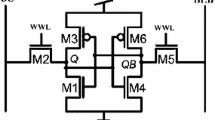

This paper introduces a 10T single-ended SRAM cell with high stability and low static power. The read static noise margin is augmented by using a Schmitt-trigger inverter and decoupling the storage node from the read bitline by adding one transistor. Since writing “1” is difficult in single-ended SRAM cells, using proper capacitive coupling and also extra pMOS transistor as an access transistor mitigates the problem. To evaluate read, write, and hold yields, we performed 10,000 Monto Carlo simulations in the 32-nm technology, and the results show our cell has 7.5×, 1.4×, and 1.1 × more yields than that of the conventional 6T SRAM cell. The proposed cell also has the least static power consumption. This amount is 1.5× less than the conventional 6T at the supply voltage of 0.5 V.

Similar content being viewed by others

Data Availability Statement

This manuscript has no associated data or the data will not be deposited. [Authors’ comment: All data generated or analyzed during this study are included in this published article.]

References

S. Ahmad, M.K. Gupta, N. Alam, M. Hasan, Single-ended schmitt-trigger-based robust low-power SRAM Cell. IEEE Trans. Very Large Scale Int. Syst. 24, 2634–2642 (2016). https://doi.org/10.1109/TVLSI.2016.2520490

S. Ahmad, N. Alam, M. Hasan, Pseudo differential multi-cell upset immune robust SRAM cell for ultra-low power applications. AEU Int. J. Electron. Commun. 83, 366–375 (2018). https://doi.org/10.1016/j.aeue.2017.09.022

S. Ahmad, B. Iqbal, N. Alam, M. Hasan, Low leakage fully half-select-free robust SRAM cells with BTI reliability analysis. IEEE Trans. Device Mater. Reliab. 18, 337–349 (2018). https://doi.org/10.1109/TDMR.2018.2839612

J. Guo, L. Zhu, W. Liu, H. Huang, S. Liu, T. Wang, L. Xiao, Z. Mao, Novel radiation-hardened-by-design (RHBD) 12T memory cell for aerospace applications in nanoscale CMOS technology. IEEE Trans. Very Large Scale Int. Syst. 25, 1593–1600 (2017). https://doi.org/10.1109/TVLSI.2016.2645282

S. Gupta, K. Gupta, N. Pandey, A 32-nm subthreshold 7T SRAM Bit cell with read assist. IEEE Trans. Very Large Scale Int. Syst. 25, 3473–3483 (2017). https://doi.org/10.1109/TVLSI.2017.2746683

S. Gupta, K. Gupta, N. Pandey, Pentavariate analysis of a subthreshold 10T SRAM Bit cell with variation tolerant write and divided bit-line read. IEEE Trans. Circuits Syst. I Regul. Pap. 65, 1–12 (2018). https://doi.org/10.1109/tcsi.2018.2813326

D. Ingerly, A. Agrawal, R. Ascazubi, A. Blattner, M. Buehler, V. Chikarmane, B. Choudhury, F. Cinnor, C. Ege, C. Ganpule, T. Glassman, R. Grover, P. Hentges, J. Hicks, D. Jones, A. Kandas, H. Khan, N. Lazo, K.S. Lee, H. Liu, A. Madhavan, R. McFadden, T. Mule, D. Parsons, P. Parthangal, S. Rangaraj, D. Rao, J. Roesler, A. Schmitz, M. Sharma, J. Shin, Y. Shusterman, N. Speer, P. Tiwari, G. Wang, P. Yashar, K. Mistry, Low-k interconnect stack with metal-insulator-metal capacitors for 22 nm high volume manufacturing, in 2012 IEEE Int. Interconnect Technol. Conf. (IITC), 2012. https://doi.org/10.1109/IITC.2012.6251663

D. Jeon, Q. Dong, Y. Kim, X. Wang, S. Chen, H. Yu, D. Blaauw, D. Sylvester, A 23-mW face recognition processor with mostly-read 5T Memory in 40-nm CMOS. IEEE J. Solid-State Circuits 52, 1628–1642 (2017). https://doi.org/10.1109/JSSC.2017.2661838

J.P. Kulkarni, K. Kim, K. Roy, A 160 mV robust schmitt trigger based subthreshold SRAM. IEEE J. Solid-State Circuits 42, 2303–2313 (2007). https://doi.org/10.1109/JSSC.2007.897148

C.B. Kushwah, S.K. Vishvakarma, A single-ended with dynamic feedback control 8T subthreshold SRAM cell. IEEE Trans. Very Large Scale Int. Syst. 24, 373–377 (2016). https://doi.org/10.1109/TVLSI.2015.2389891

K. Mehrabi, B. Ebrahimi, A. Afzali-Kusha, A robust and low power 7T SRAM cell design, in 18th CSI Int. Symp. Comput. Archit. Digit. Syst. (CADS) 2015. https://doi.org/10.1109/CADS.2015.7377782.

M. Moghaddam, S. Timarchi, M.H. Moaiyeri, M. Eshghi, An ultra-low-power 9T SRAM cell based on threshold voltage techniques. Circuits Syst. Signal Process. 35, 1437–1455 (2016). https://doi.org/10.1007/s00034-015-0119-0

B.S. Mohammad, H. Saleh, M. Ismail, Design methodologies for yield enhancement and power efficiency in SRAM-based SoCs. IEEE Trans. Very Large Scale Int. Syst. 23, 2054–2064 (2015). https://doi.org/10.1109/TVLSI.2014.2360319

M. Nabavi, M. Sachdev, A 290-mV, 3.34-MHz, 6T SRAM With pMOS access transistors and boosted Wordline in 65-nm CMOS technology. IEEE J. Solid-State Circuits. 35, 656–667 (2018). https://doi.org/10.1109/JSSC.2017.2747151

S. Naghizadeh, M. Gholami, Two novel ultra-low-power SRAM cells with separate read and write path. Circuits Syst. Signal Process. 38, 287–303 (2018)

Y. Nara, Scaling challenges of MOSFET for 32 nm node and beyond, in Int. Symp. VLSI Technol. Syst. Appl. Proc. 72–73 (2009). https://doi.org/10.1109/VTSA.2009.5159296

D. Nayak, D.P. Acharya, P.K. Rout, U. Nanda, A high stable 8T-SRAM with bit interleaving capability for minimization of soft error rate. Microelectron. J. 73, 43–51 (2018). https://doi.org/10.1016/j.mejo.2018.01.008

J. Park, Y. Yang, H. Jeong, S.C. Song, J. Wang, G. Yeap, S.O. Jung, Design of a 22-nm FinFET-based SRAM with read buffer for near-threshold voltage operation. IEEE Trans. Electron Devices 62, 1698–1704 (2015). https://doi.org/10.1109/TED.2015.2420681

G. Pasandi, S.M. Fakhraie, An 8t low-voltage and low-leakage half-selection disturb-free sram using bulk-cmos and FinFETs. IEEE Trans. Electron Devices 61, 2357–2363 (2014). https://doi.org/10.1109/TED.2014.2321295

G. Pasandi, M. Pedram, Internal write-back and read-before-write schemes to eliminate the disturbance to the half-selected cells in SRAMs. IET Circuits Devices Syst. 12, 460–466 (2018). https://doi.org/10.1049/iet-cds.2017.0227

Predictive Technology Model (PTM), (2007). http://ptm.asu.edu/

J. Rabaey, Low Power Design Essentials, 2009. https://doi.org/10.1007/978-0-387-71713-5

S. Ruchi, Dasgupta, Compact Analytical Model to Extract Write Static Noise Margin (WSNM) for SRAM Cell at 45-nm and 65-nm Nodes. IEEE Trans. Semicond. Manuf. 31, 136–143 (2018). https://doi.org/10.1109/TSM.2017.2772341

R. Saeidi, M. Sharifkhani, K. Hajsadeghi, A subthreshold symmetric SRAM cell with high read stability. IEEE Trans. Circuits Syst. II Express Briefs. 61, 26–30 (2014). https://doi.org/10.1109/TCSII.2013.2291064

V. Sharma, M. Gopal, P. Singh, S.K. Vishvakarma, S.S. Chouhan, A robust, ultra low-power, data-dependent-power-supplied 11T SRAM cell with expanded read/write stabilities for internet-of-things applications. Analog Int. Circuits Signal Process. 98, 331–346 (2019). https://doi.org/10.1007/s10470-018-1286-2

G. Torrens, B. Alorda, C. Carmona, D. Malagon-Perianez, J. Segura, S.A. Bota, A 65-nm reliable 6T CMOS SRAM cell with minimum size transistors. IEEE Trans. Emerg. Top. Comput. (2017). https://doi.org/10.1109/TETC.2017.2721932

C. Wang, D.-S. Wang, C.-H. Liao, S.-Y. Chen, A leakage compensation design for low supply voltage SRAM. IEEE Trans. Very Large Scale Integr. Syst. 24, 1761–1769 (2016)

Author information

Authors and Affiliations

Corresponding author

Additional information

Publisher's Note

Springer Nature remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

Rights and permissions

About this article

Cite this article

Shakouri, E., Ebrahimi, B., Eslami, N. et al. Single-Ended 10T SRAM Cell with High Yield and Low Standby Power. Circuits Syst Signal Process 40, 3479–3499 (2021). https://doi.org/10.1007/s00034-020-01636-y

Received:

Revised:

Accepted:

Published:

Issue Date:

DOI: https://doi.org/10.1007/s00034-020-01636-y