Abstract

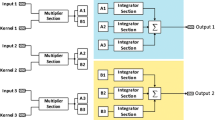

This article describes a project to design and build prototype analog early vision systems that are remarkably low-power, small, and fast. Three chips are described in detail. A continuous-time CMOS imager and processor chip uses a fully parallel 2-D resistive grid to find an object's position and orientation at 5000 frames/second, using only 30 milliwatts of power. A CMOS/CCD imager and processor chip does high-speed image smoothing and segmentation in a clocked, fully parallel 2-D array. And a chip that merges imperfect depth and slope data to produce an accurate depth map is under development in switched-capacitor CMOS technology.

Similar content being viewed by others

References

W. Yang and A.M. Chiang, A full fill-factor CCD imager with integrated signal processors, Proc. ISSCC, San Francisco, CA, pp. 218–219, February 1990.

W. Yang, The architecture and design of CCD processor for computer vision, Ph.D. thesis, Dept. Electrical Engineering and Computer Science, MIT, Cambridge, MA, August 1990.

W. Yang, Analog CCD processors for image filtering, SPIE Intern. Symp. on Opt. Eng. Photon. Aerospace Sensing, Orlando, FL, pp. 114–127, April 1991.

D.L. Standley, Analog VLSI implementation of smart vision sensors: Stability theory and an experimental design, Ph.D. thesis, Dept. Electrical Engineering and Computer Science, MIT, Cambridge, MA, P2, January 1991.

D.L. Standley and B.K.P. Horn, An object position and orientation IC with embedded imager, Proc. IEEE Intern. Solid-State Circuits Conf., San Francisco, CA, pp. 38–39, February 1991.

D.L. Standley, An object position and orientation IC with embedded imager, IEEE J. Solid-State Circ. 26(12): 1853–1859.

P.C., Yu, S.J., Decker, H.-S., Lee, C.G., Sodini, and J.L., Wyatt, Jr., CMOS resistive fuses for image smoothing and segmentation, IEEE J. Solid-State Circ. 27(4):545–553, April 1992.

P.C. Yu and H.-S. Lee, A CMOS resistive fuse processor for 2-D image acquisition, smoothing and segmentation, submitted to 1992 European Solid-State Circuits Conference, Copenhagen, Denmark.

C.L. Keast and C.G. Sodini, An integrated image acquisition, smoothing and segmentation focal plane processor, to appear in VLSI Circuit Symposium, Seattle, WA, June 1992.

C.L. Keast, An integrated image acquisition, smoothing and segmentation focal plane processor, Ph.D. Thesis, Department of Electrical Engineering and Computer Science, MIT, February 1992.

M. Hakkarainen, J. Little, H.-S. Lee, and J.L. Wyatt, Jr., Interaction of algorithm and implementation for analog VLSI stereo vision, SPIE Symp. Opt. Eng. Photon. Aerospace Sensing, Orlando, FL, pp. 173–184, April 1991.

J.L. Wyatt, Jr., C. Keast, M. Seidel, D. Standley, B. Horn, T. Knight, C. Sodini, H.-S. Lee, and T. Poggio, Analog VLSI systems for early vision processing, to appear in Proc. 1992 IEEE Intern. Symp. on Circuits and Systems, May 1992, San Diego, CA.

I.S. McQuirk, Direct methods for estimating the focus of expansion in analog VLSI, S.M. thesis, Department of Electrical Engineering and Computer Science, MIT, Cambridge, MA, September 1991.

C.L. Keast, and C.G. Sodini, A CCD/CMOS process for integrated image acquisition and early vision signal processing, Proc. SPIE Charge-Coupled Devices and Solid State Sensors, Santa Clara, CA, pp. 152–161, February 1990.

C.B. Umminger and C.G. Sodini, Switched capacitor networks for monolithic image processing systems, to appear in IEEE Trans. Circ. Syst.

C., Mead, Analog VLSI and Neural Systems. Addison-Wesley: Reading, MA, 1989.

B.K.P., Horn, Robot Vision, MIT Press: Cambridge, MA, and McGraw-Hill, New York, pp. 48–57, 1986.

B.K.P., Horn, Parallel networks for machine vision. In Research Directions in Computer Science: An MIT Perspective, A., Meyer, G.V., Guttag, R.L., Rivest, and P., Szolovits, eds., MIT Press: Cambridge, MA, pp. 531–572, 1991.

J.T., Wallmark, A new photocell using lateral photoeffect, Proc. Inst. Radio Engin., 45:474–483, April 1957.

S.P., DeWeerth and C.A., Mead, A two-dimensional visual tracking array, Advanced Research in VLSI, J., Allen and F.T., Leighton, eds., MIT Press: Cambridge, MA, pp. 259–275, 1988.

J.G., Harris, The coupled depth/slope approach to surface reconstruction, Technical Report TR-908, MIT AI Laboratory, Cambridge, MA, June 1986.

J., Harris, C., Koch, J., Luo, and J., Wyatt, Resistive fuses: Analog hardware for detecting discontinuities in early vision. In Analog VLSI Implementation of Neural Systems, C., Mead and M., Ismail, eds., Kluwer Academic, Norwell, MA, pp. 27–55, 1989.

J.G. Harris, Analog models for early vision, Ph.D. thesis, Cal Tech. Pasadena, CA, 1991.

J.G. Harris, Solving early vision problems with VLSI constraint networks. In Neural Architectures for Computer Vision, AAAI-88 Workshop, Minneapolis, MN, August 1988.

B. Horn, H.-S. Lee, C. Sodini, T. Poggio, and J. Wyatt, The first three years of the MIT vision chip project—Analog VLSI systems for integrated image acquisition and early vision processing, VLSI Memo No. 91-645, Microsystems Technology Laboratory, MIT, October 1991.

D., Marr and T., Poggio, Cooperative computation of stereo disparity, Science 194:283–287, October 1976.

M. Drumheller, and T. Poggio, On parallel stereo, Proc. IEEE Intern. Conf. Rob. Autom., San Francisco, 1986.

B.K.P., Horn and E.J., Weldon, Jr., Direct methods for recovering motion, Intern. J. Comput. Vis. 2(1):51–76, 1988.

L. Dron, The multi-scale veto model: A two-stage analog network for edge detection and image reconstruction, submitted to Intern. J. Comput. Vis.

A., Lumsdaine, J.L., Wyatt, Jr. and I.M., Elfadel, Nonlinear analog networks for image smoothing and segmentation, J. VLSI Sig. Proc. 3:53–68, 1991.

M.N. Seidel and J.L. Wyatt, Jr., Settling-time bounds for switched-capacitor networks, Proc. IMACS World cong. Comput. Appl. Math. Dublin, Ireland, pp. 1669–1670, July 1991.

Author information

Authors and Affiliations

Rights and permissions

About this article

Cite this article

Wyatt, J.L., Keast, C., Seidel, M. et al. Analog VLSI systems for image acquisition and fast early vision processing. Int J Comput Vision 8, 217–230 (1992). https://doi.org/10.1007/BF00055153

Issue Date:

DOI: https://doi.org/10.1007/BF00055153