Abstract

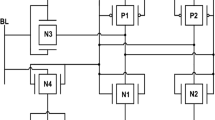

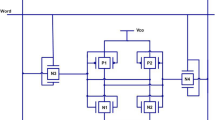

This article examines the development of a low power FINFET SRAM and applying different techniques to reduce leakage current. Due to scalability, the CMOS parameters are not providing reliable values at lower technology nodes. Researchers are looking for solutions to mitigate the negative consequences of MOSFET scaling, and FINFET has emerged as one of the best substitutes since it has better control over the gate and provide better performance parameters like it conserves less energy, eliminates short-channel effects, and reduces leakage current at sub-32 nm regime. Since the number of battery-powered portable devices has dramatically increased, electronic devices must be operated for longer time once the battery has charged. To achieve this the device should have less leakage current so that least amount of leakage power is possible which results in devices to operate for long periods of time. At first, a 6-T CMOS SRAM was designed, and all the parameters were calculated. Subsequently, DG-FINFET SRAM was developed, and all the parameters were calculated. The 6 T cell design based on FinFET consumes considerably less power than the 6 T SRAM designed by CMOS. Additionally, it features hold SNM and RSNM are better than the CMOS 6 T cell by 18% and 26% respectively. To reduce leakage current further in the FinFET SRAM many leakages current reduction techniques are applied and evaluated, which results MTCMOS technique reduced leakage current by 21.38%, SVL by 13.15%, AVL by 17.19% and proposed technique by 24.31%, which shows that the proposed technique has less leakage current than all the techniques discussed.

Similar content being viewed by others

Availability of Data and Material

Not Applicable.

Code Availability

Not Applicable.

References

Ieong, M., Narayanan, V., Singh, D., Topol, A., Chanand, V., & Ren, Z. (2006). Transistor Scaling with Novel Materials. Journal of Materials Today, 9(6), 26–31. https://doi.org/10.1016/S1369-7021(06)71540-1

Fallah, F., & Pedram, M. (2005). Standby and active leakage current control and minimization in CMOS VLSI Circuits. IEICE Transactions on Electronics, 88(4), 509–519. https://doi.org/10.1093/ietele/e88-c.4.509

Wong, H.-S.P. (2002). Beyond the Conventional Transistor. IBM Journal of Research and Development, 46(2/3), 133–168.

Kumar Gupta, S., Panagopoulos, G., & Roy, K. (2012). NBTI in n-Type SOI Access FinFETs in SRAMs and its impact on cell stability and performance. IEEE Transactions on Electron Devices, 59(10), 2603–2609.

Song, S. C., Abu-Rahman, M., & Yeap, G. (2011). FinFET based SRAM Bit cell design for 32 nm Node and below. Microelectronics Journal. https://doi.org/10.1016/j.mejo.2010.11.001

Limachia, M., & Kothari, N. (2020). Characterization of various FinFET based 6T SRAM cell configurations in light of radiation effect. Sadhana, 45(1), 1–7.

Wei Chiu, Y., Hao Hu, Y., Hsien Tu, M., Kai Zhao, J., Hua Chu, Y., Jye Jou, S., & Tec Huang, C. (2014). 40 nm Bit-Interleaving 12T Sub threshold SRAM with Data-Aware Write-Assist. IEEE Transactions on Circuits and Systems: Regular Papers, 61(9), 2578–2585.

Grossar, E., Stucchi, M., Maex, K., & Dehaene, W. (2006). Read stability and write-ability analysis of SRAM cells for nanometer technologies. IEEE Journal of Solid-State Circuits, 41(11), 2577–2588.

Akashe, S., & Sharma, S. (2013). Read write stability of Dual-VT 7T SRAM Cell at 45 nm technology. Journal of Computational and Theoretical Nano science, 10, 69–72. https://doi.org/10.1166/jctn.2013.2659

Song, S. C., Abu-Rahman, M., & Yeap, G. (2011). FinFET based SRAM Bit cell Design for 32 nm Node and below. Microelectronics Journal. https://doi.org/10.1016/j.mejo.2010.11.001

Islam, A., & Hasan, M. (2012). Variability aware low leakage reliable SRAM cell design technique. Journal of Microelectronics Reliability, 52(6), 1247–1252. https://doi.org/10.1016/j.microrel.2012.01.003

Rahman, A., Guo, J., Datta, S., & Lundstrom, M. S. (2003). Theory of ballistic nano transistors. IEE Transactions on Electron Devices, 50(10), 1853–1864. https://doi.org/10.1109/TED.2003.815366

Calhoun, B. H., & Chandrakasan, A. (2007). 256-kb65-nm Sub-Threshold SRAM design for ultra-low-voltage operation. IEEE Journal of Solid-State Circuits, 42(3), 680–688. https://doi.org/10.1109/JSSC.2006.891726

Hsieh, C.-Y., Fan, M.-L., Pi-Ho Hu, V., Su, P., & Te Chuang, C. (2012). Independently-controlled-gate finfet schmitt trigger sub-threshold SRAMs. IEEE Transactions on Very Large-Scale Integration Systems, 20(7), 1201–1210. https://doi.org/10.1109/TVLSI.2011.2156435

Hisamoto, D., Lee, W., Kedzierski, J., Takeuchi, H., Asano, K., Kuo, C., Anderson, E., et al. (2000). FinFET–a self- aligned double-gate MOSFET scalable to 20 nm. IEEE Transactions on Electron Devices, 47, 2320–2325. https://doi.org/10.1109/16.887014

Bin Kim, Y. (2010). Challenges for nanoscale MOSFETs and Emerging Nano electronics. IEEE Transactions on Electrical and Electronic Materials, 11(3), 93–105. https://doi.org/10.4313/TEEM.2010.11.3.093

Funding

Not Applicable.

Author information

Authors and Affiliations

Corresponding author

Ethics declarations

Conflict of Interest

The author has no conflicts of interest.

Additional information

Publisher's Note

Springer Nature remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

Rights and permissions

Springer Nature or its licensor (e.g. a society or other partner) holds exclusive rights to this article under a publishing agreement with the author(s) or other rightsholder(s); author self-archiving of the accepted manuscript version of this article is solely governed by the terms of such publishing agreement and applicable law.

About this article

Cite this article

Chandra, K.S., Kishore, K.H. Design and Analysis of Low Power FinFET SRAM with Leakage Current Reduction Techniques. Wireless Pers Commun 131, 1167–1188 (2023). https://doi.org/10.1007/s11277-023-10475-4

Accepted:

Published:

Issue Date:

DOI: https://doi.org/10.1007/s11277-023-10475-4