Abstract

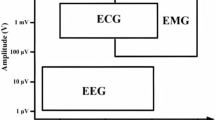

For extreme low-frequency (ELF) and super low-frequency (SLF) applications like biomedical applications (brain wave signal processing and brain–computer interface circuits), seismic signal processing applications, submarine communication applications, ultra-low-power dissipation of the electronic circuits is the most essential criterion. With the scaling of CMOS technology in the nanoscale, the contribution of leakage power becomes very significant compared to any other sources of power dissipation like switching power, bias power, etc. Subthreshold leakage current is an important component of all sources of leakage current. In modern design methodology for ultra-low-power analog circuits, this component of leakage current has been made use of for design purpose. The physics of the MOS transistor in the subthreshold region or weak inversion region is different from that when the transistor operates in the strong inversion region. Therefore, a good understanding of this physics is important for ultra-low-power design. Compact models play significant role in modern design methodologies. This chapter briefly discusses compact model for MOS transistor operating in the weak inversion region. Inversion coefficient-based design methodology for ultra-low-power analog circuits is discussed in detail. Implementation of the design methodology is then exemplified by a complete design of operational transconductance amplifier, operating in the extreme low-frequency region. Application areas of the design methodology are also discussed.

Access this chapter

Tax calculation will be finalised at checkout

Purchases are for personal use only

Similar content being viewed by others

References

Binkley DM (2008) Trade offs and Optimization in Analog CMOS Design. Wiley

Enz CC, Vittoz EA (2006) Charge-based MOS Transistor modeling: the EKV model for low-power and RF IC design. Wiley

Karimi-Bidhendi A et al (2017) CMOS Ultralow power brain signal acquisition front-ends: design and human testing. IEEE Trans Biomed Circuits Syst 11(5):1111–1122

Pandit S (2013) MOSFET characterization for VLSI circuit simulation. In: Sarkar C (ed) Technology computer aided design. CRC Press, Boca Raton. https://doi.org/10.1201/9781315216454

Pandit S (2018) Nanoscale silicon MOS Transistors. In: Roy S, Ghosh C, Sarkar C (eds) Nanotechnology. CRC Press, Boca Raton. https://doi.org/10.1201/9781315116730

Pandit S (2015) Nanoscale MOSFET: MOS transistor as basic building block. In: Sengupta A, Sarkar C (eds) Introduction to Nano. Engineering Materials, Springer, Berlin, Heidelberg

Pandit S, Mandal C, Patra A (2014) Nano-scale CMOS analog circuits. CRC Press, Boca Raton. https://doi.org/10.1201/9781315216102

Price C, Williams E, Elhalel G et al (2020) Natural ELF fields in the atmosphere and in living organisms. Int J Biometeorol. https://doi.org/10.1007/s00484-020-01864-6

Roy K, Mukhopadhyay S, Mahmoodi-Meimand H (2003) Leakage current mechanisms and leakage reduction techniques in deep-submicrometer CMOS circuits. Proc IEEE 91(2):305–327

Saha SK (2016) Compact models for integrated circuit design. CRC Press, Boca Raton. https://doi.org/10.1201/b19117

Tohidi M, Kargaard Madsen J, Moradi F (2019) Low-power high-input-impedance eeg signal acquisition SoC with fully integrated IA and signal-specific adc for wearable applications. IEEE Trans Biomed Circuits Syst 13(6):1437–1450

What are the spectrum band designators and bandwidths? https://www.nasa.gov/directorates/heo/scan/communications/outreach/funfacts/txt_band_designators.html

Acknowledgements

The author thanks the SMDP-C2SD project of the University of Calcutta, sponsored by MeitY, Govt. of India, for providing the necessary simulation resources which have been made use of for the work carried. The author expresses his deep gratitude to his student, Shri Rishov Aditya, B.Tech student of Netaji Subhash Engineering College, for carrying out many simulation experiments on this topic as part of his B. Tech project work. He further acknowledges the support provided by Dr. S. Sarkhel of the same institute for her support.

Author information

Authors and Affiliations

Corresponding author

Editor information

Editors and Affiliations

Rights and permissions

Copyright information

© 2020 Springer Nature Singapore Pte Ltd.

About this chapter

Cite this chapter

Pandit, S. (2020). Design Methodology for Ultra-Low-Power CMOS Analog Circuits for ELF-SLF Applications. In: Dhiman, R., Chandel, R. (eds) Nanoscale VLSI. Energy Systems in Electrical Engineering. Springer, Singapore. https://doi.org/10.1007/978-981-15-7937-0_2

Download citation

DOI: https://doi.org/10.1007/978-981-15-7937-0_2

Published:

Publisher Name: Springer, Singapore

Print ISBN: 978-981-15-7936-3

Online ISBN: 978-981-15-7937-0

eBook Packages: EngineeringEngineering (R0)