Abstract

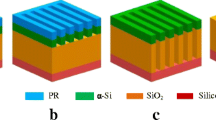

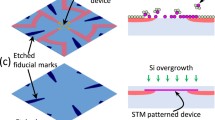

We present our recent developments on silicon technologies dedicated to the packaging of nano-objects/nano-devices. These technologies aim at both protecting and electrically connecting a nanoscale device positioned on a perfect Si(001)-(2 × 1):H surface smoothed thanks to a 950 °C thermal treatment. The nano-device is connected to nanopads implanted on the silicon surface. Each nanopad is linked to a nanovia which is locally achieved by etching and filling processes operated in a FIB (Focused Ion Beam) equipment. Impacts of the FIB process on via morphology and properties are depicted. Nanopads are fabricated through the local implantation of arsenic, and the effect of the surface smoothing thermal treatment on the dopants diffusion length is estimated by simulation and then experimentally explored. Key process steps such as the etching of a deep cavity and the surface protection with a temporary cap are also described, and a first assembly consisting in a substrate equipped with nanopads and directly bonded with a cap substrate is presented.

Access this chapter

Tax calculation will be finalised at checkout

Purchases are for personal use only

Similar content being viewed by others

References

Knickerbocker, J.U., Andry, P.S., Dang, B., Horton, R.R., Interrante, M.J., Patel, C.S., Polastre, R.J., Sakuma, K., Sirdeshmukh, R., Sprogis, E.J., Sri-Jayantha, S.M., Stephens, A.M., Topol, A.W., Tsang, C.K., Webb, B.C., Wright, S.L.: Three-dimensional silicon integration. IBM J. Res. Dev. 52(6), 553–569 (2008)

Garrou, P., Koyanagi, M., Ramm, P.: Handbook of 3D Integration. 3D Process Technology, vol. 3. Wiley, New York (2014)

Lau, J.H: Evolution, challenge, and outlook of TSV (through-silicon via) and 3D IC/Si integration. Keynote at IEEE Japan ICEP, 13–15 (2011)

Lau, J.H: Evolution, challenge, and outlook of TSV (through-silicon via) and 3D IC/Si integration. In: Proceedings of 2011 International Symposium on Advanced Packaging Materials (APM), pp. 462–488 (2011)

Gupta, A., Kannan, K., Kim, B., Mohammed, E., Ahn, B.: Development of novel carbon nanotube TSV technology. In: 2010 Electronic Components and Technology Conference, pp. 1699–1702 (2010)

Wang, T., Jeppson, K., Olofsson, N., Campbell, E., Liu, Y.: Through silicon vias filled with planarized carbon nanotube bundles. Nanotechnology 20, 485203 (2009). doi:10.1088/0957-4484/20/48/485203

Wang, T., Jeppson, K., Ye, L., Liu, Y.: Carbon-nanotube through-silicon via interconnects for three-dimensional integration. Small X(XX), 1–5 (2011)

Wang, T., Chen, S., Jiang, D., Fu, Y., Jeppson, K., Ye, L., Liu, L.: Through-silicon vias filled with densified and transferred carbon nanotube forests. IEEE Electron Device Lett. 33(3), 420–422 (2012)

Zhao, W.S., Yin, W.Y., Guo, Y.X.: Electromagnetic compatibility-oriented study on through silicon single-walled carbon nanotube bundle via (TS-SWCNTBV) arrays. IEEE Trans. Electromagn. Compat. 54(1), 149–157 (2012)

Xie, R., Zhang, C., Van der Veen, M.H., Arstila, K., Hantschel, T., Chen, B., Zhong, G., Robertson, J.: Carbon nanotube growth for through silicon via application. Nanotechnology 24,125603 (2013). doi:10.1088/0957-4484/24/12/125603

Morris, J.E. (ed.): Nanopackaging: nanotechnologies and electronics packaging. Springer, Berlin (2008)

Morris, J.E.: Nanotechnology materials for electronics reliability. In: 31st International Spring Seminar on Electronics Technology. ISSE’08, vol. C013, pp. 211–215 (2008)

Schwarzbauer, H., Kuhnert, R.: Novel large area joining technique for improved power device performance. In: Proceedings of Industry Applications Society Annual Meeting, vol. 2, pp. 1348–1351 (1989)

Zhang, Z.Z., Lu, G.Q.: Pressure-assisted low-temperature sintering of silver paste as an alternative die-attach solution to solder reflow. IEEE Trans. Electron. Packag. Manuf. 25(4), 279–283 (2002)

Bai, J.G., Zhang, Z.Z., Calata, J.N., Lu, G.Q.: Low-temperature sintered nanoscale silver as a novel semiconductor device-metallized substrate interconnect material. IEEE Trans. Compon. Packag. Technol. 29(3), 589–593 (2006)

Göbl, C., Faltenbacher, J.: Low temperature sinter technology die attachment for power electronic applications. In: Proceedings of CIPS 2010, 16–18 March 2010, Nuremberg/Germany, Paper 10.1 (2010)

Lei, T.G., Calata, J.N., Lu, G.Q., Chen, X., Luo, S.: Low-temperature sintering of nanoscale silver paste for attaching large-area (>100 mm2) chips. IEEE Trans. Compon. Packag. Technol. 33(1), 98–104 (2010)

Zheng, H., Berry, D., Calata, J.N., Ngo, K.D.T., Luo, S., Lu, G.Q.: Low-pressure joining of large-area devices on copper using nanosilver paste. IEEE Trans. Compon. Packag. Manuf. Technol. 3(6), 915–922 (2013)

Ishida, H., Ogashiwa, T., Yazaki, T., Ikoma, T., Nishimori, T., Kusamori, H., Mizuno, J.: Low-temperature wafer bonding for MEMS hermetic packaging using sub-micron Au particles. Trans. Jpn. Inst. Electron. Packag. 3(1), 62–67 (2010)

Joachim, C. (ed.): Atomic Scale Interconnection Machines. Advances in Atom and Single Molecule Machines. Springer, Berlin (2012)

Lwin, M.H.T., Tun, T.N., Kim, H.H., Kajen, R.S., Chandrasekhar, N., Joachim, C.: Silicon on insulator nanoscale backside interconnects for atomic and molecular scale circuits. J. Vac. Sci. Technol., B 28, 978–984 (2010). doi:10.1116/1.3484248

Le Gac, G., Audoit, G., Thuaire, A., Moriceau, H., Baillin, X.: Nanovias FIB-etching and filling in a micro-nano interposer for molecular electronics. In: Technical Proceedings of the 2012 NSTI Nanotechnology Conference and Expo, NSTI-Nanotech 2012, vol. 2, p. 539 (2012)

Niklaus, F., Stemme, G., Lu, J.-Q., Gutmann, R.J.: Adhesive wafer bonding. J. Appl. Phys. 99, 031101 (2006). doi:10.1063/1.2168512

Hartmann, J.M., Loup, V., Rolland, G., Holliger, P., Laugier, F., Vannuffel, C., Séméria, M.-N.: SiGe growth kinetics and doping in reduced pressure-chemical vapor deposition. J. Cryst. Growth 236, 10–20 (2002)

Kolmer, M., Godlewski, S., Zuzak, R., Wojtaszek, M., Rauer, C., Thuaire, A., Hartmann, J.M., Moriceau, H., Joachim, C., Szymonski, M.: Atomic scale fabrication of dangling bond structures on hydrogen passivated Si(0 0 1) wafers processed and nanopackaged in a clean room environment. Appl. Surf. Sci. 288, 83–89 (2014)

Rauer, C., Rieutord, F., Hartmann, J.M., Charvet, A.-M., Fournel, F., Mariolle, D., Morales, C., Moriceau, H.: Hydrophobic direct bonding of silicon reconstructed surfaces. Microsyst. Technol. 19, 675–679 (2013)

Acknowledgments

This work was supported by the European Community (AtMol project) under grant agreement No 270028.

Author information

Authors and Affiliations

Corresponding author

Editor information

Editors and Affiliations

Rights and permissions

Copyright information

© 2015 Springer International Publishing Switzerland

About this paper

Cite this paper

Thuaire, A. et al. (2015). Silicon Technologies for Nanoscale Device Packaging . In: Baillin, X., Joachim, C., Poupon, G. (eds) Nanopackaging: From Nanomaterials to the Atomic Scale. Advances in Atom and Single Molecule Machines. Springer, Cham. https://doi.org/10.1007/978-3-319-21194-7_8

Download citation

DOI: https://doi.org/10.1007/978-3-319-21194-7_8

Published:

Publisher Name: Springer, Cham

Print ISBN: 978-3-319-21193-0

Online ISBN: 978-3-319-21194-7

eBook Packages: Chemistry and Materials ScienceChemistry and Material Science (R0)