Abstract

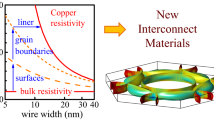

This chapter covers integration, performance, and three main process sectors concerning back-end-of-line (BEOL) wiring (“interconnect”) process technology: intralevel dielectrics (ILDs), thin-film metals used in thin-film processing, and dielectric capping layers. The integration section contains an overview of patterning schemes used in damascene wiring fabrication and covers developments up to current leading-edge schemes which use extreme ultraviolet (EUV) lithography. Performance considerations are also discussed in Sect. 5.1, with a focus on BEOL metrics such as resistance and capacitance. The dielectric section reviews the history of materials used as BEOL damascene dielectrics and covers the history of low-dielectric constant (“low-k”) materials as well as recent trends concerning air gap and porous dielectrics. The thin-film metals cover developments in physical vapor deposition (PVD) tooling and processes as well as chemical vapor deposition (CVD) wetting and cap layers. In the final section, modern trends in dielectric and selective metal caps are covered.

Access this chapter

Tax calculation will be finalised at checkout

Purchases are for personal use only

Similar content being viewed by others

References

Edelstein, D.C.: On-Chip ULSI Interconnect Technology, its Extendibility, and Integrated Devices. Columbia University Short Course (2017)

Chen, S.-T., Tomizawa, K., Tsumura, M., Tagami, H., Shobha, M., Van Sankarapandian, O., der Straten, J., Kelly, D., Canaperi, T., Levin, S., Cohen, Y., Yin, D., Horak, M., Ishikawa, Y., Mignot, C.-S., Koay, S., Burns, S., Halle, H., Kato, G., Landie, Y., Xu, A., Scaduto, E., Mclellan, J.C., Arnold, M., Colburn, T., Usui, T.: Spooner, 64 nm pitch Cu dual-damascene interconnects using pitch split double exposure patterning scheme. In: 2011 IEEE International Interconnect Technology Conference and 2011 Materials for Advanced Metallization, IITC/MAM, vol. 2011, pp. 1–3 (2011). https://doi.org/10.1109/IITC.2011.5940273

Burkhardt, M., Arnold, J.C., Baum, Z., Burns, S., Chang, J., Chen, J., Cho, J., Dai, V., Deng, Y., Halle, S., Han, G., Holmes, S., Horak, D., Kanakasabapathy, S., Kim, R.H., Klatchko, A., Koay, C.S., Krasnoperova, A., Ma, Y., McLellan, E., Petrillo, K., Schmitz, S., Tabery, C., Yin, Y., Zhuang, L., Zou, Y., Kye, J., Paruchuri, V., Mansfield, S., Spence, C., Colburn, M.: Overcoming the challenges of 22-nm node patterning through litho-design co-optimization. In: Proc. SPIE 7274, Optical Microlithography XXII, 727404 (2009). https:/978-3-030-79827-7/doi.org/10.1117/12.814433

Holmes, S.J., Tang, C., Arnold, J.C., Yin, Y., Chen, R., Fender, N., Osborn, B., Dabbagh, G., Liu, S., Colburn, M., Varanasi, R.P., Slezak, M.: Process characterization of pitch-split resist materials for application at 16nm node. In: Proc. SPIE 7639, Advances in Resist Materials and Processing Technology XXVII, 76392X (2010). https://doi.org/10.1117/12.846891

Koay, C.-S., Holmes, S., Petrillo, K., Colburn, M., Burns, S., Dunn, S., Cantone, J., Hetzer, D., Kawakami, S., van Dommelen, Y., Jiang, A., Many, M., Routh, R., Huli, L., Martinick, B., Rodgers, M., Tomizawa, H., Kini, S.: Evaluation of double-patterning techniques for advanced logic nodes. In: Proc. SPIE 7640, Optical Microlithography XXIII, 764009 (2010). https://doi.org/10.1117/12.846769

Yunpeng Yin, John C. Arnold, Matthew Colburn, Sean Burns, Steven Holmes, Chiew-seng Koay; Ryoung-han Kim; Guillaume Landie; Dave Horak; Yann Mignot; Hideyuki Tomizawa, “BEOL double patterning: challenges for etch” in AVS Conference Proceedings, PS-MoM-5 (2010)

Tomizawa, H., Chen, S.T., Horak, D., Kato, H., Yin, Y., Ishikawa, M., Kelly, J., Koay, C.S., Landie, G., Burns, S., Tsumura, K., Tagami, M., Shobha, H., Sankarapandian, M., van der Straten, O., Maniscalco, J., Vo, T., Arnold, J., Colburn, M., Usui, T., Spooner, T.: Robust self-aligned via process for 64nm pitch Dual-Damascene interconnects using pitch split double exposure patterning scheme. In: 2011 IEEE International Interconnect Technology Conference, pp. 1–3 (2011). https://doi.org/10.1109/IITC.2011.5940305

Chen, S.-T., Kim, T.-S., Nam, S.-w., Lafferty, N., Koay, C.-S., Saulnier, N., Wang, W., Yongan, X., Duclaux, B., Mignot, Y., Beard, M., Yin, Y., Shobha, H., Van der Straten, O., He, M., Kelly, J., Colburn, M., Spooner, T.: 48 nm Pitch cu dual-damascene interconnects using self-aligned double patterning scheme. In: 2013 IEEE International Interconnect Technology Conference - IITC, pp. 1–3 (2013). https://doi.org/10.1109/IITC.2013.6615589

Fuchs, K.: The conductivity of thin metallic films according to the electron theory of metals. Math. Proc. Camb. Philos. Soc. 34(1), 100–108 (1938)

Sondheimer, E.H.: The mean free path of electrons in metals. Adv. Phys. 1(1), 1–42 (1952)

Mayadas, A.F., Shatzkes, M.: Electrical-resistivity model for polycrystalline films: the case of arbitrary reflection at external surfaces. Phys. Rev. B. 1(4), 1382–1389 (1970)

Smith, R.S., Ryan, E.T., Hu, C.-K., Motoyama, K., Lanzillo, N., Metzler, D., Jiang, L., Demarest, J., Quon, R., Gignac, L., Breslin, C., Giannetta, A., Wright, S.: An evaluation of Fuchs-Sondheimer and Mayadas-Shatzkes models below 14nm node wide lines. AIP Adv. 9(2), 025015 (2019)

Lanzillo, N.A., Motoyama, K., Hook, T., Clevenger, L.: Impact of line and via resistance on device performance at the 5 nm gate all around node and beyond. In: 2018 IEEE International Interconnect Technology Conference (IITC), pp. 70–72 (2018). https://doi.org/10.1109/IITC.2018.8430294

Prasad, D., Naeemi, A.: Interconnect design and technology optimization for conventional and emerging nanoscale devices: a physical design perspective. In: 2018 IEEE International Electron Devices Meeting (IEDM) (2018)

Hu, C.-K., Kelly, J., Chen, J., Huang, H., Ostrovski, Y., Patlolla, R., Peethala, B., Adusumilli, P., Spooner, T., Gignac, L., Bruley, J., Breslin, C., Cohen, S., Lian, G., Ali, M., Long, R., Hornicek, G., Kane, T., Kamineni, V., Zhang, X., Mont, F., Siddiqui, S.: Electromigration and resistivity in on-chip Cu, Co and Ru damascene nanowires. In: 2017 IEEE International Interconnect Technology Conference (IITC), pp. 1–3 (2017). https://doi.org/10.1109/IITC-AMC.2017.7968977

Hu, C.-K., Kelly, J., Huang, H., Motoyama, K., Shobha, H., Ostrovski, Y., Chen, J., Patlolla, R., Peethala, B., Adusumilli, P., Spooner, T., Quon, R., Gignac, L., Breslin, C., Lian, G., Ali, M., Benedict, J., Lin, X., Smith, S., Kamineni, V., Zhang, X., Mont, F., Siddiqui, S., Baumann, F.: Future on-chip interconnect metallization and electromigration. In: 2018 IEEE International Reliability Physics Symposium (IRPS), pp. 4F.1-1–4F.1-6 (2018). https://doi.org/10.1109/IRPS.2018.8353597

Lojek, B.: History of Semiconductor Engineering, pp. 321–323. Springer Science & Business Media (2007). ISBN 9783540342588. and Electronics Magazine, 38(8) (1965)

Grill, A.: In: Baklanov, M., Green, M., Maex, K. (eds.) Chapter 1 in Dielectric Films for Advanced Microelectronics. John Wiley & Sons, West Sussex (2007)

Crowder, S., Greco, S., Ng, H., Barth, E., Beyer, K., Biery, G., Connolly, J., DeWan, C., Ferguson, R., Chen, X., Hargrove, M., Nowak, E., McLaughlin, P., Purtell, R., Logan, R., Oberschmidt, J., Ray, A., Ryan, D., Tallman, K., Wagner, T., McGahay, V., Crabbe, E., Agnello, P., Goldblatt, R., Su, L., Davari, B.: Digest of Technical Papers 1999 Symposium on VLSI Technology, 105 (1999)

Leobandung, E., Barth, E., Sherony, M., Lo, S.-H., Schulz, R., Chu, W., Khare, M., Sadana, D., Schepis, D., Boiam, R., Sleight, I., White, F., Assaderaghi, F., Moy, D., Biery, G., Goldblatt, R., Chen, T.-C., Davari, B., Shahidi, G.: High performance 0.18 /spl mu/m SOI CMOS technology. In: International Electron Devices Meeting 1999. Technical Digest (Cat. No.99CH36318), pp. 679–682 (1999). https://doi.org/10.1109/IEDM.1999.824243

Grill, A., Perraud, L., Patel, V., Jahnes, C., Cohen, S.: Mat. Res. Soc. Symp. Proc. 565, 107 (1999)

Donaton, R.A., Struyf, H.L., Coenegrachts, M., Stucchi, B., de Roest, M., Baklanov, D., Vanhaelemeersch, M., Maex, S., Gaillard, K., Xia, F., Lim, L.Q., Gotuaco, T.H., Yieh, M., Van Autryve, E.: Luc., Conf. Proc. ULSI VXI, 595 (MRS, Warrendale, PA) (2001)

Thompson, S., Anand, N., Armstrong, M., Auth, C., Arcot, B., Alavi, M., Bai, P., Bielefeld, J., Bigwood, R., Brandenburg, J., Buehler, M., Cea, S., Chikarmane, V., Choi, C., Frankovic, R., Ghani, T., Glass, G., Han, W., Hoffmann, T., Hussein, M., Jacob, P., Jain, A., Jan, C., Joshi, S., Kenyon, C., KlausS, J., Klopcic, J., Luce, Z., Ma, B., Mcintyre, K., Mistry, A., Murthy, P., Nguyen, H., Pearson, T., Sandford, R., Schweinfurth, R., Shaheed, S., Sivakumar, M., Taylor, B., Tufts, C., Wallace, P., Wang, C., Weber, M.: A 90 nm logic technology featuring 50 nm strained silicon channel transistors, 7 layers of Cu interconnects, low-k ILD, and 1 /spl mu/m/sup 2/ SRAM cell. In: Digest. International Electron Devices Meeting, pp. 61–64 (2002). https://doi.org/10.1109/IEDM.2002.1175779

Matsuura, M., Nishioka, Y., Matsumoto, S., Goto, K.,Satake, T., Yuasa, H., Okazaki, G., Tomita, K., Hashimoto, K., Tomohisa, S., Yamashita, T., Fukada, T., Ohsaki, A.: Conf. Proc. ULSI XVIII, 493 (MRS, Warrendale, PA) (2003)

Edelstein, D., Davis, C., Clevenger, L., Yoon, M., Cowley, A., Nogami, T., Rathore, H., Agarwala, B., Arai, S., Carbone, A., Chanda, K., Cohen, S., Cote, W., Cullinan, M., Dalton, T., Das, S., Davis, P., Demarest, J., Dunn, D., Dziobkowski, C., Filippi, R., Fitzsimmons, J., Flaitz, P., Gates, S., Gill, J., Grill, A., Hawken, D., Ida, K., Klaus, D., Klymko, N., Lane, M., Lane, S., Lee, J., Landers, W., Li, W.-K., Lin, Y.-H., Liniger, E., Liu, X.-H., Madan, A., Malhotra, S., Martin, J., Molis, S., Muzzy, C., Nguyen, D., Nguyen, S., Ono, M., Parks, C., Questad, D., Restaino, D., Sakamoto, A., Shaw, T., Shimooka, Y., Simon, A., Simonyi, E., Tempest, S., Van Kleeck, T., Vogt, S., Wang, Y.-Y., Wille, W., Wright, J., Yang, C.-C., Ivers, T.: Proceedings of the IEEE 2004 Intern. In: Interconnect Technol. Conf, vol. 214, (2004)

Ruelke, H., Huebler, P., Streck, C., Gotuaco, M., Senninger, W.: Solid State Technol. 47(1), 60 (2004)

Jan, C.-H., Anand, N., Allen, C., Bielefeld, J., Buehler, M., Chikamane, V., Fischer, K., Jain, A., Jeong, J., Klopcic, S., Marieb, T., Miner, B., Nguyen, P., Schmitz, A., Nashner, M., Scherban, T., Schroeder, B., Ward, C., Wu, R., Zawadzki, K., Thompson, S., Bohr, M.: Proceedings of the IEEE 2004 Intern. In: Interconnect Technol. Conf, vol. 205, (2004)

Grill, A.: Low and ultralow dielectric constant films prepared by plasma enhanced chemical vapor deposition. In: Baklanov, M., Green, M., Maex, K. (eds.) Dielectric Films for Advanced Microelectronics, p. 1. Wiley (2007)

Dubois, G., Miller, R.D., Volksen, W.: Spin-on dielectric materials. In: Baklanov, M., Green, M., Maex, K. (eds.) Dielectric Films for Advanced Microelectronics, p. 33. Wiley (2007)

McGahay, V.: Porous dielectrics in microelectronic: wiring applications. Materials. 3, 536 (2010)

List, R., Singh, A., Ralston, A., Dixit, G.: MRS Bull. 10, 61 (1997)

Iacopi, F., Brongersma, S., Vandevelde, B., O’Toole, M., Degryse, D., Travaly, Y., Maex, K.: Microelectron. Eng. 75, 54 (2004)

Garner, M., Kloster, G., Atwood, G., Mosley, L., Palanduz, A.: Microelectron. Eng. 45, 919 (2005)

Moore, D., Carter, R., Cui, H., Burke, P., McGrath, P., Gu, S., Gidley, D., Peng, H.: J. Vac. Sci. Technol. B. 23, 332 (2005)

Baklanov, M., de Marneffe, J., Shamiryan, D., Urbanowicz, A., Shi, H., Rakhimova, T., Huang, H., Ho, P.: J. Appl. Phys. 113, 041101 (2013)

Sankaran, S., Arai, S., Augur, R., Beck, M., Biery, G., Bolom, T., Bonilla, G., Bravo, O., Chanda, K., Chae, M., Chen, F., Clevenger, L., Cohen, S., Cowley, A., Davis, P., Demarest, J., Doyle, J., Dimitrakopoulos, C., Economikos, L., Edelstein, D., Farooq, M., Filippi, R., Fitzsimmons, J., Fuller, N., Gates, S.M., Greco, S.E., Grill, A., Grunow, S., Hannon, R., Ida, K., Jung, D., Kaltalioglu, E., Kelling, M., Ko, T., Kumar, K., Labelle, C., Landis, H., Lane, M.W., Landers, W., Lee, M., Li, W., Liniger, E., Liu, X., Lloyd, J.R., Liu, W., Lustig, N., Malone, K., Marokkey, S., Matusiewicz, G., McLaughlin, P.S., McLaughlin, P.V., Mehta, S., Melville, I., Miyata, K., Moon, B., Nitta, S., Nguyen, D., Nicholson, L., Nielsen, D., Ong, P., Patel, K., Patel, V., Park, W., Pellerin, J., Ponoth, S., Petrarca, K., Rath, D., Restaino, D., Rhee, S., Ryan, E.T., Shoba, H., Simon, A., Simonyi, E., Shaw, T.M., Spooner, T., Standaert, T., Sucharitaves, J., Tian, C., Wendt, H., Werking, J., Widodo, J., Wiggins, L., Wisnieff, R., Ivers, T.: A 45 nm CMOS node Cu/Low-k/Ultra Low-k PECVD SiCOH (k = 2.4) BEOL technology. In: 2006 International Electron Devices Meeting, pp. 1–4 (2006). https://doi.org/10.1109/IEDM.2006.346782

Grill, A.: PECVD low and ultralow dielectric constant materials: From invention and research to products. J. Vac. Sci. Technol. 34, 020801 (2016). https://doi.org/10.1116/1.4943049

Jousseaume, V., El Sabahy, J., Yeromonahos, C., Castellan, G., Bouamrani, A., Ricoul, F.: Microelectron. Eng. 167, 69–79 (2017)

Grill, A., Gates, S.M., Ryan, T.E., Nguyen, S.V., Priyadarshini, D.: Progress in the development and understanding of advanced low k and ultralow k dielectrics for very large-scale integrated interconnects—State of the art. Appl. Phys. Rev. 1, 011306 (2014). https://doi.org/10.1063/1.4861876

You, H., Mennell, P., Shoudy, M., Sil, D., Dorman, D., Cohen, S., Liniger, E., Shaw, T., Leo, T.-L., Canaperi, D., Raymond, M., Madan, A.: Alfred grill. J. Vac. Sci. Technol. B. 36, 012202 (2018). https://doi.org/10.1116/1.5007177

Priyadarshini, D., Nguyen, S.V., Shobha, H., Liniger, E., Grill, A.: J. Vac. Sci. Technol. B. 35, 021201 (2017). https://doi.org/10.1116/1.497431726

Van Nguyen, S.: J. Vac. Sci. Technol. 4, 1159 (1986). https://doi.org/10.1116/1.583476

Cote, D.R., Nguyen, S.V., Stamper, A.K., Armbrust, D.S., Tobben, D., Conti, R.A., Lee, G.Y.: IBM J. Res. Dev. 43(12), 5–38 (1999). https://doi.org/10.1147/rd.431.0005

Van Nguyen, S.: IBM J. Res. Dev. 43(12), 109–126 (1999)

Nguyen, S.V., Underhill, J., Fridmann, S., Pan, P.: J. Electrochem. Soc. 132, 1925–1932 (1985)

Lubguban Jr., J., Rajagopalan, T., Mehta, N., Lahlouh, B., Simon, S.L.: Gangopadhyaya. J. Appl. Phys. 92, 1033–1038 (2002)

Gates, S., Neumayer, D., Sherwood, M.H., Grill, A., Wang, X., Sankarapandian, M.: J. Appl. Phys. 101, 094103-1–094103-8 (2007)

Grill, A.: J. Vac. Sci. Technol. B. 34, 020801 (2016). https://doi.org/10.1116/1.4943049

Ming, Z., Beichao, Z.: Mater. Sci. Semicond. Process. 36, 170–178 (2015)

Grill, A.: Ann. Rev. Mater. Res. 39, 49 (2009)

Grill, A., Patel, V.: Appl. Phys. Lett. 79(6), 803 (2001)

Nguyen, S., McGahay, V., Sherwood, M., Klymko, N., Cohen, S., Simonyi, E., Grill, A., Shobha, H., Restaino, D., Lane, S., Molis, S., Malone, K., Liniger, E., Patel, V., Gates, S., Edelstein, D., Mehta, S., Ivers, T.: The Electrochemical Society Fall 2008 Meeting. Honolulu, Hawaii (2008)., paper 2076. http://ma.ecsdl.org/content/MA200802/28/2076.full.pdf+html

Grill, A., Edelstein, D., Lane, M., Patel, V., Gates, S., Restaino, D., Molis, S.: J. Appl. Phys. 103, 0541042008 (2018). https://doi.org/10.1063/1.2844483

Grill, A., Gates, S., Nguyen, S., Priyadarshini, E.D.: Appl. Phys. Rev. 1, 011306 (2014). https://doi.org/10.1063/1.4861876

Urbanowicz, A.M., Vanstreels, K., Verdonck, P., Shamiryan, D., De Gendt, S., Baklanov, M.R.: J. Appl. Phys. 107, 104122 (2010). https://doi.org/10.1063/1.3428958. and Electrochemical and Solid-State Letters, 12 _8_ H292-H295 _2009. 10.1149/1.3139741

Marsik, P., Urbanowicz, A.M., Verdonck, P., De Roest, D., Sprey, H., Baklanov, M.R.: Effect of ultraviolet curing wavelength on low-k dielectric material properties and plasma damage resistance. Thin Solid Films. 519(11), 3619–3626 (2011). https://doi.org/10.1016/j.tsf.2011.01.339

Vanstreels, K., Ciofi, I., Barbarin, Y., Baklanov, M.: J. Vac. Sci. Technol. B. 31, 050604 (2013). https://doi.org/10.1116/1.4818128

Ryan, E.T., Gates, S.M., Grill, A., Molis, S., Flaitz, P., Arnold, J., Sankarapandian, M., Cohen, S.A., Ostrovski, Y., Dimitrakopoulos, C.: J. Appl. Phys. 104, 094109 (2008)

Standaert, T., Beique, G., Chen, H.-C., Chen, S.-T., Hamieh, B., Lee, J., McLaughlin, P., McMahon, J., Mignot, Y., Mont, F., Motoyama, K., Nguyen, S., Patlolla, R., Peethala, B., Priyadarshini, D., Rizzolo, M., Saulnier, N., Shobha, H., Siddiqui, S., Spooner, T., Tang, H., van der Straten, O., Verduijn, E., Xu, Y., Zhang, X., Arnold, J., Canaperi, D., Colburn, M., Edelstein, D., Paruchuri, V., Bonilla, G.: Invited Paper 2.1, Interconnect Technology Conference/Advanced Metallization Conference (IITC/AMC), May 23–26, 2016, IEEE International, San Jose, California, USA (2016). https://doi.org/10.1109/IITC-AMC.2016.7507636

Briggs, B.D., Peethala, C.B., Rath, D.L., Lee, J., Nguyen, S., LiCausi, N.V., McLaughlin, P.S., et al.: International Interconnect Technology Conference June 4–7, 2018. In: Paper 11.2, Proceeding IITC, San Jose, California, USA (2018). https://doi.org/10.1109/IITC.2018.8430476

Sil, D., Gluschenkov, O., Sulehria, Y., Durrant, D., Huang, H., Lanzillo, N., Shobha, H., O’Haller, N., Yao, Y., Sunder, M., Thomas, C.R., Lee, J., Shoudy, M., Nguyen, S., Nogami, T., Peethala, C.B., Haran, B., Liu, J., Halty, S., Mazzamuto, F.: International Interconnect Technology Conference June 3-6, 2019. In: Proceeding IITC paper p6.4, Brussel, Belgium (2019)

Ahn, S.H., Yim, T.-J., Baek, J., Hwang, K.: International Interconnect Technology Conference, June 3–6, 2019. In: Proceeding IITC paper 6.1, Brussel, Belgium (2019)

Nitta, S., Ponoth, S., Breyetta, G., Colburn, M., Clevenger, L., Horak, D.: Advanced metallization conference 2007. In: MRS Proceeding, p. 329 (2007)

Edelstein, D.: Invited paper. IEEE Workshop on Microelectronics and Electron Devices, April 3, 2009, Boise. Slide and https://www.technologyreview.com/2007/05/03/225611/self-assembly-to-make-faster-chips/ and https://www.ewh.ieee.org/r6/boise/wmed2009/WMED2009_Invited_Edelstein.pdf

Chen, H.-W.: Proceedings of the 11th IITC, p. 34, Burlingame, CA, June 1–4 (2008)

Prasad, D., Ceyhan, A., Pan, C., Naeemi, A.: IEEE Trans. Electron Dev. 62(12), 3938 (2015)

Fischer, K., Chang, H.K., Ingerly, D., Jin, I., Kilambi, H., Longun, J., Patel, R., Pelto, C., Petersburg, C., Plekhanov, P., Puls, C., Rockford, L., Tsameret, I., Uncuer, M., Yashar, P.: International Interconnect Technology Conference, Proceeding, p 5, San Jose, California USA (2016)

Penny, C., Gates, S., Peethala, B., Lee, J., Priyadarshini, D., Nguyen, S.V., McLaughlin, P., Liniger, E., Hu, C.-K., Clevenger, L., Hook, T., Shobha, H., Kerber, P., Seshadri, I., Chen, J., Edelstein, D., Quon, R., Bonilla, G., Paruchuri, V., Huang, E.: International Interconnect Technology Conference, Proceed. Volume, paper 2.2, May 16–18, Taipei, Taiwan (2017)

International technology roadmap for semiconductor, 2015, Editions, p28. https://www.dropbox.com/sh/3jfh5fq634b5yqu/AADYT8V2Nj5bX6C5q764kUg4a?dl=0&preview=5_2015+ITRS+2.0_More+Moore.pdf

Son Nguyen, T., Haigh, K., Cheng, C., Penny, C., Park, J., Li, S., Mehta, T., Yamashita, L.J., Canaperi, D.: ECS J. Solid State Sci. Technol. 7(10), 588–594 (2018). https://doi.org/10.1149/2.0021811jss

Nogami, T., Huang, H., Shobha, H., Patlolla, R., Kelly, J., Penny, C., Hu, C.-K., Sil, D., DeVries, S., Lee, J., Nguyen, S., Jiang, L., Demarest, J., Li, J., Lian, G., Ali, M., Bhosale, P., Lanzillo, N., Motoyama, K., Lian, S., Standaert, T., Bonilla, G., Edelstein, D., Haran, B.: Technology challenges and enablers to extend Cu metallization to beyond 7 nm node. In: 2019 Symposium on VLSI Technology, Kyoto, Japan, pp. T18–T19 (2019). https://doi.org/10.23919/VLSIT.2019.8776573, and The Electrochemical Society Spring May 2020 meeting in Montreal, Canada, ECS Meeting Abstracts, Volume MA2020-01

Liu, X.H.: Paper 3.1, Conference: 2017 IEEE International Interconnect Technology Conference (IITC)

Spooner, T.A., Arnold, J.C., Canaperi, D., Chen, H.-C., Chen, S.-T., Gates, S.M., Isobayashi, A., Leung, P., Rao, S.S.P., Sankarapandian, M., Shobha, H., van der Straten, O.: ECS Trans. 25(7), 279–289 (2009)

Van Nguyen, S., Shobha, T., Haigh, J., Chen, J., Lee, T., Nogami, E.L., Cohen, S., Hu, C.K., Huang, H., Yao, Y., Canaperi, D., Peethala, B., Standaert, T., Bonilla, G.: Novel low-k Dielectric materials for nano device interconnect technology. In: 2020 International Symposium on VLSI Technology, Systems and Applications (VLSI-TSA), pp. 117–118 (2020). https://doi.org/10.1109/VLSI-TSA48913.2020.9203631

Hong, S., Lee, C.-S., Lee, M.-H., Lee, Y., Kyung Yeol, M.A., Kim, G., In Yoon, S., Ihm, K., Kim, K.-J., Shin, T.J., Kim, S.W., Jeon, E.-c., Jeon, H., Kim, J.-Y., Lee, H.-I., Lee, Z., Antidormi, A., Roche, S., Chhowalla, M., Shin, H.-J., Shin, H.S.: Nature. 582, 511–516 (2020). https://doi.org/10.1038/s41586-020-2375-9

Nguyen, S., Nguyen, T., Dbuzinsky, D.: Appl. Phys. Lett. 63, 2103 (1993). https://doi.org/10.1063/1.110579

Nguyen, S., Nguyen, T., Treichel, H., Spindler, O.: J. Electrochem. Soc. 141(6), 1633–1638 (1994)

Cote, D., Nguyen, S., Dobuzinsky, D., Basa, C., Neureither, B.: Proc. SPIE 2091. In: Microelectronic Processes, Sensors, and Controls (1994). https://doi.org/10.1117/12.167340

Edelstein, D., Uzoh, C., Cabral, C., DeHaven, P., Buchwalter, P., Simon, A., Cooney, E., Malhotra, S., Klaus, D., Rathore, H., Agarwala, B., Nguyen, D.: A high performance liner for copper damascene interconnects. In: Proceedings of the IEEE 2001 International Interconnect Technology Conference (Cat. No.01EX461), pp. 9–11 (2001). https://doi.org/10.1109/IITC.2001.930001

Edelstein, D., Uzoh, C., Cabral, C., DeHaven, P., Buchwalter, P., Simon, A., Cooney, E., Malhotra, S., Klaus, D., Rathore, H.: An optimal liner for copper damascene interconnects. In: Proceedings of the Advanced Metallization Conference (AMC), p. 541 (2001)

Blech, I.A.: Electromigration in thin aluminum films on titanium nitride. J. Appl. Phys. 47, 1203 (1976). https://doi.org/10.1063/1.322842

Kikuta, K.: Aluminum reflow sputtering. MRS Bull. 20(11), 53–56 (1995). https://doi.org/10.1557/S0883769400045577

Kikuta, K., Hayashi, Y., Nakajima, T., Harashima, K., Kikkawa, T.: Aluminum-germanium-copper multilevel damascene process using low-temperature reflow sputtering and chemical mechanical polishing. IEEE Trans. Electron Dev. 43(5), 739–745 (1996). https://doi.org/10.1109/16.491250

Sengupta, S., Narasimhan, M., Lee, S., Abburi, M., Yao, G.: Improved Al-via fill process technology for sub-0.251 μm interconnect. MRS Proc. 564 (2011). https://doi.org/10.1557/PROC-564-437

Edelstein, D., Heidenreich, J., Goldblatt, R., Cote, W., Uzoh, C., Lustig, N., Roper, P., McDevitt, T., Motsiff, W., Simon, A., Dukovic, J., Wachnik, R., Rathore, H., Schulz, R., Su, L., Luce, S., Slattery, J.: Full copper wiring in a sub-0.25/spl mu/m CMOS ULSI technology. In: International Electron Devices Meeting. IEDM Technical Digest, pp. 773–776 (1997). https://doi.org/10.1109/IEDM.1997.650496

Heidenreich, J., Edelstein, D., Goldblatt, R., Cote, W., Uzoh, C., Lustig, N., McDevitt, T., Stamper, A., Simon, A., Dukovic, J., Andricacos, P.C., Wachnik, R., Rathore, H., Katsetos, T., McLaughlin, P., Luce, S., Slattery, J.: Copper dual damascene wiring for sub-0.25 /spl mu/m CMOS technology. In: Proceedings of the IEEE 1998 International Interconnect Technology Conference (Cat. No.98EX102), pp. 151–153 (1998). https://doi.org/10.1109/IITC.1998.704776

Mahan, J.E.: Physical Vapor Deposition of Thin Films. Wiley-Interscience (New York, 2000). For detailed discussions of sputtering kinematics, refer to chapter VII

Mattox, D.M.: Handbook of Physical Vapor Deposition (PVD) Processing, 2nd edn. William Andrew, Norwich (2010)

Rossnagel, S.M.: Sputter deposition for semiconductor manufacturing. IBM J. Res. Dev. 43, 163 (1999)

Rossnagel, S.M.: Thin film deposition with physical vapor deposition and related technologies. J. Vac. Sci. Technol. A. 21(5), S74 (2003)

Simon, A.H.: Sputter processing. In: Seshan, K. (ed.) Handbook of Thin Film Deposition, 3rd edn, pp. 55–88. William Andrew/Elsevier (2012). https://doi.org/10.1016/C2009-0-64359-2

Simon, A.H.: Sputter processing. In: Seshan, K., Schepis, D. (eds.) Handbook of Thin Film Deposition, 4th edn, pp. 195–230. William Andrew/Elsevier (2018). https://doi.org/10.1016/C2016-0-03243-6

Chapman, D.: Glow Discharge Processes: Sputtering and Plasma Etching. Wiley-Interscience, New York (1980)

Broughton, J.N., Backhouse, C., Brett, M., Dew, S., Este, G.: Long throw sputter deposition of Ti at low pressure. In: Proceedings of the 12th International VLSI Multilevel Interconnection Conference, p. 201 (1995)

Mayo, A.A., Hamaguchi, S., Joo, J.H., Rossnagel, S.M.: Across-wafer nonuniformity of long throw sputter deposition. J. Vac. Sci. Technol. B. 15, 1788 (1997)

Rossnagel, S.M., Mikalsen, D., Kinoshita, H., Cuomo, J.J.: Collimated magnetron sputter deposition. J. Vac. Sci. Technol. A. 9, 261 (1991)

Hopwood, J.: Ionized physical vapor deposition of integrated circuit interconnects. Phys. Plasmas. 5(5), 1624 (1998)

Mao, D., Tao, K., Hopwood, J.: Ionized physical vapor deposition of titanium nitride: plasma and film characterization. J. Vac. Sci. Technol. A. 20(2), 379 (2002)

Hopwood, J. (ed.): Ionized Physical Vapor Deposition. Academic Press, Waltham (2000)

Rossnagel, S.M., Hopwood, J.: Metal ion deposition from ionized magnetron sputtering discharge. J. Vac. Sci. Technol. B. 12, 449 (1994)

Simon, A.H., Uzoh, C.E.: Open-bottomed via liner structure and method for fabricating same, US Patents 5,933,753 and 6,768,203.

Geffken, R.M., Luce, S.E.: Method of forming a self-aligned copper diffusion barrier in vias, US Patent 5,985,762

Malhotra, S.G., Simon, A.H.: Method for depositing a metal layer on a semiconductor interconnect structure, US Patent 6,949,461

Alers, G.B., Vijayendran, A., Gillespie, P., Chen, L., Cox, H., Lam, K., Augur, R., Shannon, K., Pfeifer, S., Danek, M.: Electromigration improvement with PDL TiN(Si) barrier in copper dual damascene structures. In: Proceedings of the IEEE 41st International Reliability Physics Symposium (IRPS), p. 151 (2003)

Yang, C.-C., Wang, Y., Clevenger, L., Simon, A., Greco, S., Chanda, K., Spooner, T., Cowley, A., Fang, S.: Simultaneous native oxide removal and metal neutral deposition method, US Patent 6,784,105

Kumar, N., Chu, S., Diehl, D., Tanimoto, T., Ohkura, A., Maekawa, K., Mori, K., Kobayashi, K., Yoneda, M.: Improvement in parametric and reliability performance of 90nm dual-damascene interconnects using Ar+ punch-thru PVD Ta(N) barrier process. In: Proceedings of the Advanced Metallization Conference (AMC), p. 247 (2004)

Yang, C.-C., Shaw, T., Simon, A., Edelstein, D.: Effects of contact area on mechanical strength, electrical resistance, and electromigration reliability of cu/low-k interconnects. Electrochem. Solid-State Lett. 13(6), H197 (2010)

Hosokawa, N., Tsukada, T., Kitahara, H.: Effect of discharge current and sustained self-sputtering. In: Proceedings of the Eighth International Vacuum Congress, Cannes, France, vol. 1, p. 11 (1980)

Posadowski, W.M., Radzimski, Z.J.: Sustained self-sputtering using a direct current magnetron source. J. Vac. Sci. Technol. A. 11, 2980 (1993)

Radzimski, Z.J., Hankins, O.E., Cuomo, J.J., Posadowski, W.P., Shingubara, S.: Optical emission spectroscopy of high-density metal plasma formed during magnetron sputtering. J. Vac. Sci. Technol. B. 15, 202 (1997)

Radzimski, Z.J., Posadowski, W.M., Rossnagel, S.M., Shingubara, S.: Directional copper deposition using dc magnetron self-sputtering. J. Vac. Sci. Technol. B. 16, 1102 (1998)

La Hemann, M., Bohlmark, J., Ehiarson, A., Gudmundsson, J.T.: Ionized physical vapor deposition (IPVD): a review of technology and applications. Thin Solid Films. 513(1–2), 1–24 (2006)

Edelstein, D.C., Harper, J.M.E., Hu, C.-K., Simon, A.H., Uzoh, C.E.: Copper interconnection structure incorporating a metal seed layer, US Patent 6,181,012

Edelstein, D.C., Harper, J.M.E., Hu, C.-K., Simon, A.H., Uzoh, C.E.: Copper interconnection structure incorporating a metal seed layer, US Patent 6, 399,496

Koike, J., Wada, M.: Self-forming diffusion barrier layer in Cu–Mn alloy metallization. Appl. Phys. Lett. 87, 41911 (2005)

Usui, T., Nasu, H., Takahashi, S., Shimizu, N., Nishikawa, T., Yoshimaru, M., Shibata, H., Wada, M., Koike, J.: Highly reliable copper dual-damascene interconnects with self-formed MnSi/sub x/O/sub y/ barrier layer. IEEE Trans. Electron Dev. 53(10), 2492–2499 (2006). https://doi.org/10.1109/TED.2006.882046

Kudo, H., Haneda, M., Ochimizu, H., Tsukune, A., Okano, S., Ohtsuka, N., Sunayama, M., Sakai, H., Suzuki, T., Kitada, H., Amari, S., Tabira, T., Matsuyama, H., Shimizu, N., Futatsugi, T., Sugii, T.: Copper wiring encapsulation with ultra-thin barriers to enhance wiring and dielectric reliabilities for 32-nm nodes and beyond. In: 2007 IEEE International Electron Devices Meeting, pp. 513–516 (2007). https://doi.org/10.1109/IEDM.2007.4418987

Simon, A., Baumann, F., Bolom, T., Park, J.-G., Niu, C., Matsuyama, H., Motoyama, K., Nogami, T.: Mn-dopant segregation as an indicator of barrier integrity in 32nm Groundrule Cu/Ultra-Low k interconnects. In: Proceedings of the Advanced Metallization Conference (AMC) (2011)

Nogami, T., Bolom, T., Simon, A., Kim, B.-Y., Hu, C.-K., Tsumura, K., Madan, A., Baumann, F., Wang, Y., Flaitz, P., Parks, C., DeHaven, P., Davis, R., Zaitz, M., St, B., Lawrence, R., Murphy, L., Tai, S.M., Rhee, S.-H., Usui, T., Cabral, C., Maniscalco, J., Clevenger, L., Li, B., Christiansen, C., Chen, F., Lee, T., Schmatz, J., Shobha, H., Ito, F., Ryan, T., Nguyen, S., Canaperi, D., Arnold, J., Choi, S., Cohen, S., Liniger, E., Chen, H.-C., Chen, S.-T., Vo, T., Kelly, J., Straten, O., Penny, C., Bonilla, G., Kozlowski, P., Spooner, T., Edelstein, D.: High reliability 32 nm Cu/ULK BEOL based on PVD CuMn seed, and its extendibility. In: 2010 International Electron Devices Meeting, pp. 33.5.1–33.5.4 (2010). https://doi.org/10.1109/IEDM.2010.5703471

Edelstein, D.C., Nogami, T., Parks, C., Tai, T.-L.: Copper interconnect structure and its formation, U.S. Patent 8,969,197 B2

Nogami, T., Penny, C., Madan, A., Parks, C., Li, J., Flaitz, P., Uedono, A., Chiang, S., He, M., Simon, A., Bolom, T., Ryan, T., Ito, F., Christiansen, C., Tai, L., Hu, C.-K., Kim, H., Zhang, X., Tanwar, K., Choi, S., Baumann, F., Davis, R., Kelly, J., Murphy, R., Molis, S., Rowland, J., Dehaven, P., Canaperi, D., Spooner, T., Edelstein, D.: Electromigration extendibility of Cu(Mn) alloy-seed interconnects, and understanding the fundamentals. In: 2012 International Electron Devices Meeting, pp. 33.7.1–33.7.4 (2012). https://doi.org/10.1109/IEDM.2012.6479161

Kim, H., Koseki, T., Ohba, T., Ohta, T., Kojima, Y., Sato, H., Shimogaki, Y.: Cu wettability and diffusion barrier property of Ru thin film for cu metallization. J. Electrochem. Soc. 152(8), G594–G600 (2005)

Shima, K., Shimizu, H., Momose, T., Shimogaki, Y.: Study on the adhesion strength of CVD-Cu films with ALD-Co(W) Underlayers made using amidinato precursors. ECS J. Solid-State Sci. Technol. 4(2), 20–29 (2015). https://doi.org/10.1149/2.005402ssl

Shima, K., Shimizu, H., Momose, T., Shimogaki, Y.: Comparative study on Cu-CVD nucleation using β-diketonato and Amidinato precursors for Sub-10-nm-thick continuous film growth. ECS J. Solid-State Sci. Technol. 4(8), P305–P313 (2015)

Malhotra, S.G., Canaperi, D., Chiras, S., Deligianni, H., Johnson, G., Krishnan, M., Lane, M., McFeely, F., Murray, C., Ponoth, S., Simon, A., Spooner, T., Vereecken, P., Yurkas, J.: Integration of direct plating of Cu onto a CVD Ru liner. In: Proceedings of the Advanced Metallization Conference (AMC), p. 525 (2004)

Suzuki, K., Faguet, J., Mizusawa, Y.: Thin CVD Ru film performance as Cu diffusion barrier and for direct plating. In: Proceedings of the Advanced Metallization Conference (AMC), p. 469 (2005)

Yang, C.-C., Spooner, T., Ponoth, S., Chanda, K., Simon, A., Lavoie, C., Lane, M., Hu, C.-K., Liniger, E., Gignac, L., Shaw, T., Cohen, S., McFeely, F., Edelstein, D.: Physical, electrical, and reliability characterization of Ru for Cu interconnects. In: Proceedings of the International Interconnect Technology Conference (IITC), p. 187. IEEE (2006)

Rullan, J., Ishizaka, T., Cerio, F., Mizuno, S., Mizusawa, Y., Ponnuswamy, T., Reid, J., McKerrow, A., Yang, C.-C.: Low resistance wiring and 2Xnm void free fill with CVD ruthenium liner and DirectSeed (TM) copper. In: Proceedings of the International Interconnect Technology Conference (IITC), p. 85. IEEE (2010)

Yokoyama, O., Han, C., Sakuma, T., Yasumuro, C., Hirasawa, T., Ishizaka, T., Suzuki, K.: Copper wiring forming method with Ru liner and Cu alloy fill, U.S Patent 9406557B2

Yang, C.-C., Cohen, S., Shaw, T., Wang, P.-C., Nogami, T., Edelstein, D.: Ultrathin-Cu/Ru(Ta)/TaN liner stack for copper interconnects. IEEE Electron Dev. Lett. 31, 722–724. https://doi.org/10.1109/LED.2010.2047934

Yang, C.C., McFeely, F.R., Li, B., Rosenberg, R., Edelstein, D.: Low-temperature reflow anneals of Cu on Ru. IEEE Electron Dev. Lett. 32(6), 806–808 (2011). https://doi.org/10.1109/LED.2011.2132691

Ishizaka, T., Gomi, A., Kato, T., Sakuma, T., Yokoyama, O., Yasumuro, C., Toshima, H., Mizusawa, Y., Hatano, T., Han, C.S., Hara, M.: Cu dry-fill on CVD Ru liner for advanced gap-fill and lower resistance. In: Interconnect Technology Conference and 2011 Materials for Advanced Metallization (IITC/MAM), p. 85. IEEE (2011)

Matsuda, T., Lee, J., Han, K.H., Park, K.H., Cha, J., Baek, J., Yim, T., Kim, D.C., Lee, D., Kim, J., Choi, S.H., Lee, E., Nam, S., Lee, H., Cho, Y., Kim, I., Kwon, B., Ahn, S., Yun, J., Kim, B., Yoon, B., Hong, J., Lee, N.I., Choi, S., Kang, H.K., Chung, E.: Superior Cu fill with highly reliable Cu/ULK integration for 10nm node and beyond. In: 2013 IEEE International Electron Devices Meeting, pp. 29.2.1–29.2.4 (2013). https://doi.org/10.1109/IEDM.2013.6724715

Kim, R.-H., Kim, B.H., Matsuda, T., Kim, J.N., Baek, J.M., Lee, J.J., Cha, J.O., Hwang, J.H., Yoo, S.Y., Chung, K.-M., Park, K.H., Choi, J.K., Lee, E.B., Nam, S.D., Cho, Y.W., Choi, H.J., Kim, J.S., Jung, S.Y., Lee, D.H., Kim, I.-S., Park, D.W., Lee, H.B., Ahn, S.H., Park, S.-H., Kim, M.-C., Yoon, B.U., Paak, S.S., Lee, N.-I., Ku, J.-H., Yoon, J.S., Kang, H.-K., Jung, E.S.: Highly reliable Cu interconnect strategy for 10nm node logic technology and beyond. In: 2014 IEEE International Electron Devices Meeting, pp. 32.2.1–32.2.4 (2014). https://doi.org/10.1109/IEDM.2014.7047153

Kikuchi, Y., Kawasaki, H., Nagai, H., Yu, K.-H., Oie, M., Consiglio, S., Wajda, C., Maekawa, K., Leusink, G.: Electrical properties and TDDB performance of Cu interconnects using ALD Ta(Al)N barrier and Ru liner for 7nm node and beyond. In: 2016 IEEE International Interconnect Technology Conference / Advanced Metallization Conference (IITC/AMC), pp. 99–101 (2016). https://doi.org/10.1109/IITC-AMC.2016.7507696

Dey, S., Kai-Hung, Y., Consiglio, S., Tapily, K., Hakamata, T., Wajda, C.S., Leusink, G.J., Jordan-Sweet, J., Lavoie, C., Muir, D., Moreno, B., Diebold, A.C.: Atomic layer deposited ultrathin metal nitride barrier layers for ruthenium interconnect applications. J. Vac. Sci. Technol. A. 35, 03E109 (2017). https://doi.org/10.1116/1.4979709

Mueller, J.E., Inoki, C.K., Brisco, D., LaBarbera, S.F., Kuan, T.S., Rossnagel, S.M., Sun, J.Z.: Nucleation and wetting of PVD Cu seed on ultra-thin Ta, Co, Ru, and Ta-Ru liners, SRC Report P019881 (2007) https://www.src.org/library/publication/p019881/

Ma, P., Luo, Q., Sundarrajan, A., Jiang, L., Aubuchon, J., Tseng, J., Kumar, N., Okazaki, M., Wang, Y., Wang, Y., Chen, Y., Naik, M., Emesh, I., Narasimhan, M.: Optimized integrated copper gap-fill approaches for 2x flash devices. In: 2009 IEEE International Interconnect Technology Conference, Sapporo, Hokkaido, pp. 38–40 (2009). https://doi.org/10.1109/IITC.2009.5090334

Carbonell, L., Volders, H., Heylen, N., Kellens, K., Caluwaerts, R., Devriendt, K., Sanchez, E.A., Wouters, J., Gravey, V., Shah, K., Luo, Q., Sundarrajan, A., Lu, J., Aubuchon, J., Ma, P., Narasimhan, M., Cockburn, A., Tokei, Z., Beyer, G.P.: Metallization of sub-30 nm interconnects: comparison of different liner/seed combinations. In: 2009 IEEE International Interconnect Technology Conference, Sapporo, Hokkaido, pp. 200–202 (2009). https://doi.org/10.1109/IITC.2009.5090387

Nogami, T., Maniscalco, J., Madan, A., Flaitz, P., DeHaven, P., Parks, C., Tai, L., St, B., Lawrence, R., Davis, R., Murphy, T., Shaw, S.C., Hu, C.-K., Cabral, C., Chiang, S., Kelly, J., Zaitz, M., Schmatz, J., Choi, S., Tsumura, K., Penny, C., Chen, H.-C., Canaperi, D., Vo, T., Ito, F., Straten, O., Simon, A., Rhee, S.-H., Kim, B.-Y., Bolom, T., Ryan, V., Ma, P., Ren, J., Aubuchon, J., Fine, J., Kozlowski, P., Spooner, T., Edelstein, D.: CVD Co and its application to Cu damascene interconnections. In: 2010 IEEE International Interconnect Technology Conference, Burlingame, CA, pp. 1–3 (2010). https://doi.org/10.1109/IITC.2010.5510584

Simon, A.H., Bolom, T., Niu, C., Baumann, F.H., Hu, C.-K., Parks, C., Nag, J., Kim, H., Lee, J.Y., Yang, C.-C., Nguyen, S., Shobha, H.K., Nogami, T., Guggilla, S., Ren, J., Sabens, D., AuBuchon, J.F.: Electromigration comparison of selective CVD cobalt capping with PVD Ta(N) and CVD cobalt liners on 22nm-groundrule dual-damascene Cu interconnects. In: 2013 IEEE International Reliability Physics Symposium (IRPS), Anaheim, CA, pp. 3F.4.1–3F.4.6 (2013). https://doi.org/10.1109/IRPS.2013.6532002

Baumann, F.H., Bolom, T., Hu, C.-K., Motoyama, K., Niu, C., Simon, A.H.: Copper interconnect with CVD liner and metallic cap, US Patent 9,111,938

Motoyama, K., van der Straten, O., Maniscalco, J., Huang, H., Kim, Y.B., Choi, J.K., Lee, J.H., Hu, C.-K., McLaughlin, P., Standaert, T., Quon, R., Bonilla, G.: Ru liner scaling with ALD TaN barrier process for low resistance 7 nm Cu interconnects and beyond. In: 2018 IEEE International Interconnect Technology Conference (IITC), Santa Clara, CA, pp. 40–42 (2018). https://doi.org/10.1109/IITC.2018.8430296

Motoyama, K., van der Straten, O., Maniscalco, J., Cheng, K., DeVries, S., Hu, C.-K., Huang, H., Park, K., Kim, Y., Hosadurga, S., Lanzillo, N., Simon, A., Jiang, L., Peethala, B., Standaert, T., Wu, T., Spooner, T., Choi, K.: EM enhancement of Cu interconnects with Ru liner for 7 nm node and beyond. In: 2019 IEEE International Interconnect Technology Conference/Materials for Advanced Metallization (IITC/MAM) (2019)

Motoyama, K., van der Straten, O., Maniscalco, J., Cheng, K., DeVries, S., Huang, H., Shen, T., Lanzillo, N., Hosadurga, S., Park, K., Bae, T., Seo, H., Wu, T., Spooner, T., Choi, K.: Co-doped Ru liners for highly reliable cu interconnects with selective Co cap. In: 2020 IEEE International Interconnect Technology Conference (IITC), Santa Clara, CA, 2020 (Virtual) (2020)

Huang, H., Lanzillo, N., Standaert, T.E., Motoyama, K., Yang, C., Shobha, H., Maniscalco, J.F., Nogami, T., Li, J., Spooner, T.A., Bonilla, G.: Impact of liner metals on copper resistivity at beyond 7 nm dimensions. In: 2018 IEEE International Interconnect Technology Conference (IITC), Santa Clara, CA, pp. 13–15 (2018). https://doi.org/10.1109/IITC.2018.8430472

Ding, P., Hashim, I., Chin, B.L.: Structure for improving low temperature copper reflow in semiconductor features, U.S. Patent 6,352,926 B1

Ta, K.: Ushering in the era of nanoscale chip wiring, https://blog.appliedmaterials.com/ushering-era-nanoscale-chip-wiring

Motoyama, K., van der Straten, O., Tomizawa, H., Maniscalco, J., Chen, S.T.: Novel Cu reflow seed process for Cu/low-k 64nm pitch dual damascene interconnects and beyond. In: 2012 IEEE International Interconnect Technology Conference, San Jose, CA, pp. 1–3 (2012). https://doi.org/10.1109/IITC.2012.6251656

Motoyama, K., van der Straten, O., Maniscalco, J., He, M.: PVD Cu reflow seed process optimization for defect reduction in nanoscale Cu/low-k dual damascene interconnects. J. Electrochem. Soc. 160(12), D3211–D3215 (2013)

Bhosale, P.S., Maniscalco, J., Lanzillo, N., Nogami, T., Canaperi, D., Motoyama, K., Huang, H., McLaughlin, P., Shaviv, R., Stolfi, M., Vinnakota, R., How, G., Pethe, S., Sheu, B., Xie, X., Chen, L.: Modified ALD TaN barrier with Ru liner and dynamic Cu reflow for 36nm pitch interconnect integration. In: 2018 IEEE International Interconnect Technology Conference (IITC), Santa Clara, CA, pp. 43–45 (2018). https://doi.org/10.1109/IITC.2018.8430474

Chen, F., Gambino, J., Shinosky, M., Li, B., Angyal, M., Badami, D., Aitken, J. Proceedings of the IEEE 2009 International Interconnect Technol. Conf., 182 (2009)

Moon, P., Dubin, V., Johnston, S., Leu, J., Raol, K., Wu, C.: Tech. Dig. IEEE IEDM 2003, 35.1.1 (2003)

Chow, L.A.: Ch. 6 in handbook of thin film deposition. In: Seshan, K. (ed.) . Elsevier Inc., Waltham (2012)

Nguyen, S., Haigh Jr., T., Shaw, T., Molis, S., Dziobkowski, C., Zahakos, C., Cohen, S., Shobha, H., Liniger, E., Hu, C.K., Bonilla, G., Klymko, N., Grill, A.: ECS Trans. 33(12), 137 (2010)

Nguyen, S., Grill, A., Cohen, S., Shobha, H., Klymko, N., Simonyi, E., Haigh, T., Hu, C., Adams, E., Linger, E., Madan, A., Shaw, T., Ryan, E.T., Cheng, T., Herman, J., Young, R.: Proceeding of 216th electrochemical society meeting, paper #2159 (2009)

Nguyen, S., Haigh Jr., T., Tagami, M., Grill, A., Cohen, S., Shobha, H., Hu, C., Adams, E., Liniger, E., Shaw, T., Cheng, T., Yusuff, H., Xu, Y., Ko, T., Molis, S., Spooner, T., Skodas, S., Liu, X., Bonilla, G., Edelstein, D.: ECS Trans. 41(43), 3–9 (2012)

King, S.: ECS Trans. 33(2), 365 (2010)

Lane, M.W., Liniger, E.G., Lloyd, J.R.: J. Appl. Phys. 93(3), 1417 (2003)

Lloyd, J.R., Lane, M.W., Liniger, E.G., Hu, C.-K., Shaw, T.M., Rosenberg, R.: IEEE Trans. Dev. Mater. Rel. 5(1), 113 (2005)

S. V. Nguyen, H. Shobha, D. Priyadarshini, C.-C. Yang, T. Haigh Jr., C.-K. Hu, S. Cohen, E. Liniger, T. Shaw, E. Adams J. Burnham, T. Ko, Y. Lin, A. Madan, N. Klymko, C. Parks, D. Yang, Jr., S. Knupp, S. Molis, A. Simon, G. Bonilla, A. Grill, D. Edelstein, D. Canaperi, T. Spooner, D. Collin, L.-Q. Xia, S. Reiter, M. Balseanu, and M. Shek, Proceedings 2013 International Conference on Atomic Layer Deposition, 119 (2013)

Chang, S.Y., Wan, C.C., Wang, Y.Y.: Electrochem. Solid-State Lett. 10(5), D43 (2007)

Hu, C.K., Ohm, J., Gignac, L.M., Breslin, C.M., Mittal, S., Bonilla, G., Edelstein, D., Rosenberg, R., Choi, S., An, J.J., Simon, A.H., Angyal, M.S., Clevenger, L., Maniscalco, J., Nogami, T., Penny, C., Kim, B.Y.: J. Appl. Phys. 111(9), 093722 (2012)

Yang, C.-C., Chen, F., Li, B., Shobha, H., Nguyen, S., Grill, A., Ye, W., AuBuchon, J., Shek, M., Edelstein, D.: IEEE Electron Dev. Lett. 33(4), 588 (2012)

Nguyen, S., Vo, T., Haigh, T., Cohen, S., Flaitz, P., Nogami, T., Shobha, H., Priyadarshini, D., Lin, Y., Canaperi, D., Grill, A., Gordon, R., Au, Y.: Proceeding of atomic layer deposition conference, p. 67–68, Portland Oregon (2015)

Yang, C.-C., McFeely, R., Wang, P.-C., Chanda, K., Edelstein, D.C.: Electrochem. Solid-State Lett. 13(5), D33–D35 (2010)

Deepika Priyadarshini, Son Nguyen, H. Shobha, S. Cohen, T. Shaw, E. Liniger, C.K. Hu, C. Parks, E. Adams, J. Burnham, G. Bonilla, A. Grill, D. Canaperi, D. Edelstein, D. Collins, M. Shek, L.-Q. Xia; https://doi.org/10.1109/IITC.2014.6831866, Interconnect Technology Conference / Advanced Metallization Conference (IITC/AMC), 2014 IEEE International, pp. 185–188, San Jose California

Rainville, M.G., Shankar, N., Reddy, K.S., Hausmann, D.M.: 2010 US Patent # 9859153B1

King, S.: CS J. Solid State Sci. Technol. 4(1), N3029–N3047 (2014). https://doi.org/10.1149/2.0051501jss

US patent # 9349687 B2

US Patent # 9947579 B2

Author information

Authors and Affiliations

Corresponding author

Editor information

Editors and Affiliations

Rights and permissions

Copyright information

© 2023 Springer Nature Switzerland AG

About this chapter

Cite this chapter

Chen, ST., Lanzillo, N.A., Van Nguyen, S., Nogami, T., Simon, A.H. (2023). Interconnect Processing: Integration, Dielectrics, Metals. In: Rudan, M., Brunetti, R., Reggiani, S. (eds) Springer Handbook of Semiconductor Devices . Springer Handbooks. Springer, Cham. https://doi.org/10.1007/978-3-030-79827-7_5

Download citation

DOI: https://doi.org/10.1007/978-3-030-79827-7_5

Published:

Publisher Name: Springer, Cham

Print ISBN: 978-3-030-79826-0

Online ISBN: 978-3-030-79827-7

eBook Packages: EngineeringEngineering (R0)