Abstract

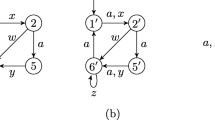

Design For Testability (DFT) is understood as the process of introducing some features into a protocol entity that facilitate the testing process of protocol implementations. DFT at the implementation level deals with a particular realization on a given platform, whereas DFT at the specification level affects all possible implementations regardless of the implementation process. The fact that protocols are usually specified only partially, facilitates DEC at the specification level. In this paper, we address one particular problem of DFT, the problem of finding a minimal augmentation of the given protocol behavior (an FSM) such that a newly obtained specification is more testable than the original one, while maintaining sets of defined states and events. We propose an approach to augmenting a partially specified FSM such that a test suite for the resulting FSM with guaranteed fault coverage is shorter than that for the original FSM.

Chapter PDF

Similar content being viewed by others

References

M. Abramovici, M. A. Breuer, and A. D. Friedman, Digital Systems Testing and Testable Design, Computer Science Press, Oxford, England, 1990.

G. v. Bochmann and A. Petrenko, “Protocol Testing: Review of Methods and Relevance for Software Testing”, ISSTA’94, ACM International Symposium on Software Testing and Analysis, Seattle, U.S.A., 1994, pp. 109–124.

G. v. Bochmann, A. Petrenko, and M. Yao, “Fault Coverage of Tests Based on Finite State Models”, the Proceedings of IFIP TC6 Seventh IWPTS’94, Japan.

T. S. Chow, “Testing Software Design Modeled by Finite-State Machines”, IEEE Transactions on Software Engineering, Vol. SE-4, No. 3, 1978, pp. 178–187.

R. Dssouli and R. Fournier, “Communication Software Testability”, IFIP Transactions, Protocol Testing Systems III (the Proceedings of IFIP TC6 Third International Workshop on Protocol Test Systems), Ed. by I. Davidson and W. Litwack, North Holland, 1991, pp. 45–55.

S. Fujiwara, G. v. Bochmann, F. Khendek, M. Amalou, A. Ghedamsi, “Test Selection Based on Finite State Models”, IEEE Transactions on Software Engineering, Vol. SE-17, No. 6, 1991, pp. 591–603.

A. Gill, Introduction to the Theory of Finite-State Machines, McGraw-Hill, 1962. [Henn64] F. C. Hennie, “Fault Detecting Experiments for Sequential Circuits”, IEEE 5th Ann. Symp. on Switching Circuits Theory and Logical Design, 1964, pp. 95–110.

D. Hogrefe, “OSI Formal Specification Case Study: The Inres Protocol and Service”, University of Berne, Technical Report IAM-91–012, University of Berne, 1991.

J. Joseph, “On Easily Diagnosable Sequential Machines”, IEEE Transactions on Computers, Vol. C-27, February, 1978, pp. 159–162.

D. Lee and M. Yannakakis, “Testing Finite-State Machines: State Identification and Verification”, IEEE Trans. on Computers, Vol. 43, No. 3, 1994, pp. 306–320.

A. Petrenko, “Checking Experiments with Protocol Machines”, IFIP Transactions, Protocol Test Systems, IV (the Proceedings of IFIP TC6 Fourth International Workshop on Protocol Test Systems, 1991), Ed. by Jan Kroon, Rudolf J. Heijink and Ed Brinksma, 1992, North-Holland, pp. 83–94.

A. Petrenko, G. v. Bochmann, and R. Dssouli, “Conformance Relations and Test Derivation”, IFIP Transactions, Protocol Test Systems, VI, (the Proceedings of IFIP TC6 Fifth International Workshop on Protocol Test Systems, 1993), Ed. by O. Rafiq, 1994, North-Holland, pp.157–178.

A. Petrenko, R. Dssouli, and H. Konig, “On Evaluation of Testability of Protocol Structures”, IFIP Transactions, Protocol Test Systems, VI, (the Proceedings of IFIP TC6 Fifth International Workshop on Protocol Test Systems, 1993), Ed. by O. Rafiq, 1994, North-Holland, pp.111–123.

M. L. Sheu and C. L. Lee, “Symplifying Sequential Circuit Test Generation”, IEEE Design and Test of Computers, Fall 1994, pp. 28–38.

D. P. Sidhu and T. K. Leung, “Formal Methods for Protocol Testing: A Detailed Study”, IEEE Trans. on Software Engineering, Vol. SE-15, No. 4, 1989, pp. 413–426.

T. Tylaska and J. D. Bargainer, “An Improved Bound for Checking Experiments that Use Simple Input-Output and Characterizing Sequences”, IEEE Transactions on Computers, Vol. C-24, No. 6, 1975, pp. 670–673.

M. P. Vasilevski, “Failure Diagnosis of Automata”, Cybernetics, Plenum Publishing Corporation, New York, No. 4, 1973, pp. 653–665.

S. T. Vuong, A. A. F. Loureiro, and S. T. Chanson, “A Framework for the Design for Testabilitiy of Communication Protocols”, in the Proceedings of IFIP TC6 Fifth IWPTS’93, Ed. by O. Rafiq, 1994, North-Holland, pp.89–108.

Author information

Authors and Affiliations

Editor information

Editors and Affiliations

Rights and permissions

Copyright information

© 1996 Springer Science+Business Media Dordrecht

About this chapter

Cite this chapter

Yevtushenko, N., Petrenko, A., Dssouli, R., Karoui, K., Prokopenko, S. (1996). On the design for testability of communication protocols. In: Cavalli, A., Budkowski, S. (eds) Protocol Test Systems VIII. IFIP — The International Federation for Information Processing. Springer, Boston, MA. https://doi.org/10.1007/978-0-387-34988-6_17

Download citation

DOI: https://doi.org/10.1007/978-0-387-34988-6_17

Publisher Name: Springer, Boston, MA

Print ISBN: 978-1-4757-6312-6

Online ISBN: 978-0-387-34988-6

eBook Packages: Springer Book Archive