Abstract

In this work, we are making energy efficient ALU using the most energy efficient LVCMOS IO standard for the highest frequency of i7 processor. It is observed that LVCMOS12 is the most energy efficient than all available LVCMOS having 26.23, 58.37 and 75.65 % less IO power reduction than LVCMOS18, LVCMOS25 and LVCMOS33 respectively at 1 GHz. Then we are making this ALU portable using MOBILE DDR IO standard in place of default LVCMOS33 IO standard which we use in traditional ALU. As we replace LVCMOS with MOBILE DDR, we are achieving 69.07 % portability in terms of IO power and 29.36 % in terms of Leakage power at 2.9 GHz. In next stage, we try to enhance the performance of ALU with MOBILE DDR but not beyond the power consumption with LVCMOS. In that way, we achieve the highest frequency of 12 GHz with MOBILE DDR. That was earlier possible for 3.8 GHz 64-bit ALU using CMOS. In this HDL based implementation of 64-bit ALU on FPGA, Kintex-7 FPGA is used with XC7K70T device and FBG676 package is used.

Similar content being viewed by others

References

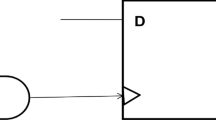

Sharma, M., Sharma, K. G., Sharma, T., Singh, B. P., & Arora. N. (2011). SET D-flip flop design for portable applications. iN IEEE India international conference on power electronics (IICPE) (pp. 1–5).

Panda, P. R., Silpa, B. V. N., Shrivastava, A., & Gummidipudi, K. (2010). Power-efficient system design. Springer Press, 253 p, ISBN 978-1-4419-6388-8.

Maurice, M., & Gyvez, J. P. (2008). Technological boundaries of voltage and frequency scaling for power performance tuning. Springer Integrated Circuits and Systems, ISBN 978-1-4419-4553-2.

Morris, John. (2003). Reconfigurable logic: A saviour for experimental computer architecture research. Lecture Notes in Computer Science, 2823, 69–78.

Hui, L., & Ding, L. W. (2010). Low-power and portable design of bioelectrical impedance measurement system. In WASE international conference on information engineering (ICIE) (Vol. 3, pp. 38–41).

Gosset, G., & Flandre, D. (2011). Fully-automated and portable design methodology for optimal sizing of energy-efficient CMOS voltage rectifiers. IEEE Journal on Emerging and Selected Topics in Circuits and Systems, 1(2), 141–149.

Paganini, M., Kimmich, G., Ducrey, S., Caubit, G., & Coeffe, V. (2007). Portable multimedia SoC design: A global challenge. In Design, automation and test in Europe conference and exhibition, DATE ’07 (pp. 1–4).

Pandey, B., Yadav, J., Singh, Y., Kumar, R., & Patel, S. (2013). Energy efficient design and implementation of ALU on 40-nm FPGA. In IEEE international conference on energy efficient technologies for sustainability-(ICEETs). Nagercoil, Tamilnadu, April 10–12.

Kim, S. H. (2007). A low power and highly reliable 400 Mbps mobile DDR SDRAM with on-chip distributed ECC. In IEEE Asian solid-state circuits conference (pp. 34–37).

Marraa, L. et al. (2008). Experimental analysis of energy consumption by MobileDDR memory for mobile applications. In IEEE international symposium on industrial electronics (pp. 1686–1691).

Specification of 4th Generation Intel Core i7 Processor, www.intel.in.

Author information

Authors and Affiliations

Corresponding authors

Rights and permissions

About this article

Cite this article

Kumar, T., Pandey, B., Das, T. et al. Mobile DDR IO Standard Based High Performance Energy Efficient Portable ALU Design on FPGA. Wireless Pers Commun 76, 569–578 (2014). https://doi.org/10.1007/s11277-014-1725-z

Published:

Issue Date:

DOI: https://doi.org/10.1007/s11277-014-1725-z