Abstract

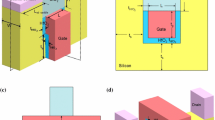

A novel high-performance H-shape-gate U-shape-channel junctionless FET (HGUC JL FET) is proposed. Compared with the saddle junctionless FET, the proposed HGUC JL FET shows better subthreshold characteristics and higher on-current. Its electrical properties were extensively investigated by studying the influence of variation of design parameters such as the H-gate thickness, the source/drain extension region height, and the gate oxide thickness and material. Compared with conventional structures, the proposed HGUC JL FET shows better performance, especially on scaling down to several nanometers. The reverse leakage current is also effectively restrained and the \({I}_{\mathrm{on}}\)/\({I}_{\mathrm{off}}\) ratio greatly improved through design optimization.

Similar content being viewed by others

References

Jean-Pierre, C., Chi-Woo, L., Aryan, A., et al.: Nanowire transistors without junctions. Nat. Nanotechnol. 5(3), 225–229 (2010)

Liu, X., Wu, M., Jin, X., et al.: Simulation study on deep nanoscale short channel junctionless SOI FinFETs with triple-gate or double-gate structures. J. Comput. Electron. 13(2), 509–514 (2014)

Barraud, S., Berthome, M., Coquand, R., et al.: Scaling of trigate junctionless nanowire MOSFET with gate length down to 13 nm. IEEE Electron Device Lett. 33(9), 1225–1227 (2012)

Wu, M., Jin, X., Kwon, H.I., et al.: The optimal design of junctionless transistors with double-gate structure for reducing the effect of band-to-band tunneling. J. Semicond. Technol. Sci. 13(3), 245–251 (2013)

Liu, X., Wu, M., Jin, X., et al.: The optimal design of 15 nm gate-length junctionless SOI FinFETs for reducing leakage current. Semicond. Sci. Technol. 28(10), 105013–105018(6) (2013)

Lou, H., Zhang, L., Zhu, Y., et al.: A junctionless nanowire transistor with a dual-material gate. IEEE Trans. Electron Devices 59(7), 1829–1836 (2012)

Baruah, R.K., Paily, R.P.: Impact of high-k spacer on device performance of a junctionless transistor. J. Comput. Electron. 12(1), 14–19 (2013)

Baruah, R.K., Paily, R.P.: The effect of high-k gate dielectrics on device and circuit performances of a junctionless transistor. J. Comput. Electron. 14(2), 492–499 (2015)

Hu, G., Xiang, P., Ding, Z., Liu, R., Wang, L., Tang, T.: Analytical models for electric potential, threshold voltage, and subthreshold swing of junctionless surrounding-gate transistors. IEEE Trans. Electron. Dev. 61, 688–695 (2014)

Dutta, P., Syamal, B., Mohankumar, N., Chandan, K.: A 2-D surface-potential-based threshold voltage model for short channel asymmetric heavily doped DG MOSFETs. Int. J. Numer. Model. Electron. Netw. Devices Fields 27, 682–690 (2014)

Jin, X., Liu, X., Lee, J.-H., Lee, J.H.: Modeling of subthreshold characteristics of short channel junctionless cylindrical surrounding-gate nanowire metal–oxide–silicon field effect transistors. Phys. Scr. 89, 015804 (2014)

Jin, X., Wu, M., Liu, X., et al.: A novel high performance junctionless FETs with saddle-gate. J. Comput. Electron. 14(3), 1–8 (2015)

Jin, X., Wu, M., Liu, X., Lee, J.-H., Lee, J.-H.: optimization of saddle junctionless FETs for extreme high integration. J. Comput. Electron. 15(3), 801–808 (2016)

Shoji, M., Horiguchi, S.: Electronic structures and phonon-limited electron mobility of double-gate silicon-on-insulator Si inversion layers. J. Appl. Phys 85, 2722–2731 (1999)

SILVACO International. ATLAS User’s Manual (2012)

Acknowledgements

This work is supported by the Natural Science Foundation of Liaoning Province No.201602541, No.201602546.

Author information

Authors and Affiliations

Corresponding author

Rights and permissions

About this article

Cite this article

Jin, X., Yang, G., Liu, X. et al. A novel high-performance H-gate U-channel junctionless FET. J Comput Electron 16, 287–295 (2017). https://doi.org/10.1007/s10825-017-0966-y

Published:

Issue Date:

DOI: https://doi.org/10.1007/s10825-017-0966-y