Abstract

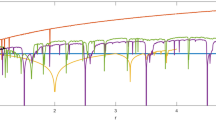

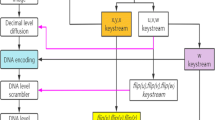

This paper presents a new approach to analysis and design of ADC-based random number generators. To this end, different full-bit and half-bit redundant stages of algorithmic converter are used to design chaotic maps. It is shown that, in the redundant and nonredundant structures, output probability density function of the converter stages and their related chaotic functions always converge to uniformity. It is demonstrated that residues become independent and uniformly distributed. This fact leads to the randomness and uniformity of distribution of the random number generator output bits. Moreover, it is shown that some common chaotic maps that are employed in chaotic random number generators can be implemented using nonredundant and half-bit redundant stages of algorithmic converter. In this way, the capability of ADC-based generators in designing chaotic maps and producing random number sequences is illustrated. The validity of the proposed chaos-based random number generator is confirmed using NIST statistical tests even in the presence of nonidealities in algorithmic converter. Since the ADCs are mixed-signal integrated circuits and can be used in high-speed applications, the ADC-based random number generator has high throughput and is easily embeddable in all analog and digital circuits.

Similar content being viewed by others

References

S. Callegari, R. Rovatti, G. Setti, Embeddable ADC-based true random number generator for cryptographic applications exploiting nonlinear signal processing and chaos. IEEE Trans. Signal Process. 53(2), 793–805 (2005)

T. Cho, P.R. Gray, A 10 b, 20 Msamples, 35 mW pipeline AD converter. IEEE J. Solid State Circuits 30(3), 166–172 (1995)

I. Cicek, A.E. Pusane, G. Dundar, A new dual entropy core true random number generator. Analog Integr. Circuits Signal Process. 81(1), 61–70 (2014)

I. Cicek, A.E. Pusane, G. Dundar, A novel design method for discrete time chaos based true random number generators. Integra. VLSI J. 47(1), 38–47 (2014)

P. Crippa, C. Turchetti, M. Conti, A statistical methodology for the design of high-performance CMOS current-steering digital-to-analog converters. EEE Trans. Comput. Aided Design Integr. Circuits Syst. 21(4), 377–394 (2002)

M. Delgado-Restituto, A. Rodríguez-Vázquez, Mixed-signal map configurable integrated chaos generator for chaotic communications. IEEE Trans. Circuits Syst. I Fundam. Theory Appl. 48(12), 1462–1474 (2001)

M. Drutarovsky, P. Galajda, Chaos-based true random number generator embedded in a reconfigurable hardware. J. Electr. Eng. 57(4), 218–225 (2006)

E. Fatemi-Behbahani, E. Farshidi, K. Ansari-Asl, A new approach to analysis of residue probability density function in pipelined ADCs. Integr. VLSI J. 52(1), 51–61 (2016)

J. Guerber, M. Gande, U.-K. Moon, The analysis and application of redundant multistage ADC resolution improvements through PDF residue shaping. IEEE Trans. Circuits Syst. I Reg. Pap. 59(8), 1733–1742 (2012)

U. Güler, S. Ergün, A high speed, fully digital IC random number generator. AEU Int. J. Electron. Commun. 66(2), 143–149 (2012)

P. Huang, S. Hsien, V. Lu, P. Wan, S.C. Lee, W. Liu, B.W. Chen, Y.P. Lee, W.T. Chen, T.Y. Yang, G.K. Ma, SHA-less pipelined ADC with in-situ background clock-skew calibration. IEEE J. Solid State Circuits 46(8), 1893–1903 (2011)

O. Katz, D.A. Ramon, I.A. Wagner, A robust random number generator based on a differential current-mode chaos. IEEE Trans. Very Large Scale Integr. VLSI Syst. 16(12), 1677–1686 (2008)

J.P. Keane, P.J. Hurst, S.H. Lewis, Digital background calibration for memory effects in pipelined analog-to-digital converters. IEEE Trans. Circuits Syst. I Reg. Pap. 53(3), 511–525 (2006)

M.G. Kim, P.K. Hanumolu, U.-K. Moon, A 10 MS/s 11-bit 0.19 mm\(^{2}\) algorithmic ADC with improved clocking scheme. IEEE J. Solid State Circuits 44(9), 2348–2355 (2009)

C.C. Lee, M.P. Flynn, A SAR-assisted two-stage pipeline ADC. IEEE J. Solid State Circuits 46(4), 859–869 (2011)

B. Levy, A propagation analysis of residual distributions in pipeline ADCs. IEEE Trans. Circuits Syst. I Reg. Pap. 58(10), 2366–2376 (2011)

J. Li, G. Ahn, D. Chang, U.-K. Moon, A 0.9-V 12-mW 5-MSPS Algorithmic ADC With 77-dB SFDR. IEEE J. Solid State Circuits 40(4), 960–969 (2005)

N. Li, W. Pan, S. Xiang, L. Yan, B. Luo, X. Zou, Influence of statistical distribution properties on ultrafast random-number generation using chaotic semiconductor lasers. Optik Int. J. Light Electron. Opt. 125(14), 3555–3558 (2014)

F. Maloberti, Data Converters (Springer, Berlin, 2007)

A. Papoulis, S.U. pillai, Probability Random Variables and Stochastic Processes, 4th edn. (McGraw-Hill, New York, 2002)

F. Pareschi, G. Setti, R. Rovatti, Implementation and testing of high-speed CMOS true random number generators based on chaotic systems. IEEE Trans. Circuits Syst. I Reg. Pap. 57(12), 3124–3137 (2010)

M.J.M. Pelgrom, A.C.J. Duinmaijer, A.P.G. Welbers, Matching properties of MOS transistors. IEEE J. Solid State Circuits 24(5), 1433–1439 (1989)

S. Robson, B. Leung, G. Gong, Truly random number generator based on a ring oscillator utilizing last passage time. IEEE Trans. Circuits Syst. II Exp. Briefs 61(12), 937–941 (2014)

A. Rukhin, J. Soto, J. Nechvatal, M. Smid, E. Barker, S. Leigh, M. Levenson, A statistical test suite for random and pseudorandom number generators for cryptographic applications, in National Institute of Standards and Technology (NIST), Special Publication800-22, Revision 1a, (2010). http://csrc.nist.gov/groups/ST/toolkit/rng/documents/SP800-22rev1a.pdf. (online)

G. Setti, G. Mazzini, R. Rovatti, S. Callegari, Statistical modeling of discrete-time chaotic processes-basic finite-dimensional tools and applications. Proc. IEEE 90(5), 662–690 (2002)

E.G. Soenen, R.L. Geiger, An architecture and an algorithm for fully digital correction of monolithic pipelined ADCs. IEEE Trans. Circuits Syst. II Analog Digit. Signal Process. 42(3), 143–153 (1995)

A.B. Sripad, D.L. Snyder, A necessary and sufficient condition for quantization errors to be uniform and white. IEEE Trans. Acoust. Speech Signal Process. ASSP–25(5), 442–448 (1977)

T. Stojanovski, L. Kocarev, Chaos-based random number generator–part I: analysis. IEEE Trans. Circuits Syst. I Fundam. Theory Appl. 48(3), 281–288 (2001)

T. Stojanovski, L. Kocarev, Construction of Markov partitions in PL1D maps. IEEE Trans. Circuits Syst. II Exp. Briefs 60(10), 702–706 (2013)

T. Stojanovski, J. Pihl, L. Kocarev, Chaos-based random number generator–part II: practical realization. IEEE Trans. Circuits Syst. I Fundam. Theory Appl. 48(3), 382–385 (2001)

B. Widrow, I. Kollar, Quantization Noise-Roundoff Error in Digital Computation, Signal Processing, Control, and Communications (Cambridge University Press, Cambridge, 2008)

P.Z. Wieczorek, An FPGA implementation of the resolve time-based true random number generator with quality control. IEEE Trans. Circuits Syst. I Reg. Pap. 61(12), 3450–3459 (2014)

Author information

Authors and Affiliations

Corresponding author

Rights and permissions

About this article

Cite this article

Fatemi-Behbahani, E., Ansari-Asl, K. & Farshidi, E. A New Approach to Analysis and Design of Chaos-Based Random Number Generators Using Algorithmic Converter. Circuits Syst Signal Process 35, 3830–3846 (2016). https://doi.org/10.1007/s00034-016-0248-0

Received:

Revised:

Accepted:

Published:

Issue Date:

DOI: https://doi.org/10.1007/s00034-016-0248-0