Abstract

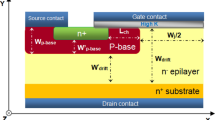

Lateral nMOSFETs have been fabricated on 4H-SiC utilizing deposited dielectrics and gate-last processing. A bi-layer dielectric was utilized consisting of thin nitrided SiO2 covered by 25nm of Al2O3 deposited using atomic layer deposition. Field-effect mobility and threshold voltage (VT) were found to vary with SiC nitric oxide (NO) anneal temperature. High peak mobility values of 106 cm2/V·s were obtained, with a corresponding VT of 0.8 V, using an 1175°C 20 min NO anneal of the SiC before Al2O3deposition. Constant voltage stressing (CVS) of the gate (3 MV/cm) for 1000s induces a VT increase of only 0.12 V for the devices stressed at RT, whereas a VT.shift of 0.34 V occurs for devices stressed at 150°C. Heating unstressed devices to 200°C reveals a stable VTwith temperature. Negative charge in the gate region allows for the attainment of positive VT while VT stability does not suffer.

Similar content being viewed by others

References

S. Dhar, S. Wang, J.R. Williams, S.T. Pantelides, and L.C. Feldman, MRS Bull. 30, 288 (2005).

V.V. Afanas'ev, F. Ciobanu, S. Dimitrijev, G. Pensl, and A. Stesmans, J. Phys.: Condens. Matter 16, S1839 (2004).

G.Y. Chung, C.C. Tin, J.R. Williams, K. McDonald, R.K. Chanana, R.A. Weller, S. T. Pantelides, L.C. Feldman, O.W. Holland, M.K. Das, and J.W. Palmour, IEEE Electron Device Lett. 22 (4), 176 (2001).

C.-Y. Lu, J.A. Cooper Jr, T. Tsuji, G. Chung, J.R. Williams, K. McDonald, and L. C. Feldman, IEEE Trans. Electron Dev., 50 (7), 1582 (2003).

A.J. Lelis, D. Habersat, R. Green, A. Ogunniyi, M. Gurfinkel, J. Suehle, and N. Goldsman, IEEE Trans. Electron Devices, 55 (8), 1835 (2008).

C.-M. Zetterling, M. Östling, H. Yano, T. Kimoto, H. Matsunami, K. Linthicum, and R. F. Davis, Mat. Sci. Forum 338-342, 1315 (2000).

C.M. Tanner and Y.-C. Perng, C. Frewin, S.E. Saddow, and J.P. Chang, Appl. Phys. Lett. 91, 203510 (2007).

G. Pensl, S. Beljakowa, T. Frank, K. Gao, F. Speck, T. Seyller, L. Ley, F. Ciobanu, V. Afanas'ev, A. Stesmans, T. Kimoto, and A. Schöner, Phys. Stat. Sol. (b) 245 (7), 1378 (2008).

T. Hatayama, S. Hino, N. Miura, T. Oomori, and E. Tokumitsu, IEEE Trans. Electron Dev. 55 (8), 2041 (2008).

H.N. Alshareef, M. Quevedo-Lopez, H.C. Wen, R. Harris, P. Kirsch, P. Majhi, B.H. Lee, R. Jammy, D. J. Lichtenwalner, J. S. Jur, and A. I. Kingon, Appl. Phys. Lett. 89, 232103 (2006).

B.-M. Lee, D.J. Lichtenwalner, M. Agustin, R. Arghavani, X. Tang, S. Gandikota, V. Ku, and V. Misra, ECS Trans. 13, 123 (2008).

R. Suri, B. Lee, D J. Lichtenwalner, N. Biswas, and V. Misra, Appl. Phys. Lett. 93, 193504 (2008).

J.H. Stathis and S Zafar, Microelectron. Reliab. 46, 270 (2006).

F. Allerstam, H. Ö. Ólafsson, G. Gudjónsson, D. Dochev, E.Ö. Sveinbjörnsson, T. Rödle and R. Jos, J. Appl. Phys. 101, 124502 (2007).

Author information

Authors and Affiliations

Rights and permissions

About this article

Cite this article

Lichtenwalner, D.J., Misra, V., Dhar, S. et al. Gate Stack Reliability of high-Mobility 4H-SiC Lateral MOSFETs with Deposited AI2O3 Gate Dielectric. MRS Online Proceedings Library 1195, 155–160 (2009). https://doi.org/10.1557/PROC-1195-B04-03

Published:

Issue Date:

DOI: https://doi.org/10.1557/PROC-1195-B04-03