Abstract

Quantum dot cellular automata (QCA) is a emerging nanotechnology that promises smaller size and lower power consumption, with faster speed compared to the transistor-based technology. In this paper, we have proposed novel 8-into-3 bit simple encoder, 4-into-2 bit priority encoder, scan flip-flop, and pseudo-random bit sequence generator designs in QCA. These circuits are useful components for the design of many logical and functional circuits. Simulation results of the proposed QCA circuits are obtained by using the QCA designer tool. The correctness of the proposed circuits is hence confirmed.

Similar content being viewed by others

Avoid common mistakes on your manuscript.

Background

Complementary metal-oxide-semiconductor (CMOS) technology is in rampant use in current-day semiconductor fabrication. But there is a paradox in CMOS that power consumed increases with increase in speed. But some applications require more speed and less power. New technologies like carbon nanofield effect transistor and quantum dot cellular automata (QCA) have the capability to provide more integration and speed along with less power consumption and high parallel processing [1, 2]. An encoder is a digital circuit that has two n input lines and n output lines. Corresponding to the input value, binary codes are generated by output lines [3]. A priority encoder is an encoder circuit named so because it carries out the priority function, i.e., in case more than one inputs are equal to 1 and at the same time, precedence will be given to the input having the highest priority. Scan flip-flop contains a multiplexer (MUX) to select either a normal operation with data input or scan operation with scan input [4]. It has a control input to select either data or scan input. It is bigger than normal flip-flop (as MUX is included here).It adds nearly 20% to 30% of area per flip-flop. This paper deals with the QCA implementation of some of these combinational and sequential circuits.

QCA basics

QCA cells

The principle of quantum dot cellular automata was first proposed by Prof. CS Lent [1]. In order to implement a system that encodes information in the form of electron position, it becomes necessary to construct a vessel in which an electron can be trapped and ‘counted’ as present or absent.

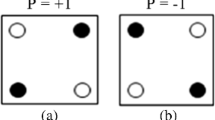

As shown in Figure 1, a quantum dot does just this by establishing a region of low potential surrounded by a ring of high potential. In ordinary form, this technology is based on bi-stable QCA cell’s interaction. The cell is constructed from four quantum dots and charged with two free electrons, which are able to tunnel between adjacent dots [5]. These electrons tend to occupy antipodal sites as a result of their mutual electrostatic repulsion. Thus, there exist two equivalent energetically minimal arrangements of the two electrons in the QCA cell, as shown in Figure 1. These two arrangements are denoted as cell polarization. By using cell polarization to represent logic ‘1’ and to represent logic ‘0’, binary information is encoded in the charge configuration of the QCA cell.

QCA wires

Other important component in QCA designing is the wire. In a QCA wire, the propagation of binary signal takes place from input to output due to the electrostatic interactions between cells. Since the polarization of each cell tends to align with that of its neighbors, a linear arrangement of standard cells is used to transmit binary information from one point to another [6, 7]. In this wire, all free cells align in the same direction as the driving cell (input cell), so the information contained in the state of the input is transmitted down the wire. Besides, the separation between dots and cells is a key parameter giving Coulombic effect in QCA application in conventional form.

A QCA wire is shown in Figure 2. Moreover, in a QCA wire, all of the computational power is provided by the Coulomb interaction between cells in absence of electrical current flow between cells and hence no power dissipation. Similar to the binary wire, there is another type of wire that is used to transfer data from one place to another. This is called inversion chain. In an inversion chain all the QCA cells are 45° rotated from the normal QCA cells. Each cell of the chain inverts the signal due to Coulombic forces between the electrons. Hence, depending on the number of cells between input and output, the output can be same or the inverted value of the input [8]. For wire crossover, it uses a total of three layers for designing crossovers as shown in Figure 3. The multilayer crossover appears conceptually simple but there are questions about its realization, since it requires two overlapping active layers.

QCA clock zones

QCA circuits require a clock to function properly. QCA clocks change the tunneling barrier between quantum dot so as to facilitate the movement of electrons within a cell and allow them to change their configuration in a predefined manner [9]. There are two types of switching of tunneling barrier possible, which are adiabatic and abrupt. In adiabatic switching the tunneling barriers among the dots are raised slowly to bring the cell in a fixed polarization. Similarly, the barriers are lowered slowly to make electrons free to move among the quantum dots. Adiabatic switching is preferred over abrupt switching because it ensures that at every point of time during the operation, the circuit will remain in a ground (stable) state and will not move to an excited state permanently [10, 11]. In this work we have used adiabatic switching in clocks. There are four QCA clocks, namely, clock 0, clock 1, clock 2, and clock 3 as shown in Figure 4. Each clock has four parts which are high level, falling edge, low level, and rising edge.

These phases are named hold, release, relax, and switch, respectively. Figure 4 shows the four phases of clock. The main function of QCA clocks is to ensure the proper transfer of the data from one place to another in a circuit [12]. During the hold state the tunneling barrier of the quantum dots is high; hence, electrons are highly localized and have a fixed polarization. During the release state, the tunneling barrier is decreased and electrons slowly become free to move. In the relax state electrons are completely free to tunnel among quantum dots and do not have any influence on the neighboring cells. In the switch state the tunneling barrier is slowly raised constraining the electrons to the most stable state [13, 14].

Majority gate and inverters

Any QCA circuit can be efficiently built using only majority gates and inverters. Figure 5 shows a majority gate with three inputs, i.e., A, B, and C, and output M (A, B, and C). A majority gate performs following function: Maj (A, B, C) = AB + BC + CA. AND and OR gates can be constructed using the majority gate easily by assigning one of the inputs to the majority gate as 0 and 1, respectively [15]. Figure 6 shows the QCA layout of inverter.

Proposed designs

The 8-3bit simple encoder

Figure 7 shows the QCA design of 8:3 bit simple encoder where D0 to D7 are inputs and Y0, Y1, and Y2 are outputs, respectively. Figure 8 shows the simulation result of proposed circuit.

The 4–2 bit priority encoder

Priority encoders are used in a number of computer systems as well as other applications. For example, when several processes, modules, or units request a single hardware (or software) resource, a decision has to be made to allow a single request to use such a resource. The priority encoder implements a fixed selection function where the resource is granted to the request with the highest priority. The basic function of a 4-bit priority encoder is to convert the 4-bit input into a binary representation. If the input n is high, all lower inputs (n − 1… 0) are ignored. In Figure 9, D1, D2, D3, and D4 are four inputs respectively, and Y1, Y2, and V are outputs. Figure 10 shows the simulation result of the proposed circuit.

Scan flip-flop

Flip-flops and latches are fundamental building blocks of sequential digital circuits. Due to significant inter- and intra-die process variations, it is necessary to ensure correct logical and temporal functionality, so we need to carry out both functional as well as timing checks on the fabricated design [16]. Figure 11 shows the block diagram of a scan flip-flop, along with the D flip-flop it replaces. It consists of a multiplexer and a D flip-flop. A and B are the inputs of the multiplexer and S acts as a select signal. The S signal is low during normal operation of the scan flip-flop. In scan mode SE is high. Now the D input of the flip-flop is driven by the scan-in signal B. They are very similar to the flip-flops with an additional enable pin, enabling them to function both as an ordinary (operating mode) flip-flop as well as the scan flip-flop(testing mode). They are used during testing and are much preferred over built-in self-test units. Figure 12 shows the QCA layout of scan flip-flop where A and B are input to MUX and S is select pin. The output of MUX is input to D flip-flop and Q is the output. Figure 13 shows the simulation result of proposed design.

The 3-bit PRBS generator

An N-bit pseudo-random binary sequence (PRBS) is a binary sequence and random in a sense that the value of any element is independent of all other elements’ values, similar to real random sequences, and pseudo because it starts to repeat itself after every N elements. PRBS can be used for supplying known binary sequences which are used as test signals for making bit error measurement. Figure 14 shows the QCA design of proposed PRBS generator.

Results and discussion

Circuits use lesser number of cells compared to traditional circuits and are more densely packed. These circuit designs have been simulated using QCA designer and the results are shown. Ninety QCA cells are used to design a scan flip-flop with area of 0.19 μm2 whereas the 4–2 bit priority encoder, which contains 100 cells, has an area of 0.13 μm2. Some of the larger and complex circuits such as 8–3 bit encoder have 281 cells with total area of 0.06 μm2, and PRBS generator has 381 cells and area 0.61 μm2. These and some more basic circuit designs can be clubbed together to create more complex circuit designs such as arithmetic logic unit or ALU, field programmable gate array or FPGA. In extension to this work, a fault-tolerant majority gate can be used and hence making the circuit more suitable for physical implementation.

Conclusions

This paper has demonstrated the design of a QCA 4:2 bit priority encoder and 8:3 bit simple encoder, scan flip-flop, and PRBS. The proposed designs are significantly smaller than the same circuits using CMOS technology. The sizes of layouts are measured on the basis of size of QCA cells. All designs are carefully clocked and were functionally verified using QCA designer. Finally, in Table 1, designs are compared according to number of cells, area, and delay.

Methods

First of all, the logic behind any proposed circuit is deduced and then the circuit diagram is drawn at gate level. The gate level circuit is converted to QCA layout using majority gates, inverters, etc. as described in the above sections and then these designs are simulated in QCA designer which is the product of an ongoing research effort by the Walus Group at the University of British Columbia to create a design and simulation tool for QCA. The designer tool allows the designer to layout a QCA design and simulates it quickly. QCA designer has provided a new platform for developers; results from simulations, using this tool, have been published by many international groups [11–16]. Results obtained by this tool are then compared to theoretical values to verify the correctness of the circuit.

Authors’ information

BG is a professor in the Department of EE, IIT Kanpur. His interest lies in spintronics and semiconductor device modeling. SG and SK are third year undergraduate students in the Department of EE, IIT Kanpur. AS is pursuing his Ph.D. degree under Prof. BG at the Department of EE, IIT Kanpur. His research interests include spintronics and device modeling.

References

Wilson M, Kannangara K, Smith G, Simmons M, Raquse B: Nanotechnology: basic science and emerging technologies. London: Chapman and Hall; 2002.

Lent CS, Tougaw PD, Porod W, Bernstein GH: Quantum cellular automata. Nanotechnology 1993,4(1):49–57. 10.1088/0957-4484/4/1/004

Delgado-Frias JG, Jabulani N: A high-performance encoder with priority lookahead. IEEE Trans Circuits Syst 2000,47(9):1390–1393. 10.1109/81.883335

Kianpour M, Sabbaghi-Nadooshan R: A novel modular decoder implementation in quantum cellular automata. In IEEE International Conference on Nanoscience, Technology and Society Implications. Orissa: C. V. Raman College; 8–10 December 2011:1–5.

Sara H, Mohammad T: Keivan N An efficient quantum-dot cellular automata full-adder. Sci Res Essays 2012,7(2):177–189.

Orlov AO, Amlani I, Toth G, Lent CS, Bernstein GH, Snider GL: Experimental demonstration of a binary wire for quantum-dot cellular automata. Appl Phys Lett 1999,74(19):2875–2877. 10.1063/1.124043

Kim K, Wu K, Karri R: Towards designing robust QCA architectures in the presence of sneak noise paths. In Proceedings of the Design, Automation and Test in Europe, Munich, 7–11 March 2005 vol 2. Munich: ; 2005:1214–1219.

Heumpil C, Swartzlander EE: Adder designs and analyses for quantum-dot cellular automata. IEEE Trans Nanotechnol 2007,6(3):374–383.

Hema Sandhya J, Mousumi S, Pavan Kumar J: Quantum dot cellular automata based effective design of combinational and sequential logical structures. World Acad Sci Eng Technol 2011, 60: 671–675.

Walus K, Jullien G: Design tools for an emerging technology: quantum-dot cellular automata. Proc IEEE 2006,94(6):1225–1244.

Walus K, Jullien G, Dimitrow V: Computer arithmetic structures for quantum cellular automata. In Conference Record of the Thirty-Seventh Asilomar Conference on Signals, Systems and Computers. : Pacific Grove; 9–12 November 2003:1435–1439.

Orlov A, Islamshah A, Kummamuru RK, Ramasubramaniam R, Toth G, Lent CS, Bernstein GH, Snider GL: Experimental demonstration of clocked single-electron switching in quantum-dot cellular automata. Appl Phys Lett 2000,77(2):295–297. 10.1063/1.126955

MostafaRahimi A, Kavehei O, Navi K: A novel design for quantum-dot cellular automata cells and full adders. J Appl Sci 2012, 7: 3460–3648.

Walus K, Schulhof G, Jullien GA: High level exploration of quantum-dot cellular automata (QCA). Conf. Rec. 38th Asilomar Conf. Signals, Systems and Computers, Pacific Grove 7–10 November 2004, 3033.

Townsend WJ, Abraham JA: Complex gate implementations for quantum dot cellular automata. Proc. 4th IEEE Conference Nanotechnology, Pacific Grove 16–19 August 2004, 625–627.

Kumar R, Bollapalli KC, Garg R, Soni T, Khatri SP: A robust pulsed flip-flop and its use in enhanced scan design. In IEEE International Conference on Computer Design 2009, ICCD 2009. Lake Tahoe: ; 4–7 October 2009:97–102.

Acknowledgment

We express our thanks to Mr. DiwakarAgarwal, alumnus of IIT Kanpur, for his help in understanding the basics of QCA technology and simulation.

Author information

Authors and Affiliations

Corresponding author

Additional information

Competing interest

The authors declare that they have no competing interests.

Authors’ contributions

SK designed the logic of proposed circuits and SG simulated them on QCA designer, and both of them drafted the manuscript. BG verified the simulation result. AKS helped in literature study and in modifying the manuscript. All authors read and approved the final manuscript.

Authors’ original submitted files for images

Below are the links to the authors’ original submitted files for images.

Rights and permissions

Open Access This article is distributed under the terms of the Creative Commons Attribution 2.0 International License ( https://creativecommons.org/licenses/by/2.0 ), which permits unrestricted use, distribution, and reproduction in any medium, provided the original work is properly cited.

About this article

Cite this article

Ghosh, B., Gupta, S., Kumari, S. et al. Novel design of combinational and sequential logical structures in quantum dot cellular automata. J Nanostruct Chem 3, 15 (2013). https://doi.org/10.1186/2193-8865-3-15

Received:

Accepted:

Published:

DOI: https://doi.org/10.1186/2193-8865-3-15