Abstract

Rapid and reproducible assembly of aligned nanostructures on a wafer-scale is a crucial, yet one of the most challenging tasks in the incorporation of nanowires into integrated circuits. We present the synthesis of a periodic nanochannel template designed for electrochemical growth of perfectly aligned, rectangular nanowires over large areas. The nanowires can be electrically contacted and characterized in situ using a pre-patterned multi-point measurement platform. During the measurement the wires remain within a thick oxide matrix providing protection against breaking and oxidation. We use laser interference lithography, reactive ion etching and atomic layer deposition to create cm-long parallel nanochannels with characteristic dimensions as small as 40 nm. In a showcase study pulsed electrodeposition of iron is carried out creating rectangular shaped iron nanowires within the nanochannels. By design of the device, the grown wires are in contact with an integrated electrode system on both ends directly after the deposition. No further processing steps are required for electrical characterization, minimizing the risk of damage and oxidation. The developed nanowire measurement device allows for multi-probe resistance measurements and can easily be adopted for transistor applications. The guided, in-plane growth of electrodeposited nanowire arrays which are tunable in size and density paves the way for the incorporation of nanowires into a large variety of multifunctional devices.

Export citation and abstract BibTeX RIS

1. Introduction

After 20 years of intensive research on one-dimensional nanostructures, we are now on the edge of being able to use nanowires for industry purposes. Several publications have been made exploring their fundamental properties and their broad range of potential applications. In particular, one-dimensional nanostructures have been used for nanowire transistors [1–3], whereas Lavrijsen, Allwood and Cowburn et al have developed logic concepts and models for storage of multiple bits within one nanowire [4–6]. On the field of thermoelectrics enhanced performance due to confinement effects has been theoretically discussed and reported [7, 8]. For industry oriented designs it is crucial to be able to accurately position nanostructures into large arrays and naturally there is an everlasting quest for cheap and rapid production, while maintaining a high durability of the fabricated devices [9, 10]. Menke et al coined the phrase of lithographically patterned nanowire electrodeposition by presenting an approach that combines surface machining and electrodeposition [11]. Nanowires fabricated using this or similar approaches have already been used for multifunctional sensing devices [12–14]. A large number of other methods for nanowire growth exist, such as vapor–liquid–solid growth [15–17], pulsed laser deposition [18] and the very common template assisted electrodeposition [19–22]. Hundreds of publications which are closely related to the electrodeposition of nanowires are published every year. Apart from a limited number of exceptions in which nanowires are contacted post-growth with two-point contacts within their vertical synthesis template [23–25], all of these techniques have in common that nanowires have to be transferred from their template of growth and placed on a substrate before electrical characterization or device fabrication can be carried out. This involves several processing steps and depending on the growth method, at least one chemical etching step [26] or a method of picking up [27] the wires from the substrate. If the wires need to be aligned, different methods using electric or magnetic fields as well as elaborate nanowire printing systems have been reported [3, 9]. However, none of these methods can achieve perfection and all of these methods can damage or alter the nanowires. In any case, photolithography becomes necessary for the connection process. The electrical connection between electronics and nanowires can either be established by time-consuming and often challenging e-beam lithography or by direct lithography [28]. Unless all synthesis steps can be successively conducted without a vacuum break, the sample is exposed to ambient air, humidity or process chemicals which can lead to unwanted oxidation or etching of the nanowires. In the case of bismuth nanowires for example, a strong surface oxide layer is formed upon release from the template which needs to be removed before an ohmic contact between the deposited contact pads and the wire becomes possible [29, 30]. In summary, all these steps until its final incorporation into a measurement device pose a significant challenge. The question we seek to answer is how the whole procedure can be simplified.

Herein, we present a novel template design that comes with a two-fold advantage: if a limited number of nanowires need to be grown for material characterization, all of the outlined difficulties can be overcome and the characterization is greatly facilitated. Additionally, the approach opens up the possibility to create wafer-scale arrays of parallel nanowires.

Our approach is based on the use of a periodic nanochannel template similar to those frequently used in micro- and nanofluidics [31–34]. However, we do not aim to investigate the fluidic properties, but rather to use these kinds of templates for nanowire fabrication, similar to the works of Pevzner et al, who used VLS-deposition techniques [35]. In contrast to other approaches for in-plane nanowire growth, this has the advantage that the growth direction of the nanowires is perfectly deterministic and confined in all directions but in length, which guarantees a high structural homogeneity. Electrodeposition is known to produce nanowires of excellent quality and since our nanowires have a rectangular cross section, they become particularly interesting from a magnetic point of view [24]. The production of the lithographically defined nanowire arrays is cheap, rapid, requires only standard laboratory equipment and no strongly toxic chemicals. Thus, the whole process can easily be scaled to industrial sized device fabrication.

The idea behind the setup is to pattern a pair of flat electrodes onto a substrate prior to the fabrication of an in-plane nanochannel structure on top of these using a sacrificial-layer method [36–38]. This layer is patterned using UV laser interference lithography (LIL) and reactive ion etching (RIE). Subsequently it is covered by atomic layer deposition (ALD). One of the electrodes serves as a cathode in an electrodeposition process, which triggers nanowire growth within the nanochannel system. Once the second electrode is reached during wire deposition, the process is intentionally stopped and by then, electric contact on both ends of the nanowire has been established. The dimensions of the wires are tunable in width, thickness and length by modifying the shape of the nanochannels and the arrangement of the electrodes. Electric measurements can be performed in situ, since there is no need of any additional processing steps. During the measurements the nanowires may remain inside the template which protects the wires against oxidation and physical damage. Still, any contact structure for example for multi-probe measurements, thermometers and source–drain layouts can be incorporated into a single system-on-chip device.

2. Results and discussion

The synthesis route of our template is displayed in figure 1.

Figure 1. Left: schematic of the synthesis route. Note that all proportions are severely distorted for easier understanding. Right: colored SEM images of the corresponding processing steps. Image (vii) shows short rectangular 80 × 80 nm2 nickel wires which are connected on one side only. The surrounding Al2O3 template was chemically etched in 0.1 M NaOH.

Download figure:

Standard image High-resolution imageFor our showcase device, an electrode design for four-probe measurements is drawn in a positive photoresist layer by means of direct laser writing lithography. After sequential sputtering of Cr (adhesion promoter) and a thin Au layer, the photoresist is lifted off with acetone leaving the contact electrode platform on the substrate. Two of the contact pads are designed to function as the working electrode in the later electrodeposition process. The width of the contact pads is made large enough (∼1 cm) to ensure easy connectability to the potentiostat (figure 1(i)).

Subsequently, a stack consisting of four different layers is prepared in the following order (figure 1(ii)): (1) spin coating of a sacrificial polymer layer. A suitable polymer is chosen and the spin rate is adjusted to get the desired thickness from 40 nm up to approximately 1 μm. The thickness of this layer determines the height of the nanochannels. Note that any polymer can be used, provided it withstands all further processing steps and can be removed selectively. (2) Sputtering of a thin SiO2 layer acting as a hard mask for pattern transfer. (3) Spin coating of an anti-reflective coating which is necessary for interference lithography [39]. The spin rate is adjusted to obtain the desired thickness. (4) Spin coating of positive photoresist.

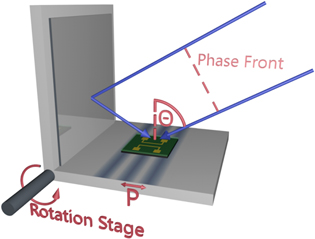

The photoresist is exposed using a LIL setup based on the Lloyd's-mirror configuration (figure 2) [39, 40], however an e-beam setup is equally suitable for the line pattern writing. LIL offers great advantages over common illumination techniques with regard to production speed, since wafer-scale areas can be processed in a single exposure. Another upside of LIL is its ability to create significantly smaller feature sizes than any other optical apparatus using the same wavelength, thus greatly reducing the cost for lasers and optics [41]. The interference pattern of a single exposure with one mirror consists of an array of parallel lines with a periodicity given by

Figure 2. Laser interference lithography setup in the Lloyd's mirror configuration. The blue arrows represent the incident light's k-vectors. The periodicity P is dependent on the angle θ between incident light and the sample's surface normal. It can be changed by rotating the stage with respect to the phase front.

Download figure:

Standard image High-resolution imageA rotation of the stage with respect to the incoming laser light (wavelength λ) modifies the incident angle θ and hence the periodicity can be tuned. The theoretical lower limit of 133 nm is defined by the wavelength used. The realistic upper limit of our setup is 1000 nm, since the area which is exposed with an interference pattern shrinks as θ approaches zero and the incoming light becomes increasingly parallel to the mirror. The substrates are aligned in a way that the line pattern is formed perpendicular to the gold contacts. During the development step the exposed photoresist is removed, leaving stripes of unexposed photoresist (figure 1(iii)). A change in periodicity causes a proportional change in the stripes width. However, further control of their width can be achieved by adjusting the exposure energy dose. Since a positive photoresist is used, exposures with a higher energy dose by longer exposure times or increased laser power can be used to significantly narrow the stripes. Consequently, the width and density of nanochannels can be tuned independently within the mentioned periodicity limits (figures 3(a) and (b).

Figure 3. SEM images of square nanochannels and nanowires. All scale bars correspond to 400 nm. (a) Overview of equally sized 80 × 80 nm2 channels with inter-channel distances of 200 nm, 300 nm and 400 nm respectively, created by a combination of tilting the interferometer stage, overexposure and isotropic etching. (b) Flat 80 × 350 nm2 nanochannels with 850 nm periodicity (c) Close up image of square 200 × 200 nm2 nickel nanowires with 400 nm periodicity, (d) polymer stripes which were thinned out horizontally due to RIE with higher chamber pressure, displaying an undercut under the SiO2 hardmask and (e) ultra-small nanochannels with dimensions less than 40 × 40 nm2 and 200 nm periodicity.

Download figure:

Standard image High-resolution imageInterference lithography is usually conducted in flat and polished substrates. Since our substrate is patterned with a thin gold electrode which can hamper the LIL process, we ensure the continuity of the photoresist stripes along the different parts of the electrodes by carefully tuning the multilayer stack. The sacrificial layer smoothens steps created by the gold electrodes and minimizes unwanted reflectivity changes near the electrodes. There are two additional reasons for incorporating this extra layer plus the RIE step (figure 1(iv)): RIE is used in order to achieve perfectly rectangular nanochannels and to improve the nanochannels' sidewall and upper surface quality, since photoresist patterns often exhibit a significant surface roughness. Most importantly, by etching under isotropic conditions the sacrificial polymer can be thinned in horizontal direction (figure 3(d)). Using this undercut effect, feature sizes beyond the diffraction limit (figure 3(e)) can be achieved.

However, the use of an additional sacrificial layer and a SiO2 hard mask as described here is not mandatory and can be left out for easier synthesis. Güder et al and Peeni et al have presented similar approaches for nanochannel creation by directly using the patterned photoresist as sacrificial layer [36, 42].

The pattern is transferred into the sacrificial layer by a sequential RIE procedure. The samples are first exposed to an oxygen plasma to remove the upper organic anti-reflective coating layer. The thereby exposed underlying SiO2 hard mask is selectively etched by an CHF3 plasma. Stripes of SiO2 remain un-etched under the photoresist acting as a hard mask for a second oxygen plasma etching which transfers the line pattern into the sacrificial layer and removes the remaining photoresist on top of the silica hard mask. As a result, perfectly rectangular polymer stripes with a thin top layer of SiO2 remain.

The patterned sacrificial layer is subsequently conformally coated by a thick layer of aluminum oxide deposited by ALD (figure 1(v)). ALD is ideally suited to mold the polymer stripes perfectly at low temperatures due to self-limiting surface reactions. The organic sacrificial layer is then completely removed from the channels by calcination in air (figure 1(vi)).

By a combination of overexposure during LIL and RIE under isotropic conditions, the smallest channels which were synthesized have a cross section of less than 40 × 40 nm2 (figure 3(e)), while still preserving the square shape and the periodicity with high homogeneity.

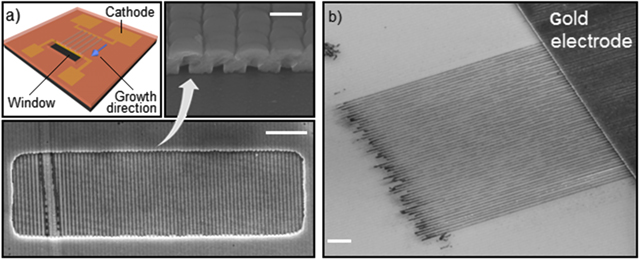

In order to carry out the electrodeposition within the nanochannels, either simple mechanical scratching by hand and a scalpel or more accurate laser writing lithography followed by selective etching is used to open a small window in the desired place in the Al2O3 layer. The size of the window is tunable so that the amount of opened nanochannels (>five) can be defined at will. The window enables the electrolyte to enter the nanochannels (figure 4(a)). Optical microscopy reveals that capillary force drags liquid along the nanochannels which are oriented perpendicular to the electrode front (figure 5), here displayed on large nanochannels of approximately 250 × 250 nm2 in cross section and 820 nm periodicity for easier optical imaging. We observe the same behavior in small channels; however, the movement of the liquid is at much greater speed and cannot be captured.

Figure 4. (a) Schematic illustration and SEM images of an electrolyte window displaying selective opening of a limited number of nanochannels. Scale bars correspond to 400 nm (top) and 4 μm (bottom). The larger electrode in the schematic is used as a working electrode (cathode) in the electrodeposition process. (b) Tilted SEM view (45°) of a parallel nanowire array. Scale bar is 2 μm.

Download figure:

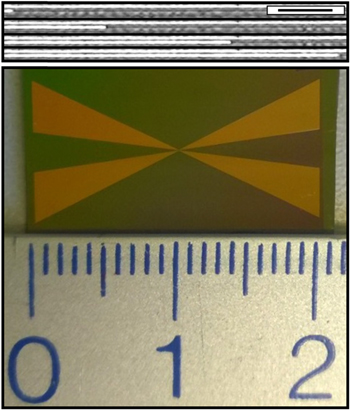

Standard image High-resolution imageFigure 5. Top: optical microscopy of liquid dragged along the nanochannels (250 × 250 nm2 with 800 nm periodicity) due to capillary force. Images are taken with 3 s in between each. Scale bar corresponds to 10 μm. Bottom: digital photograph of a sample used for four-probe magnetoresistance measurements. The channels are oriented from top to bottom.

Download figure:

Standard image High-resolution imageThe gold electrode on the opposite side of the previously opened window is electrically connected as explained in the experimental section and used as the working electrode (figure 4(a)) in a standard electrodeposition setup with three electrodes. Upon application of a correct voltage, the metal ions in the electrolyte are reduced at the working electrode and thus nanowire growth starts in direction towards the window. Pulsed electrodeposition is carried out to assure homogenous growth (figure 4(b)) [19]. The deposition is time-controlled and continues until the nanowires reach the second electrode, assuring electrical contact for later measurements. The length of the wires is limited to approximately 100 μm, since the electrolyte circulation becomes more limited, the longer the distance is between the electrode and the window.

On the first sight our route might seem complex as compared to sputtering of the nanowires directly after the lithographic step [43]. There are several reasons why we believe our route offers great advantages: achieving larger thicknesses in narrow pitches by sputtering is difficult, since it may prevent the lift-off procedure from working. Additionally, in periodic structures and as the feature sizes get smaller, the sputtered material tends to accumulate on top of the photoresist stripes rather than in the trenches [44]. By using electrodeposition, the wires can be precisely placed in the desired location. Most importantly, since the wires growth direction is along their long axis (as compared to growth along their short axis when sputtered), segmented nanowires with hundreds of repeats can be grown. These kinds of nanowires become especially important in spintronics, for example in integrated spin-valve, giant-magnetoresistance and even tunnel-magnetoresistance nanowires [23, 24]. Various materials such as transition metals (Fe, Ni, Co, Cu) and semiconductors (Bi2Te3) have been grown inside the channels.

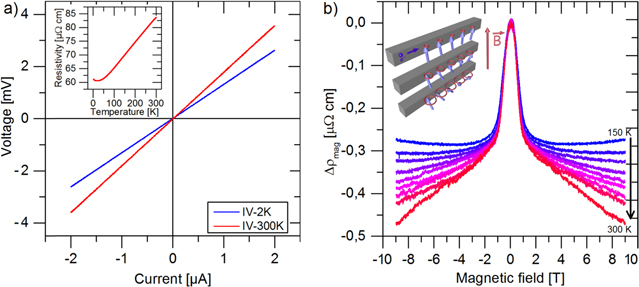

As a proof of our concept we present electrical measurements on iron nanowires (figure 6). During the in situ measurement the nanowires remain within the protecting oxide template. The sample shows perfectly linear I–V relations at 2 K and 300 K demonstrating ohmic contacts between both gold electrodes and the iron nanowire (figure 6(a)). From the perfectly linear ρ(T) behavior between 50 K and 300 K indicated in the inset in figure 6(a), we infer that our nanowires are pure metallic. Since even short exposures of iron to ambient air lead to its oxidation, we prove that our template provides full protection against corrosion. If the template needs to be removed for SEM-imaging or sensing applications, weak 0.1 M KOH can be used.

Figure 6. (a) I–V curves of electrodeposited iron nanowires (70 × 80 × 12 000 nm3) grown and characterized within the nanochannels template. The inset shows the temperature dependent resistivity which is approximately nine times higher than the resistivity of bulk iron. This is a typical behavior for thin metallic nanowires due to boundary scattering. In publications on electrical properties of single cobalt and nickel nanowires, resistivities which are seven times larger than bulk values were reported [47, 48]. A small increase for T < 15 K is observed which is attributed to localization effects. (b) Temperature dependent magnetoresistance measurements from 150 K (blue) to 300 K (red). The cartoon displays the decrease of a spin-wave's amplitude from low magnetic fields (bottom) to high magnetic fields (top), resulting in reduced s–d scattering of the conduction electrons.

Download figure:

Standard image High-resolution imageFigure 6(b) shows the high-field temperature dependent magnetoresistance. The pronounced peak at 0 T is due to the anisotropic magnetoresistance effect, while the negative dependence between resistance and magnetic field for  is attributed to a magnon freeze out [45, 46]. An in-depth discussion of the temperature dependent magnon contribution and the electrical characteristics of electrodeposited Fe nanowires will follow in a future publication.

is attributed to a magnon freeze out [45, 46]. An in-depth discussion of the temperature dependent magnon contribution and the electrical characteristics of electrodeposited Fe nanowires will follow in a future publication.

3. Conclusion

In summary, we have developed a technique for rapid synthesis of parallel electrodeposited nanowires by a combination of LIL, RIE and ALD. Our approach allows for the fabrication of highly resistant and versatile templates. With the proposed synthesis route, feature sizes well-below the diffraction limit of the used wavelength can be achieved. In a model system we demonstrate the electrodeposition and electrical characterization of oxidation sensitive Fe nanowires. The presented approach can easily be extended to various application fields, such as biological and chemical sensors, racetrack memories, gate–voltage dependent measurement devices as well as electrical and magneto-optical characterization of 1D nanostructures. Wafer-scale arrays of well-positioned, parallel nanowires can be created, opening up the possibility for production of large amounts of nanowire–transistors and their incorporation into MOSFET designs.

While the fabrication of the template system alone is indeed more complex than producing anodic alumina templates or polycarbonate membranes, the discussed advantages in our opinion outweigh. In fact, the total amount of work necessary for fabrication, device creation and characterization of nanowires is strongly reduced. Additionally, the fabrication consists of only three major steps which are well-established, fast, highly reproducible and compatible with 'assembly-line' like production.

Finally, our approach can be used to create nanowires with tailor-made, rectangular magnetic and non-magnetic segments, thus selectively introducing stable transversal anisotropy within one nanowire. The possibility of using these as shift registers for the storage of multiple bits of data within one nanowire will be explored in a future publication.

4. Experimental section

4.1. Template fabrication.

Si<100> wafers coated with 100 nm thick thermally grown silicon dioxide layer (Si-Mat) are used as substrates. For electrode patterning 500 nm ma-P 1205 positive photoresist is used (Microchemicals GmbH) and illuminated with a direct lithography setup consisting of a 405 nm wavelength laser with 1 μm spot and a movable stage (μPG 101 LaserWriter from Heidelberg Instruments Mikrotechnik GmbH). Electrodes are sputtered with 5 nm Cr as an adhesive promoter and 30 nm Au using a 308 R Coating System (Cressington Scientific Instruments). The layer stack in our experiments is built up by spin coating 35–90 nm GenARC 266 (Brewer Science) or 120–250 nm PMMA/MA 317.04 (Allresist GmbH) as a sacrificial layer, RF-Sputtering of 30 nm SiO2 as a hard mask using a CRC-300 (Torr International), spin coating 35–90 nm of GenARC 266 as an anti-reflective coating for the LIL followed by 200 nm UV2000 (Rohm and Haas Electronic Materials) positive photoresist. The required thickness of the anti-reflective coating is calculated using the program Multilayer Reflectivity by Michael E. Walsh in order to minimize the reflected power at the interface between photoresist and anti-reflective coating [39]. The exposure is conducted in a self-built LIL setup. The laser used in this work is a FQCW 266-50 (CryLas GmbH) with 266 nm wavelength and 50 mW output power. RIE is conducted with a Si220 (Sentech Instruments GmbH) using an oxygen plasma for 60 s (10 mTorr chamber pressure, 10 sccm mass flow rate and 75 W power), followed by a CHF3 plasma for 230 s (10 mTorr, 25 sccm CHF3, 75 W) respectively. Depending on the thickness of the sacrificial layer, the last RIE step is conducted at the required times under above conditions. Increasing the chamber pressure during oxygen plasma etching to 25 mTorr as well as the etching time creates undercuts below the SiO2 hardmask. ALD of Al2O3 is conducted in a TFS200HP (BENEQ Oy) reactor using tri-methyl aluminum and water precursors, both kept constant at 20 °C with opening times of 250 ms and 500 ms respectively. The chamber temperature is set to 150 °C. The deposition is carried out in stop-mode operation with exposure times of 10 s, pump times of 10 s and approximately 1200 total cycles. A local electrolyte window either scratched mechanically by a scalpel or etched in 5% phosphoric acid at 45 °C for two hours before the sacrificial polymer is removed by calcination in air at 350 °C for at least 24 h at a heating rate of 1 °C min−1.

4.2. Nanowire growth.

For the growth of iron nanowires by pulsed electrodeposition [19] an iron sulfate bath is used consisting of boric acid (4.5 g l−1), glycine (12.2 g l−1), ascorbic acid (1.0 g l−1) and iron(II) sulfate heptahydrate (4.5 g l−1). Prior to electrodeposition, the electrolyte is bubbled with argon gas to avoid changes in the oxidation state of the iron ions [20]. A three-electrode cell with an Ag/AgCl/KClsat reference electrode and a platinum wire as counter electrode is used. The electrode which is patterned on the substrate is connected on two ends and acts as the working electrode. One end serves as a conduction line for the current while the other serves as a measurement point of the potential directly at the location of nanowire growth with respect to the reference electrode. Thus, the resistance drop along the path of the thin electrodes which could cause a change in deposition potential is not taken into account. The pulse cycles consist of a deposition pulse at −1.3 V for 10 ms followed by an off-time of 100 ms at −0.45 V in which the ion concentration is allowed to regenerate, since there is no current flow. The bath is moderately stirred and kept at 20 °C. The horizontal growth rate under these conditions inside the channels is determined to be 300 nm min−1. If the wires are to grow from one contact to another, electric contact on both ends is assured by controlling the deposition time with an ample buffer, since too long growth does not create any problems.

4.3. Electric measurements.

In order to connect the chip carrier with the sample a wire bonder is used. A thin aluminum wire is bonded to the electric contacts by applying force perpendicular to the surface plane combined with a short ultrasonic pulse. This proved to be sufficient to penetrate the layer of porous aluminum oxide channels which covers the contacts. If it is necessary to completely free the contact pads, for example if probes are used for measurement, the edges of the sample can be dipped into KOH (25%wt.) for 3 min. It is important to make sure the channels are aligned parallel to the etching liquid surface, to make sure capillary forces do not drag the solution into the matrix, possibly reaching the grown wires. If the contact structure is made large enough in beforehand (approx. 2 × 2 cm2), this procedure can be done with ease and without risk of damaging the wires (example structure figure 5). In our example we use a four-point measurement setup to characterize the magnetoresistance of a single Fe-nanowire using a PPMS Dynacool (Quantum Design) cryostat. SEM characterization (Zeiss Sigma) reveals that only one nanowire is connecting both sides of the electrodes, since the growth rates in neighboring pores was slightly slower. The surrounding template does not need to be removed for imaging, since the contrast difference between a pore that contains a wire and an empty one is sufficient. For the measurements, an ac current (lock in freq. 128.174 Hz) is injected while the voltage drop over the nanowire is measured. The magnetic field is applied perpendicular to the nanowire.

Acknowledgments

We would like to thank Johannes Gooth and Heiko Reith for thoughtful discussions and assistance with electrical measurements.

Funding sources

The research leading to these results has received funding from the European Unions's 7th Framework Program under grant agreement n°309589 (M3d) and we gratefully acknowledge financial support from the German Research Foundation (DFG) via SFB 986 'M3', project C3.