Abstract

We investigated the lateral distribution of the equilibrium carrier concentration (n0) along the channel and the effects of channel length (L) on the source-drain series resistance (Rext) in the top-gate self-aligned (TG-SA) coplanar structure amorphous indium-gallium-zinc oxide (a-IGZO) thin-film transistors (TFTs). The lateral distribution of n0 across the channel was extracted using the paired gate-to-source voltage (VGS)-based transmission line method and the temperature-dependent transfer characteristics obtained from the TFTs with different Ls. n0 abruptly decreased with an increase in the distance from the channel edge near the source/drain junctions; however, much smaller gradient of n0 was observed in the region near the middle of the channel. The effect of L on the Rext in the TG-SA coplanar a-IGZO TFT was investigated by applying the drain current-conductance method to the TFTs with various Ls. The increase of Rext was clearly observed with an increase in L especially at low VGSs, which was possibly attributed to the enhanced carrier diffusion near the source/drain junctions due to the larger gradient of the carrier concentration in the longer channel devices. Because the lateral carrier diffusion and the relatively high Rext are the critical issues in the TG-SA coplanar structure-based oxide TFTs, the results in this work are expected to be useful in further improving the electrical performance and uniformity of the TG-SA coplanar structure oxide TFTs.

Similar content being viewed by others

Introduction

In the last decade, amorphous indium-gallium-zinc oxide (a-IGZO) thin-film transistors (TFTs) have attracted considerable attention due to their advantages such as a high field-effect mobility (μFE), a low off-current, and a small subthreshold swing1,2,3,4,5,6,7,8. In addition, the a-IGZO TFTs are fabricated at low temperatures (below 300 °C) with a good uniformity over large areas9,10. These excellent properties make the a-IGZO TFT a promising candidate for the backplane element of active-matrix liquid-crystal displays and active-matrix organic light-emitting diode (AMOLED) displays11,12. Up to now, the a-IGZO TFTs have been fabricated with several structures including a bottom-gate etch stopper structure, a bottom-gate back-channel-etch structure, and a top-gate self-aligned (TG-SA) coplanar structure7. Among them, the TG-SA coplanar structure has many advantages compared with bottom-gate structures, such as smaller parasitic capacitance, better channel length scalability, and better process controllability13,14. Owing to these merits, the TG-SA coplanar structure a-IGZO TFT is desirable especially for high-resolution AMOLED applications15,16. However, despite such advantages, there still remain some issues to be solved in TG-SA coplanar a-IGZO TFTs. One of them is the threshold voltage (Vth) dependence on the channel length of the device17,18,19. In the TG-SA coplanar a-IGZO TFTs, the source/drain extension regions are n+-doped in order to lower the source/drain series resistance (Rext). The high-density free carriers in the source/drain extension regions diffuse into the IGZO channel layer during the subsequent annealing process, which increases the carrier concentration of the channel region and shifts Vth to the negative direction especially in the short channel devices17,18,19. Therefore, the study on the lateral carrier diffusion and Rext is very important in the TG-SA coplanar a-IGZO TFTs to further improve the electrical performance and uniformity of the devices. In this work, we extracted the lateral distribution of the carrier concentration in the TG-SA coplanar a-IGZO TFTs by using the paired gate-to-source voltage (VGS)-based transmission line method (TLM) and temperature-dependent transfer characteristics data obtained from the TFTs with various channel lengths. Furthermore, we investigated the effects of channel length on the Rext of the TG-SA coplanar a-IGZO TFT using the drain current-conductance method (DCCM).

Results and Discussion

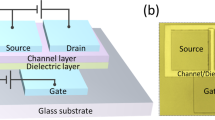

Figure 1(a) depicts a cross-sectional schematic of the fabricated TG-SA coplanar a-IGZO TFTs, where the fabrication process of the TFTs is introduced in the Methods Section. Figure 1(b) shows the schematic carrier concentration plot along the channel between the source and drain in the TG-SA coplanar a-IGZO TFTs. Near the source and drain junctions, the carriers diffuse from the n+-doped source/drain extension regions to the channel region. Solid lines represent the equilibrium carrier concentration (n0) and the dotted lines represent the VGS-induced carrier concentration at two different VGSs (VGS1 > VGS2). As can be observed in Fig. 1(b), there are two distinct regions: one is the region where VGS-induced carrier concentration is higher than n0 and the other is the region where n0 is higher than the VGS-induced carrier concentration. The conductivity in the former region is controlled by VGS, thus this region can be considered as an effective channel region. Because the effective channel ends where the VGS-induced carrier concentration is equal to n0, the effective channel length (Leff) increases with an increase in VGS. ΔL is defined as the difference between the drawn channel length (L) and Leff (ΔL = L − Leff). Rext is the source-drain series resistance associated with all the regions outside the effective channel region.

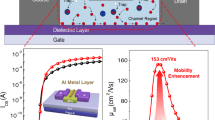

Figure 2(a) depicts the transfer curves of the TG-SA coplanar a-IGZO TFTs measured in the linear region (drain-to-source voltage (VDS) = 0.1 V). L was varied from 3 to 20 μm, while a channel width (W) was fixed at 4 μm. Figure 2(a) shows that Vth shifts negatively and the on-current increases with a decrease in L. These results are consistent with those in the previous works17,18,19 and more negative shift of Vth in the shorter channel TFT was attributed to the higher carrier concentration in the channel region caused by the carrier diffusion from the n+-doped source/drain extension regions17. Figure 2(b) displays the Vths obtained from the fabricated TG-SA coplanar a-IGZO TFTs with different Ls. Here, Vth was determined by the intercept of the extrapolated curve with the VGS axis in the linear-scale transfer characteristics.

To extract the lateral carrier concentration distribution near the source/drain junctions in the TG-SA coplanar a-IGZO TFTs, the paired VGS-based TLM20 was employed. In the TG-SA coplanar TFTs, the total resistance between source and drain electrodes measured in the linear region (Rtot) can be expressed using the following equation:

where μFEi is the intrinsic field-effect mobility and Ci is the gate insulator capacitance per unit area, respectively. Figure 3(a) shows the Rtot-L plot measured from the TFTs with different Ls (L = 6, 12, 20 μm) at a given VDS of 0.1 V for various VGSs (=1 to 5 V with 0.2 V steps). Figure 3(b) is the enlarged image of the encircled area in Fig. 3(a). In the paired VGS-based TLM, ΔL and Rext at a certain VGS are extracted from the intersection of two straight lines obtained at two closely separated voltages (VGS ± ΔVGS) where ΔVGS is 0.2 V in this work. Figure 4(a,b) show the ΔL and the width-normalized Rext (W · Rext) extracted as a function of VGS by using the paired VGS-based TLM. ΔL and Rext are largely modulated by VGS, which confirms the presence of the unintentionally doped regions formed by the lateral carrier diffusion from the n+-doped source/drain extension regions in the fabricated TG-SA coplanar a-IGZO TFTs. The results of Fig. 4(a) and the definition of Leff in Fig. 1(b) allow the extraction of the lateral carrier concentration distribution in the unintentionally doped regions near the source/drain junctions. In the TFT, the VGS-induced channel carrier concentration (n(VGS)) can be calculated using the following equation21:

where q and t are the electronic charge and channel thickness, respectively. As explained in Fig. 1(b), Leff (=L − ΔL) ends where n is equal to n0 in the TG-SA coplanar a-IGZO TFTs, therefore, ΔL is uniquely determined at a specific value of VGS by the results of Fig. 4(a). Because both n and ΔL are obtained as a function of VGS, we can extract n0 at a specific position in the unintentionally doped regions near the source/drain junctions by matching the ΔL/2 and n values calculated at every VGS. Figure 5 displays the lateral distribution of n0 in the unintentionally doped regions near the source/drain junctions in the fabricated TG-SA coplanar TFT with L = 20 μm (Vth = 1.06 V). It shows that n0 abruptly decreases from 1.5 × 1018 cm−3 to 8.2 × 1016 cm−3 as the distance from the edge of the channel (ΔL/2) increases from 0.16 μm to 1.63 μm.

The lateral carrier concentration distribution in the channel region far from the source/drain junctions can be extracted using the temperature-dependent transfer characteristics data obtained from the TFTs with different Ls. Figure 6(a–e) show the temperature-dependent linear-mode transfer curves (VDS = 0.1 V) of the TFTs with various Ls (L = 3, 4, 6, 12, 20 μm) measured at low VGSs and Fig. 7(a–e) depict the Arrhenius plots obtained from the results in Fig. 6(a–e). In the disordered semiconductor-based TFTs, the energy distance between the Fermi level and conduction band edge in the flat-band condition (EaFB = EC − EF0) has been successfully extracted using the temperature-dependent transfer characteristics according to the procedure described in the previous works22,23,24. Figure 8 shows the evolution of EaFB and n0 extracted from the TFTs with different Ls using the experimental results in Figs 6 and 7. n0 was calculated from

where nIGZO is the effective density of states at the conduction band edge in IGZO at room temperature (=5.0 × 1018 cm−3)25 and k is the Boltzmann constant, respectively. Figure 8 shows that EaFB increases and n0 decreases, with an increase in L. These results are consistent with the positive shift of Vth with an increase in L observed in Fig. 2. In the TG-SA coplanar TFT, n0 is different depending on the distance from the edge of the channel due to the carrier diffusion from the n+-doped source/drain extension regions. Considering that the carrier diffusion takes place from both source and drain regions, n0 is believed to have the lowest value in the middle of the channel. Because the Vth of the laterally non-uniformly doped TFT is determined by the lowest carrier concentration in the channel region, the calculated n0s in Fig. 8 based on the results in Figs 6 and 7 can be assumed to be the n0 in the of the middle of the channel in each TFT with different Ls. These results allow us to extract the values of n0 as a function of the distance from the edge of the channel in the channel region far from the source/drain junctions. Figure 9 shows the lateral distribution of n0 in the whole channel region of the fabricated TG-SA coplanar TFT with L = 20 μm.

Arrhenius plots obtained from the results in Fig. 6 for TFTs with different Ls ((a) 3 μm, (b) 4 μm, (c) 6 μm, (d) 12 μm, and (e) 20 μm).

Because the relatively higher Rext has been considered as a weakness of the TG-SA coplanar structure than the bottom gate structures in a-IGZO TFTs, the extraction of the exact values of Rext is very important in the TG-SA coplanar a-IGZO TFTs to further improve the electrical performance of the devices. In this work, we investigated the effects of L on the Rext of the TG-SA coplanar a-IGZO TFT for the first time using the DCCM. As given in Fig. 4(b), the Rext of the TG-SA coplanar a-IGZO TFT can be extracted not only by the DCCM but by the paired VGS-based TLM. However, because the Rexts are assumed to be the same in all TFTs with different Ls in the paired VGS-based TLM, the extracted Rext from the paired VGS-based TLM is the averaged one of the TFTs with different Ls. The DCCM was developed to extract the VGS-induced source and drain series resistance (Rext,S and Rext,D) in the lightly-doped-drain metal-oxide-semiconductor field-effect transistors26. It can extract the Rext,S and Rext,D separately by using the IDs and output conductances (GDs) measured in the forward and reverse operation modes in the linear operation regime, respectively. DCCM is to form four independent equations to solve Rext,S, Rext,D, μFE,fwd, and μFE,rev, where μFE,fwd and μFE,rev are μFEs for the forward and reverse mode operations, respectively. Equations (4) and (5) are the two of the four equations which are for the forward mode operation and equations (6) and (7) are those for the reverse mode operation.

where \({V}_{{\rm{GS}}}^{\ast }\) = VGS − ID · Rext,S and \({V}_{{\rm{DS}}}^{\ast }\) = VDS − ID · (Rext,D + Rext,S).

where ∂\({V}_{{\rm{GS}}}^{\ast }\)/∂VDS = −GD · Rext,S and ∂\({V}_{{\rm{DS}}}^{\ast }\)/∂VDS = 1 − GD · (Rext,D + Rext,S).

where \({V}_{GS}^{\ast }\) = VGS − ID · Rext,D and \({V}_{DS}^{\ast }\) = VDS − ID · (Rext,D + Rext,S).

where ∂\({V}_{GS}^{\ast }\)/∂VDS = −GD · Rext,D and ∂\({V}_{{\rm{DS}}}^{\ast }\)/∂VDS = 1 − GD · (Rext,D + Rext,S). Rext,S, Rext,D, μFE,fwd, and μFE,rev can be extracted from the measured forward and reverse mode ID and GD at any specified VGS by solving the four equations simultaneously by numerical methods. Because the DCCM requires only a single device for the extraction of Rext, it can be used to investigate the effects of L on the Rext in the TG-SA coplanar a-IGZO TFTs. Figure 10 shows the W · Rext (W · (Rext,S + Rext,D)) extracted as a function of VOV in the fabricated TG-SA coplanar a-IGZO TFT with different Ls, where VOV represents VGS − Vth. For comparison, the W · Rext extracted using the paired VGS-based TLM in Fig. 4(b) is also included as an inset. The results in Fig. 10 clearly shows that the Rext is increased with an increase in L especially at low VGSs. Considering that the Rext at low VGSs is dominated by the unintentionally doped channel regions formed by the lateral carrier diffusion from the n+-doped source/drain extension regions near the source/drain junctions, the higher Rext in the longer channel TFTs is believed to be mainly caused by the enhanced carrier diffusion (large ΔL) due to the larger gradient of the carrier concentration in the longer channel devices.

W · Rext (W · (Rext,S + Rext,D)) extracted as a function of VOV in the fabricated TG-SA coplanar a-IGZO TFT with different Ls. For comparison, W · Rext extracted using the paired VGS-based TLM in Fig. 4(b) is included as an inset.

Conclusion

In this work, we examined the lateral distribution of n0 across the channel and the effects of L on the Rext in the TG-SA coplanar a-IGZO TFTs. The lateral distribution of n0 across the channel was extracted using the paired VGS-based TLM near the source/drain junctions and using the temperature-dependent transfer characteristics data measured from the TFTs with different Ls near the middle of the channel, respectively. n0 abruptly decreased from 1.5 × 1018 cm−3 to 8.2 × 1016 cm−3 at room temperature as the distance from the edge of the channel (ΔL/2) increases from 0.16 μm to 1.63 μm in the fabricated TG-SA coplanar TFT with L = 20 μm. However, much smaller gradient of n0 was observed in the channel region far from the source/drain junctions. To examine the effect of L on the Rext in the TG-SA coplanar a-IGZO TFTs, the DCCM was employed. The Rexts were extracted from the TFTs with different Ls, which clearly showed that Rext increased with an increase in L especially at low VGSs. The observed phenomenon was possibly attributed to the enhanced carrier diffusion (large ΔL) near the source/drain junctions in the long channel devices.

Methods

An a-IGZO layer (In:Ga:Zn = 1:1:1 at%) was deposited by direct-current sputtering at room temperature on a SiO2 buffered glass substrate. A SiO2 layer was deposited by plasma-enhanced chemical vapor deposition as a gate insulator followed by the sequential deposition of a gate metal. After deposition and patterning of the gate electrode and the gate insulator, the source/drain extension regions were self-aligned to the gate and are n+-doped by being exposed to the plasma during the dry-etching process. Interlayer dielectrics were deposited and patterned for source/drain contact holes. Then, the metal layer was sputtered and patterned to form the source/drain electrodes. The TFTs were passivated by a SiO2 passivation layer. Finally, the devices were thermally annealed to achieve the stable and uniform electrical performances.

References

Nomura, K. et al. Room Temperature Fabrication of Transparent Flexible Thin-film Transistors Using Amorphous Oxide Semiconductors. Nature 432, 488–492 (2004).

Kamiya, T. & Hosono, H. Material Characteristics and Applications of Transparent Amorphous Oxide Semiconductors. NPG Asia Mater. 2, 15–22 (2010).

Kwon, J.-Y., Lee, D.-J. & Kim, K.-B. Transparent Amorphous Oxide Semiconductor Thin Film Transistor. Electronic Materials Letters 7, 1–11 (2011).

Lee, S. Y., Kim, D. H., Chong, E., Jeon, Y. W. & Kim, D. H. Effect of Channel Thickness on Density of States in Amorphous InGaZnO Thin Film Transistor. Appl. Phys. Lett. 98, 122105 (2011).

Fortunato, E., Barquinha, P. & Martins, R. Oxide Semiconductor Thin-film Transistors: A Review of Recent Advances. Adv. Mater 24, 2945–2986 (2012).

Bak, J. Y. et al. Origin of Degradation Phenomenon under Drain Bias Stress for Oxide Thin Film Transistors using IGZO and IGO Channel Layers. Sci. Rep. 5, 7884 (2015).

Kwon, J. Y. & Jeong, J. K. Recent Progress in High Performance and Reliable N-type Transition Metal Oxide-based Thin Film Transistors. Semicond. Sci. Technol. 30, 024002 (2015).

Kim, Y.-H., Lee, E., Um, J. G., Mativenga, M. & Jang, J. Highly Robust Neutral Plane Oxide TFTs Withstanding 0.25 mm Bending Radius for Stretchable Electronics. Sci. Rep. 6, 25734 (2016).

Yang, S. et al. Low-Temperature Processed Flexible In-Ga-Zn-O Thin-film Transistors Exhibiting High Electrical Performance. IEEE Electr. Device Lett. 32, 1692–1694 (2011).

Kim, W.-G. et al. High-pressure Gas Activation for Amorphous Indium-Gallium-Zinc-Oxide Thin-Film Transistors at 100 °C. Sci. Rep. 6, 23039 (2016).

Osada, T. et al. Development of Liquid Crystal Display Panel Integrated with Drivers Using Amorphous In-Ga-Zn-Oxide Thin Film Transistors. Jpn. J. Appl. Phys. 49, 03CC02 (2010).

Yoon, J.-S. et al. 55-inch OLED TV using Optimal Driving Method for Large-size Panel based on InGaZnO TFTs. SID Int. Symp. Dig. Tech. Pap. 45, 849–852 (2014).

Oh, S. et al. Comparison of Top-Gate and Bottom-Gate Amorphous InGaZnO Thin-film Transistors with the Same SiO2/a-InGaZnO/SiO2 Stack. IEEE Electr. Device Lett. 35, 1037–1039 (2014).

Choi, S. et al. Systematic Decomposition of the Positive Bias Stress Instability in Self-aligned Coplanar InGaZnO Thin-Film Transistors. IEEE Electr. Device Lett. 38, 580–583 (2017).

Bae, J. U. et al. Development of Oxide TFT’s Structures. SID Int. Symp. Dig. Tech. Pap. 44, 89–92 (2013).

Jang, Y. H. et al. Internal Compensation Type OLED Display Using High Mobility Oxide TFT. SID Int. Symp. Dig. Tech. Pap. 48, 76–79 (2017).

Kang, D. H., Han, J. U., Mativenga, M., Ha, S. H. & Jang, J. Threshold Voltage Dependence on Channel Length in Amorphous-Indium-Gallium-Zinc-Oxide Thin-Film Transistors. Appl. Phys. Lett. 102, 083508 (2013).

Ha, S. H. et al. Channel Length Dependent Bias-Stability of Self-Aligned Coplanar a-IGZO TFTs. J. Display Technol. 12, 985–988 (2013).

Kim, H. W., Kim, E. S., Park, J. S., Lim, J. H. & Kim, B. S. Influence of Effective Channel Length in Self-aligned Coplanar Amorphous-Indium-Gallium-Zinc-Oxide Thin-film Transistors with Different Annealing Temperatures. Appl. Phys. Lett. 113, 022104 (2018).

Hu, G. J., Chang, C. & Chia, Y.-T. Gate-Voltage-Dependent Effective Channel Length and Series Resistance of LDD MOSFET’s. IEEE Trans. Electron Devices. 34, 2469–2475 (1987).

Chern, H. N., Lee, C. L. & Lei, T. F. An Analytical Model for the Above-threshold Characteristics of Polysilicon Thin-film Transistors. IEEE Trans. Electron Devices. 42, 1240–1246 (1995).

Chen, C., Abe, K., Kumomi, H. & Kanicki, J. Density of States of A-InGaZnO from Temperature-dependent Field-effect Studies. IEEE Trans. Electron Devices. 56, 1177–1183 (2009).

Jeong, J., Jeong, J. K., Park, J.-S., Mo, Y.-G. & Hong, Y. Meyer-Neldel Rule and Extraction of Density of States in Amorphous Indium-Gallium-Zinc-Oxide Thin-Film Transistor by Considering Surface Band Bending. Jpn. J. Appl. Phys. 49, 03CB02 (2010).

Jeong, C.-Y., Lee, D., Han, Y.-J., Choi, Y.-J. & Kwon, H.-I. Subgap States in P-channel Tin Monoxide Thin-film Transistors from Temperature-dependent Field-effect Characteristics. Semicond. Sci. Technol. 30, 085004 (2015).

Fung, T.-C. et al. Two-dimensional Numerical Simulation of Radio Frequency Sputter Amorphous In-Ga-Zn-O Thin-film Transistors. J. Appl. Phys. 106, 084511 (2009).

Lou, C.-L., Chim, W.-K., Chan, D. S.-H. & Pan, Y. A Novel Single-device DC Method for Extraction of the Effective Mobility and Source-drain Resistances of Fresh and Hot-carrier Degraded Drain-engineered MOSFET’s. IEEE Trans. Electron Devices. 45, 1317–1322 (1998).

Acknowledgements

This work was supported by the National Research Foundation of Korea (NRF) grant funded by the Korea government (MSIP) (No. 2017R1A2A2A14001213) and in part by the Chung-Ang university Graduate Research Scholarship in 2018.

Author information

Authors and Affiliations

Contributions

S.Y. H., H.J.K., I.T.C., J.N., P.S.Y., S.W.L. and H.I.K. designed this work. I.T.C. and J.N. fabricated the devices, and S.Y.H., H.J.K., D.H.K. and H.Y.J. measured the electrical characteristics of the devices and performed the analysis. S.H.S., K.S.P., S.Y. and I.K. provided a theoretical advice for proceeding experiments. S.Y.H. and H.I.K. wrote the manuscript. The project was supervised by H.I.K.

Corresponding author

Ethics declarations

Competing Interests

The authors declare no competing interests.

Additional information

Publisher’s note: Springer Nature remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

Rights and permissions

Open Access This article is licensed under a Creative Commons Attribution 4.0 International License, which permits use, sharing, adaptation, distribution and reproduction in any medium or format, as long as you give appropriate credit to the original author(s) and the source, provide a link to the Creative Commons license, and indicate if changes were made. The images or other third party material in this article are included in the article’s Creative Commons license, unless indicated otherwise in a credit line to the material. If material is not included in the article’s Creative Commons license and your intended use is not permitted by statutory regulation or exceeds the permitted use, you will need to obtain permission directly from the copyright holder. To view a copy of this license, visit http://creativecommons.org/licenses/by/4.0/.

About this article

Cite this article

Hong, SY., Kim, HJ., Kim, DH. et al. Study on the Lateral Carrier Diffusion and Source-Drain Series Resistance in Self-Aligned Top-Gate Coplanar InGaZnO Thin-Film Transistors. Sci Rep 9, 6588 (2019). https://doi.org/10.1038/s41598-019-43186-7

Received:

Accepted:

Published:

DOI: https://doi.org/10.1038/s41598-019-43186-7

This article is cited by

Comments

By submitting a comment you agree to abide by our Terms and Community Guidelines. If you find something abusive or that does not comply with our terms or guidelines please flag it as inappropriate.