Abstract

The electronic conductivities of ferroelectric domain walls have been extensively explored over the past decade for potential nanoelectronic applications. However, the realization of logic devices based on ferroelectric domain walls requires reliable and flexible control of the domain-wall configuration and conduction path. Here, we demonstrate electric-field-controlled stable and repeatable on-and-off switching of conductive domain walls within topologically confined vertex domains naturally formed in self-assembled ferroelectric nano-islands. Using a combination of piezoresponse force microscopy, conductive atomic force microscopy, and phase-field simulations, we show that on-off switching is accomplished through reversible transformations between charged and neutral domain walls via electric-field-controlled domain-wall reconfiguration. By analogy to logic processing, we propose programmable logic gates (such as NOT, OR, AND and their derivatives) and logic circuits (such as fan-out) based on reconfigurable conductive domain walls. Our work might provide a potentially viable platform for programmable all-electric logic based on a ferroelectric domain-wall network with low energy consumption.

Similar content being viewed by others

Introduction

Domain walls (DWs) in ferroic materials have attracted intensive interest over the past decades due to their physical phenomena and potential for applications in nanoelectronics1,2 and spintronics3,4,5. Of particular interest are the designs of racetrack memory6,7 and DW logic8,9 based on moving magnetic DWs driven by a current or a magnetic field. In these cases, data storage or logic operation functions could be realized by controlling DW injection, motion, and annihilation along magnetic nanowires rather than switching magnetic domains as is traditional. Contrary to the large wall width and high energy cost in current-driven moving magnetic DWs, ferroelectric DWs possess a much smaller wall width (less than a few nanometers), and their electric-field-driven features and electric conduction are conducive to high-density integration and low-power regulation of nanoelectronic devices1,10,11,12,13,14,15,16,17,18,19,20,21,22,23,24,25. Recently, by controlling the electric conduction of ferroelectric DWs with a low voltage, low or high resistance states could be created to realize 0 or 1 data bits for memory applications18,19,20,21,22,23,25. For example, a prototype nonvolatile DW memory unit was demonstrated based on reconfigurable charged DWs (CDWs)19,20,21,23, and the readout current of DWs hinged on the conformational changes of the DWs driven by an electric field between two in-plane terminal electrodes. More intriguingly, ferroelectric DW memory was reported based on a high-density CDW array with a controllable readout current18.

Thus, CDWs can be used as dynamic functional entities, and their large local electric conduction also offers intriguing possibilities for potential nanometer-sized logic applications. Analogous to magnetic racetrack memory or DW logic in nanomagnetic, a ferroelectric DW diode and a field-effect transistor have recently been proposed. The former one is based on the unidirectional motion of all DWs in a terraced KTiOPO4 crystal lamella;26 the latter one is designed through erasing and rewriting of CDWs between the drain, gate, and source electrodes on a LiNbO3 single crystal25. However, unlike magnetic DW logic in nanowires, the realization of ferroelectric DW logic is still a great challenge. The key issue is the implementation and integration of the CDW network with one CDW independently controlled without disturbing the other CDWs. Here, we demonstrate that CDWs within topologically confined vertex domains naturally formed in self-assembled BiFeO3 nano-islands18,27,28 can provide stable networks of local conductive paths for ferroelectric DW logic. Such a ferroelectric CDW network controllable by an electric field with nonvolatile conductance constitutes the building blocks for the proposed reconfigurable DW logic gates and circuits, indicating potential applications for all-electric memory-in-logic devices. By comparing with emerging magnetic DW devices6,7,8,9, the ferroelectric DW logic units exhibit higher integration density due to a much smaller DW width, fast operating speed, and lower energy consumption due to the electric-field-driven features.

Results

Electric control of DW morphology and logic operation analogue

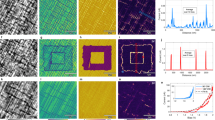

CDWs can naturally form in BiFeO3 nano-islands18,27,28,29,30. By controlling the growth conditions (see “Methods”), we fabricated a BiFeO3 nano-island array with a size of 200–350 nm and an aspect ratio of 1.0–1.5, as shown in Fig. 1a and Fig. S1. Piezoresponse force microscopy (PFM) and conductive-atomic force microscopy (c-AFM) images (Fig. 1b, c and Fig. S2) show cross-shaped CDWs of vertex domains confined in each nano-island. The ferroelectric hysteresis loop (Fig. S3) and the corresponding PFM and c-AFM images (Fig. S4) indicate the reversible control of the quad-domain between center-convergent (Fig. S4a,b) and center-divergent (Fig. S4d,e) polarization states, which accompanies with the head-to-head CDWs with a low conductance state (~pA, Fig. S4c) and a tail-to-tail CWDs with a high conductance state (~nA, Fig. S4f)18. For the head-to-head CDWs in BiFeO3 nano-islands, the screening charges arise from the intrinsic electronic carriers (i.e., electrons liberated from oxygen vacancies) from n-type BiFeO3 nano-islands21,31. While for the tail-to-tail CDWs, the screening charges arise from the p-type LSMO electrode when the quad-domain switched from a downward center-convergent pattern to an upward center-divergent pattern under the applied electric field, where a large number of holes are delivered to the tail-to-tail CDW region to compensate the negative bound charges18.

a Morphology, b in-plane PFM phase, and (c) c-AFM image of vertex domains confined in a rectangular BiFeO3 nano-island array. d Initial cross-shaped CDW network with center-divergent (marked by three-dimensional arrows) vertex domains confined in a rectangular BiFeO3 nano-island. e Disconnection of a CDW branch by a [\(\bar{1}\bar{1}0\)]-oriented (marked by the green arrow) trailing field. f Reconnection of this disrupted CDW branch by a [\(110\)]-oriented (marked by yellow arrow) trailing field. The curves below panels (d–f) are the corresponding current profiles along the dashed lines in (d–f). g, h Schematic of two logic operations of the NOT gate based on the experimental observations in (e, f), where [\(\bar{1}\bar{1}0\)]- and [\(110\)]-oriented electric fields are defined as logic inputs ‘0’ and ‘1’, and the corresponding high and low resistance (HR and LR) states for the disconnected and connected CDW are defined as logic outputs ‘1’ and ‘0’, respectively. i Corresponding symbol (left) and truth table (right) for the NOT logic gate.

To design ferroelectric DW logic based on CDWs, we first explore the dynamic behavior of the cross-shaped CDWs with a high conductance state under a probe-based trailing electric field13,32,33. The details of the control process can be seen in Supplementary Fig. 5. Intriguingly, a targeted CDW of the off-center vertex domains confined in a rectangular nano-island with an aspect ratio deviating from 1 can be independently disconnected and connected again by a trailing electric field without affecting the other CDWs, as shown in Fig. 1d–f. For the initial state in Fig. 1d, the conductive paths of the four CDW branches of the off-center vertex are connected. When an electric field of −3 V is applied on the nanoscale probe (Fig. S5a) with an in-plane downward slow-scanning direction (Fig. S5b), a trailing field along with the [\(\bar{1}\bar{1}0\)] direction is generated during probe scanning, and the targeted CDW branch is disconnected, as shown in Fig. 1e. This disconnected CDW can be reconnected by a trailing field along the [\(110\)] direction (Fig. S5c), as shown in Fig. 1f. The local current and the corresponding resistance state for the connected and disconnected CDW are recorded as shown in the lower panel of Fig. 1d–f. The reproducibility of the connection and disconnection of the CDW has been further confirmed by c-AFM measurements (Fig. S6), and the corresponding low and high resistance state is also recorded as shown in Fig. S7. According to our previous results on the reversible control of the CDW resistance states on the vertex domains of nano-islands18, the repeatable on-and-off switching for CDW network could be no less than 102 cycles. Moreover, time- and temperature-dependent c-AFM measurements, as shown in Figs. S8 and S9, respectively, also illustrate the stability of the modulated CDW network. Such robust control characteristics of the cross-shaped CDWs of the off-center vertex confined in the rectangular nano-island allow reversible control of the ‘on’ and ‘off’ states of one CDW without interfering with the other CDWs. Notably, the CDWs in the square nano-island with an aspect ratio of ~1.0 show negligible variation, e.g., the four CDWs remain after applying the in-plane trailing field as shown in Fig. S10. This stability may arise from the topological protection of the square nano-island18,30,34.

Taking advantage of the reversible modulation of the local conductance states of the CDWs by a trailing field along with the [\(\bar{1}\bar{1}0\)] or [\(110\)] direction, we propose ferroelectric DW logic, as shown in Fig. 1g–i. The [\(\bar{1}\bar{1}0\)]- and [\(110\)]-oriented trailing fields are used to represent the input Boolean logic values ‘0’ and ‘1’, respectively, and the low and high conductance states between the two selected terminals of the cross-shaped CDWs represent the output Boolean logic values ‘1’ and ‘0’, respectively. Here, the transistors are required to control which unit works and which does not, as shown in Fig. 1g, h. Thus, the switching between disconnected (Fig. 1e and g) and connected (Fig. 1f and h) CDWs by an electric field along with the [\(\bar{1}\bar{1}0\)]- and [\(110\)]-orientations, respectively, is analogous to a ‘NOT’ gate, as illustrated by the schematic and truth table in Fig. 1i.

Mechanism of connection and disconnection of ferroelectric DW

To understand the on-and-off switching of the CDW, we performed phase-field simulations to investigate the evolution of the CDW configuration in a rectangular nano-island under an in-plane electric field (see Fig. 2a–c and Supplementary Movies 1, 2). Considering metals may be used as contacts in each of the proposed logic units, different screening charge densities were added to simulate the domain structures in the nano-island, as shown in Fig. S11. As seen, the four-fold quad-domains remain either for the partially compensated state or for the fully compensated state. In Fig. 2, 156 μC/cm2 charges were added to 45° edges of the nano-island, which means the in-plane polarization induced bound charges have been fully compensated35. The initial vertex state of the nano-island (178 × 138 nm2) shows center-divergent quad-domains with a cross-shaped CDW configuration (Fig. 2a). When an in-plane [\(\bar{1}\bar{1}0\)]-oriented electric field is applied in the area enclosed by a blue box in Fig. 2a, the pink area of the quad-domain with an in-plane component of [\(\bar{1}\bar{1}0\)]-oriented polarization grows, but the gray area of the quad-domain with an in-plane component of [\(\bar{1}10\)]-oriented polarization shrinks. This domain evolution is accompanied by DW bending (Fig. 2b), which drives the local DW to change from a CDW (Fig. 2d) to a neutral DW (Fig. 2e), as demonstrated by the transformation between cross-shaped CDWs and interrupted DWs in the bound charge density map of Fig. 2g and h. The detailed definitions of the CDWs and neutral DWs can be seen in the inserts of Fig. 2d, e, and Supplementary Text. Due to the abrupt change in the bound charge density from a CDW to a neutral DW, as shown in the area enclosed by the blue box in Fig. 2g, h, the conductance is expected to dramatically decrease, which is consistent with the disconnected CDW in Fig. 1e. Intriguingly, if a [\(110\)]-oriented electric field is applied in the area enclosed by the blue box in Fig. 2b, the disrupted CDW can be reoriented as shown in Fig. 2c, and transforms into a CDW, as demonstrated in Fig. 2f. The recovered high density of the bound charges for the CDW in Fig. 2i explains the reconnected CDWs in Fig. 1f. The corresponding intermediate domain images and the dynamic evolution for the CDWs from Fig. 2a to b, and Fig. 2b to c can also be seen in Supplementary Fig. 12 and Supplementary Movies 1 and 2, respectively. Additionally, we also performed phase-field simulations to investigate the reversible control of one CDW by the alternative [\(\bar{1}\bar{1}0\)]- and [\(110\)]-oriented electric field (Fig. S13), which is consistent with the experimental observation in Fig. 1d–f and Fig. S6.

a Polar vector map for a 178 × 138 nm2 nano-island with cross-shaped CDWs. b, c Polar vector maps for the rectangular nano-island after a [\(\bar{1}\bar{1}0\)]- or [\(110\)]-oriented electric field is applied in the area enclosed by the blue dotted box in (a). d–f Magnified polar vector maps for the area highlighted by the blue dotted boxes in (a, b, c), which show that the local DW is reversibly modulated between a CDW and a neutral DW by the local electric field. g–i Corresponding charge density maps for (a, b, c). The connected CDWs in (g) and (i) and disconnected CDWs in (h) indicate a high conductance for the CDW and a low conductance for the neutral DW, respectively.

The creation and annihilation of one CDW are related to the variation of the bound charge density during the polarization re-distribution controlled by the external electric field. For the initial state in Fig. 2a, the orientation of the DW marked by the dashed box aligns along \([1\bar{1}0]\)-crystalline orientation. In such cases, there are a large number of negative bound charges accumulated at the DW region (marked by ⊖ the symbol in Fig. 2d), which indicates the nano-island with an initial CDW configuration with a high conductance state (Fig. 2g). After the application of [\(\bar{1}\bar{1}0\)]-oriented electric field, the DW was bent nearly parallel to [\(010\)]-orientation (Fig. 2b). In this case, the polarization vector rotated continuously across the DW region, resulting in a head-to-tail neutral DW (marked by ⊕ and ⊖ symbols in Fig. 2e), i.e., this segment changes from a CDW to a neutral DW (this segment CDW being annihilated). After applying a reversed electric field ([\(110\)]-orientation), the DW was bent nearly to [\(\bar{1}\bar{1}0\)]-orientation (Fig. 2c), where a great number of negative charges (marked by ⊖ symbol in Fig. 2f) accumulated at the DW region once again, resulting in a reversal change of this segment from a neutral DW to a CDW (this segment CDW being re-created, see Fig. 2i).

Design of NOR and NAND logic gates

Based on such robust control characteristics of the cross-shaped CDWs of the off-center vertex domains, more versatile logic gates (e.g., NOR and NAND) can be designed by connecting two rectangular nano-islands in parallel (Fig. 3) or series (Fig. S14). With two nano-islands combined in parallel, as shown in Fig. 3a, the electric fields (E1 and E2) used for control of the CDWs form the two logic inputs, and the conductance state, determined by the parallel resistance of the CDWs confined between the two selected terminals (green nodes), represents the logic output. To illustrate the functionality of the NOR gate, four different logic input configurations of ‘11’, ‘10’, ‘01’, and ‘00’ are illustrated in Fig. 3a–d, where the output conductance state is shown as ‘1’ (high resistance, HR) only when the investigated CDWs of the in-parallel nano-islands are both disconnected; otherwise, it is shown as ‘0’ (low resistance, LR). The relationship between the logic inputs and outputs is summarized in Fig. 3e, which corresponds to the required logic operations for a NOR gate. To further illustrate the working principle of the proposed NOR gate with combined structures, a schematic of the crossbar structure is shown in Fig. S15. The input electric field for the upper panel nano-island is implemented by Word line 1 (WL1) and WL2, and that for the lower panel nano-island is implemented by WL3 and WL4, and the polarity of the electric field is controlled by the switching of the external circuit. The output resistance state is readout by Bit line 1 (BL1) and BL2. With two nano-islands connected in series, a NAND gate is implemented, as shown in Fig. S14. In this case, the output conductance state is shown as ‘0’ (LR) only when the investigated CDWs are both connected; otherwise, it is shown as ‘1’ (HR). Furthermore, the NAND gate can also be implemented when a third nano-island serves as a Bias, as shown in Fig. S16.

Design of OR, AND, XOR, and XNOR logic gates

According to the ‘NOT’ logic gate illustrated in Fig. 1d–f, it is challenging to implement ‘1’ and ‘0’ logic outputs when the logic inputs are ‘11’ and ‘00’, respectively. While these logic operations are the essential ingredients for other basic logic gates, such as ‘OR’, ‘AND’, ‘XOR’, and ‘XNOR’. Thus, more versatile CDWs are needed to be explored, where the connection of one CDW and disconnection of another CDW are required concurrently when a unidirectional trailing field along [\(\bar{1}\bar{1}0\)] or [\(110\)]-orientation is applied on one nano-island. Accordingly, we explore the modulation of CDWs in a nano-island with the size of 260 × 208 nm2 and AR of 1.25) as shown in Fig. 4a–c, where the initial four quad-domains show different symmetry compared with that of the above discussed four quad-domains. As can be seen in Fig. 4a, the c-AFM image shows ~20 nA conductance at the CDW locations when the polarizations are upward and center-divergent. The modulated CDWs by in-plane trailing field are shown in Fig. 4b, c. When the in-plane trailing field is along [\(\bar{1}\bar{1}0\)] direction, we observe that two-quarters of the DWs at the lower/upper panel are disconnected/connected (Fig. 4b), while what happens for the two-quarters of the DWs at the upper/lower panel when the in-plane trailing field is along [\(110\)] direction (Fig. 4c). Thus, the high and low conductance states can be simultaneously implemented between \({A}^{{\prime} }\)/\({B}^{{\prime} }\) node and \({C}^{{\prime} }\)/\({D}^{{\prime} }\) node of the CDW network in Fig. 4b, as well as \({C}^{{\prime} }\)/\({D}^{{\prime} }\) node and \({A}^{{\prime} }\)/\({B}^{{\prime} }\) node in Fig. 4c, respectively. Taking advantage of such CDWs controlled by in-plane downward and upward trailing fields in Fig. 4b, c, we design ‘OR’ and ‘AND’ logic gates by series-connected and parallel-connected two nano-islands with changeable DW networks as discussed above respectively, as shown in Fig. 4d–h and Fig. S17. In addition, other logic gates such as ‘XOR’ and ‘XNOR’ are also designed as shown in Figs. S18 and S19, respectively.

a–c CDW networks at the initial state and controlled by an in-plane trailing field in a BiFeO3 nano-island with an AR of 1.25. The connection/disconnection of \({A}^{{\prime} }\)/\({B}^{{\prime} }\) node and disconnection/connection of \({C}^{{\prime} }\)/\({D}^{{\prime} }\) node is implemented concurrently in one nano-island by applying an in-plane field along [\(\bar{1}\bar{1}0\)] (b) or [\(110\)] direction (c). d–g c-AFM images and corresponding logic circuit diagrams of two series-connected nano-islands with the sequence of logic operations for inputs of ‘11’, ‘10’, ‘01’, and ‘00’. h Truth table for OR logic gate respectively. E1 and E2 are the applied in-plane trailing fields for the two nano-islands. R represents the resistance of the DW between the output electrodes.

Digital signal readout and transmission by ferroelectric DW logic circuits

The demonstrations of the above logic gates make the concept of ferroelectric DW logic viable since any Boolean function can be implemented by combining these basic gates. Furthermore, signal readout and transmission, as schematically shown in the first column of Fig. 5, are also proposed based on an electric-field-controllable ferroelectric CDW network. For comparison, complementary metal-oxide semiconductor (CMOS) and ferromagnetic DW logic circuits8 are also highlighted, as shown in the second and third columns of Fig. 5, respectively. For the signal readout, a low voltage and a high voltage can be read out directly at two ends (marked by black points) of a connected (the first panel of the fourth column in Fig. 5) and disconnected (the second panel of the fourth column in Fig. 5) CDW, and the readout signals can be easily switched between each other by an electric field (indicated by the bidirectional arrow in Fig. 5). The third panel of the fourth column of Fig. 5 shows a fan-out circuit, where an input signal can be separated into two output signals of A and B. In this way, one might be able to integrate all-electric logic gates and circuits into the nano-island array and regulate the function of each specific logic unit as needed.

Schematic illustration of the ferroelectric DW logic circuits for the readout signal of low and high voltages and the fan-out function. The bidirectional arrow indicates that the readout signals of low and high voltages can be transformed into each other by electric-field-induced connection and disconnection of a CDW. The schematics for the CMOS circuit and magnetic DW logic circuit, redrawn from ref. 8 are also illustrated for comparison. E represents the applied in-plane electric field.

Discussion

As discussed at the beginning, in comparison with emerging designs of racetrack memory and DW logic based on moving magnetic DW6,7,8,9, the ferroelectric DW logic units exhibit higher integration density (Fig. S20) due to much smaller DW width and lower energy consumption due to electric-field-driven features. More comparison in the Supplementary Table 1 demonstrates some benefits of the ferroelectric DW logic circuit for device applications, such as low energy consumption, fast operation speed, and high integration density. For example, the operating energy for one bit estimated for the ferroelectric DW logic units is in 10 aJ order of magnitude, which is comparable to the emerging energy-efficient magnetoelectric spin-orbit logic but much lower than other emerging magnetic and existing CMOS technologies36. Finally, it should be noted that the proposed ferroelectric DW logic units are preliminary designs and there are several challenges. For example, the endurance of the CDW network under electric field-driven repeated on-and-off switching (Figs. 1d–f) and operation at higher temperatures (Fig. S9) remain to be improved. One possible way to address this issue in the future is to design the geometry (size and AR) of the nano-islands30,37, such that the shape and thickness of the CDW might be accurately confined by the symmetry of the nano-islands. Another big challenge is the logic cascading of the single logic gates, which may be implemented by appropriate circuit design and connection, e.g., the voltage corresponding to the resistance state of the DW can be set as output, and then the output voltage can be used as the input of the next logic gate, to achieve cascade.

In summary, we demonstrate electric-field controlled stable and repeatable on-and-off switching of conductive domain walls within topologically confined vertex domains naturally formed in self-assembled ferroelectric nano-islands, which is accompanied by the transformations between charged and neutral domain walls via electric-field controlled domain-wall reconfiguration. By analogous to logic processing, we also propose programmable logic gates and circuits based on reconfigurable conductive domain walls. This ferroelectric memory-in-logic architecture proposed based on the flexible control of conducting domain-wall network might allow for designing programmable all-electric logic with low energy consumption.

Methods

Preparation of ferroelectric nano-island array with CDWs

BiFeO3 thin films were prepared by pulsed laser deposition method on LaAlO3 (001) single-crystal substrates, where a very thin (2 nm) (La,Sr)MnO3(LSMO) buffer layer was pre-grown to construct the required electrostatic and elastic boundary conditions for the nucleation of self-assembled BiFeO3 nano-islands. During the thin-film preparation, the growth temperature was maintained in the range of 600–750 °C under the oxygen pressure of 0.2 mbar. The growth details for BiFeO3 nano-island array are similar to our previous work27.

PFM measurements for ferroelectric-domain configurations

The polar vectors of the three-dimensional BiFeO3 nano-islands were investigated by the combination of vertical and lateral PFM phase images using an Infinity Asylum Research AFM and a Bruker AFM. During the measurement, a commercial Pt/Ir-coated tip with a tip radius of 20 nm, a force constant of 2.8 N/m, and a resonant frequency of 75 kHz was used as a movable top electrode, where the bottom electrode (LSMO layer) was ground. The PFM signal was collected at the contact resonance frequency with an a.c. tip bias of 1 Vpp, and the scanning velocity of the cantilever is 0.5 μm/s.

c-AFM measurements for conducting DW network

The conductance of the BiFeO3 nano-islands was characterized by c-AFM, which is also based on an Infinity Asylum Research AFM and a Bruker AFM. In the c-AFM model, a commercial Pt/Ir-coated tip was used. During the conductance measurement, the tip was ground and the voltage bias was applied to the LSMO bottom electrode. The bias voltage applied to the LSMO bottom electrode is ~1.5 V.

Phase-field simulations

Phase-field simulations were carried out using the time-dependent Ginzburg-Landau model for the investigation of domain evolution and DW network in BiFeO3 nano-islands. Ferroelectric polarization evolution is described by the polarization vector \({{{{{{\bf{P}}}}}}}_{i}\)(\({P}_{x}\), \({P}_{y}\), \({P}_{z}\)), which is the order parameter to describe the domain structure. The model describes the temporal evolution of domain structure, which can be numerically solved by the time-dependent Landau-Ginzburg (TDGL) equation,

where t, L, and Fp are simulation time, kinetic coefficient (related to DW mobility), and total free energy respectively, whereas:

where fbulk, fgrad, felas, and felec are bulk free energy density38, gradient energy density, elastic energy density, and electric energy density39, respectively. The bulk free energy density fbulk is a sixth-order polynomial,

where \({\alpha }_{1},{\alpha }_{11},{\alpha }_{12},{\alpha }_{111},{\alpha }_{112}\) and \({\alpha }_{123}\) are dielectric stiffness and high order stiffness. Among them, only \({\alpha }_{1}\) depends on the temperature, such that \({\alpha }_{1}\) = (T−T0)/(2ε0C0), T is temperature, T0 is Curie temperature, ε0 = 8.85 × 10−12 F/m is dielectric permittivity of vacuum, C0 is the Curie constant.

The gradient energy density is described in terms of polarization gradients. For simplicity, the gradient energy is taken to be isotropic, given as:

where the \({g}_{{ijkl}}\) is gradient energy coefficient and \({{{{{{\bf{P}}}}}}}_{i.j}=\partial {P}_{i}/\partial {x}_{j}\)40\(.\) The elastic energy can be written as,

where the \({c}_{{ijkl}}\) is elastic stiffness tensor, \({e}_{{ij}}\) is elastic strain, \({\varepsilon }_{{ij}}\) is total elastic strain, \({\varepsilon }_{{ij}}^{0}\) is the stress-free strain given as \({\varepsilon }_{{ij}}^{0}={Q}_{{ijkl}}{P}_{k}{P}_{l}\), where \({Q}_{{ijkl}}\) represents the electrostrictive coefficient41. The electrostatic energy, \({f}_{{{\mbox{elec}}}}\), is given by,

In the present simulations, an open circuit boundary condition with fully compensated edge charges (156 μC/cm2) on edge tilts and charge-free on the substrate and top surface was used as an electrostatic boundary condition, and a strain-free mechanical boundary condition was used at the working temperature of 300 K. The nano-island was constructed with a size of 178 nm × 138 nm at the base and 7 nm at the island height, and the edge tilt was taken as 45° for the simulations. The value of coefficients used for the current work is listed in Supplementary Table 242. The parameters of permittivity and Curie constant (C0) used in the phase-field simulations are 50 and 1.2166 × 105 K, respectively.

Reporting summary

Further information on research design is available in the Nature Research Reporting Summary linked to this article.

Data availability

The authors declare that the data supporting the findings of this study are available within the paper and its Supplementary Information Files.

References

Catalan, G., Seidel, J., Ramesh, R. & Scott, J. F. Domain wall nanoelectronics. Rev. Mod. Phys. 84, 119–156 (2012).

Meier, D. & Selbach, S. M. Ferroelectric domain walls for nanotechnology. Nat. Rev. Mater. 7, 157–173 (2022).

Yang, S.-H., Naaman, R., Paltiel, Y. & Parkin, S. S. P. Chiral spintronics. Nat. Rev. Phys. 3, 328–343 (2021).

Raymenants, E. et al. Nanoscale domain wall devices with magnetic tunnel junction read and write. Nat. Electron. 4, 392–398 (2021).

Li, R. et al. A spin–orbit torque device for sensing three-dimensional magnetic fields. Nat. Electron. 4, 179–184 (2021).

Parkin, S. S. P., Hayashi, M. & Thomas, L. Magnetic domain-wall racetrack memory. Science 320, 190–194 (2008).

Thomas, L., Moriya, R., Rettner, C. & Parkin, S. S. P. Dynamics of magnetic domain walls under their own inertia. Science 330, 1810–1813 (2010).

Allwood, D. A. et al. Magnetic domain-wall logic. Science 309, 1688–1692 (2005).

Luo, Z. et al. Current-driven magnetic domain-wall logic. Nature 579, 214–218 (2020).

Sluka,T., Bednyakov, P., Yudin, P., Crassous, A. & Tagantsev, A. in Topological Structures in Ferroic Materials: Domain Walls, Vortices and Skyrmions (ed. Seidel, J.) 103–138 (Springer International Publishing, 2016).

Seidel, J. Domain walls in motion. Nat. Nanotechnol. 10, 109 (2015).

Seidel, J. et al. Conduction at domain walls in oxide multiferroics. Nat. Mater. 8, 229–234 (2009).

Crassous, A., Sluka, T., Tagantsev, A. K. & Setter, N. Polarization charge as a reconfigurable quasi-dopant in ferroelectric thin films. Nat. Nanotechnol. 10, 614–618 (2015).

McGilly, L. J., Yudin, P., Feigl, L., Tagantsev, A. K. & Setter, N. Controlling domain wall motion in ferroelectric thin films. Nat. Nanotechnol. 10, 145–150 (2015).

Rojac, T. et al. Domain-wall conduction in ferroelectric BiFeO3 controlled by accumulation of charged defects. Nat. Mater. 16, 322–327 (2017).

Lu, H. et al. Electrical tunability of domain wall conductivity in LiNbO3 thin films. Adv. Mater. 31, 1902890 (2019).

Zhang, Y. et al. Intrinsic conductance of domain walls in BiFeO3. Adv. Mater. 31, 1902099 (2019).

Ma, J. et al. Controllable conductive readout in self-assembled, topologically confined ferroelectric domain walls. Nat. Nanotechnol. 13, 947–952 (2018).

Jiang, J. et al. Temporary formation of highly conducting domain walls for non-destructive read-out of ferroelectric domain-wall resistance switching memories. Nat. Mater. 17, 49–56 (2018).

Jiang, A. Q. et al. Ferroelectric domain wall memory with embedded selector realized in LiNbO3 single crystals integrated on Si wafers. Nat. Mater. 19, 1188–1194 (2020).

Sharma, P. et al. Nonvolatile ferroelectric domain wall memory. Sci. Adv. 3, e1700512 (2017).

McConville, J. P. V. et al. Ferroelectric domain wall memristor. Adv. Funct. Mater. 30, 2000109 (2020).

Sharma, P. et al. Conformational domain wall switch. Adv. Funct. Mater. 29, 1807523 (2019).

Liu, L. et al. Giant domain wall conductivity in self-assembled BiFeO3 nanocrystals. Adv. Funct. Mater. 31, 2005876 (2020).

Chai, X. et al. Nonvolatile ferroelectric field-effect transistors. Nat. Commun. 11, 2811 (2020).

Whyte, J. R. & Gregg, J. M. A diode for ferroelectric domain-wall motion. Nat. Commun. 6, 7361 (2015).

Ma, J. et al. Self-assembly growth of a multiferroic topological nanoisland array. Nanoscale 11, 20514–20521 (2019).

Kim, K. E. et al. Configurable topological textures in strain graded ferroelectric nanoplates. Nat. Commun. 9, 403 (2018).

Li, Z. et al. High-density array of ferroelectric nanodots with robust and reversibly switchable topological domain states. Sci. Adv. 3, e1700919 (2017).

Ma, J. et al. Geometry confined polar vertex domains in self-assembled BiFeO3 nano-islands. Mater. Res. Lett. 7, 399–404 (2019).

Wu, W., Horibe, Y., Lee, N., Cheong, S.-W. & Guest, J. R. Conduction of topologically protected charged ferroelectric domain walls. Phys. Rev. Lett. 108, 077203 (2012).

Vasudevan, R. K. et al. Deterministic arbitrary switching of polarization in a ferroelectric thin film. Nat. Commun. 5, 4971 (2014).

Wang, C. et al. Ferroelastic switching in a layered-perovskite thin film. Nat. Commun. 7, 10636 (2016).

Chen, M. et al. Stabilization of ferroelastic charged domain walls in self-assembled BiFeO3 nanoislands. J. Appl. Phys. 128, 124103 (2020).

Chu, Y.-H., Martin, L. W., Holcomb, M. B. & Ramesh, R. Controlling magnetism with multiferroics. Mater. Today 10, 16–23 (2007).

Manipatruni, S. et al. Scalable energy-efficient magnetoelectric spin–orbit logic. Nature 565, 35–42 (2018).

Chen, M. et al. Robust polarization switching in self-assembled BiFeO3 nanoislands with quad-domain structures. Acta Materialia 175, 324–330 (2019).

Li, Y. L., Hu, S. Y., Liu, Z. K. & Chen, L. Q. Phase-field model of domain structures in ferroelectric thin films. Appl. Phys. Lett. 78, 3878–3880 (2001).

Li, Y. L., Hu, S. Y., Liu, Z. K. & Chen, L. Q. Effect of electrical boundary conditions on ferroelectric domain structures in thin films. Appl. Phys. Lett. 81, 427–429 (2002).

Pertsev, N. A., Kukhar, V. G., Kohlstedt, H. & Waser, R. Phase diagrams and physical properties of single-domain epitaxial PbZr(1-x)TixO3 thin films. Phys. Rev. B 67, 054107 (2003).

Haun, M. J., Furman, E., Jang, S. J., Mckinstry, H. A. & Cross, L. E. Thermodynamic theory of PbTiO3. J. Appl. Phys. 62, 3331–3338 (1987).

Hsieh, Y.-H. et al. Permanent ferroelectric retention of BiFeO3 mesocrystal. Nat. Commun. 7, 13199 (2016).

Acknowledgements

We thank Dr. X.M. Shi for his discussion on logic operations. We are also grateful to Analysis & Testing Center at BIT. This work was supported by the Basic Science Center Program of the National Natural Science Foundation of China (NSFC) grant 51788104; NSFC grant 12004036, 51922055, 51972028, 52002204, and 11974052; and the National Basic Research Program of China grant 2019YFA0307900.

Author information

Authors and Affiliations

Contributions

C.-W.N. conceived the project. J.W., Jing M., H.H., and D.Y. performed the logic study. Ji M. and M.C. fabricated the thin films. J.W., Ji M., Y.F., H.Y., and Y.W. performed PFM and c-AFM measurements. H.J. and D.L. performed the phase-field simulations under the supervision of H.H. and L.-Q.C. J.W., H.H., and Jing M. wrote the draft of the manuscript. J.Z. and Y.L. discussed the results. All authors discussed the results and edited the manuscript.

Corresponding authors

Ethics declarations

Competing interests

The authors declare no competing interests.

Peer review

Peer review information

Nature Communications thanks Cheol Seong Hwang and the other anonymous reviewer(s) for their contribution to the peer review of this work.

Additional information

Publisher’s note Springer Nature remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

Rights and permissions

Open Access This article is licensed under a Creative Commons Attribution 4.0 International License, which permits use, sharing, adaptation, distribution and reproduction in any medium or format, as long as you give appropriate credit to the original author(s) and the source, provide a link to the Creative Commons license, and indicate if changes were made. The images or other third party material in this article are included in the article’s Creative Commons license, unless indicated otherwise in a credit line to the material. If material is not included in the article’s Creative Commons license and your intended use is not permitted by statutory regulation or exceeds the permitted use, you will need to obtain permission directly from the copyright holder. To view a copy of this license, visit http://creativecommons.org/licenses/by/4.0/.

About this article

Cite this article

Wang, J., Ma, J., Huang, H. et al. Ferroelectric domain-wall logic units. Nat Commun 13, 3255 (2022). https://doi.org/10.1038/s41467-022-30983-4

Received:

Accepted:

Published:

DOI: https://doi.org/10.1038/s41467-022-30983-4

This article is cited by

-

A review on different theoretical models of electrocaloric effect for refrigeration

Frontiers in Energy (2023)

Comments

By submitting a comment you agree to abide by our Terms and Community Guidelines. If you find something abusive or that does not comply with our terms or guidelines please flag it as inappropriate.