Abstract

Inorganic amorphous oxide semiconductor (AOS) materials such as amorphous InGaZnO (a-IGZO) possess mechanical flexibility and outstanding electrical properties, and have generated great interest for use in flexible and transparent electronic devices. In the past, however, AOS devices required higher activation energies, and hence higher processing temperatures, than organic ones to neutralize defects. It is well known that one-dimensional nanowires tend to have better carrier mobility and mechanical strength along with fewer defects than the corresponding two-dimensional films, but until now it has been difficult, costly, and impractical to fabricate such nanowires in proper alignments by either “bottom-up” growth techniques or by “top-down” e-beam lithography. Here we show a top-down, cost-effective, and scalable approach for the fabrication of parallel, laterally oriented AOS nanoribbons based on lift-off and nano-imprinting. High mobility (132 cm2/Vs), electrical stability, and transparency are obtained in a-IGZO nanoribbons, compared to the planar films of the same a-IGZO semiconductor.

Similar content being viewed by others

Introduction

Flexible and transparent electronics can be designed to maintain close contact with curved and moving surfaces, and can be inconspicuously mounted on a wide variety of substrates. Hence, many types of flexible/transparent electronic devices, including sensors1,2,3,4, thermoelectric devices5, 6, and displays7, 8, could be incorporated into everyday life in unobtrusive configurations9. Interest in these electronic devices has been growing rapidly over the past few years10, 11. So far, most of the technical issues impeding their fabrication are related to the need for low processing temperatures12. This is because most flexible materials, in particular substrates such as a plastic foil13 or paper14 sheet, are vulnerable to the high temperatures that are generally necessary to achieve satisfactory semiconductor property. The desirability of low processing temperatures has motivated the use of organic semiconductors, typically deposited and annealed below 150 °C. While their electrical performance is competitive to that of amorphous silicon (a-Si) and their mechanical flexibility can be high15, their limited carrier mobility (~1–10 cm2/Vs) may be insufficient for high-speed or low-power applications, and their chemical stability, while improving, is less than that of typical inorganic materials.

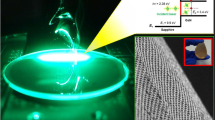

Meanwhile, higher mobility (>10 cm2/Vs) has been obtained in inorganic amorphous oxide semiconductors (AOSs) such as amorphous indium gallium zinc oxide (a-IGZO)16. However, for AOSs based electronics, a trade-off exists between post-annealing process and electrical performance because of an inherent large number of defects and loose amorphous networks inside AOS films17. Thus, many attempts have been made, by optimizing device structure or material processing, to realize higher mobility with lower-annealing-temperature processes (Fig. 1)18,19,20,21,22,23. In addition, the intrinsic mechanical flexibility of AOSs macroscopic films cannot be still competitive to organic semiconductors15.

Recent progress in AOS-based thin-film transistors (TFTs). Post-annealing temperature versus mobility and Subthreshold swing (SS) achieved in recent studies into a-IGZO TFTs. A summary of detailed device specifications and substrates is shown in the table. The nanoribbon material shows the optimal combination of low temperature, high mobility, and low subthreshold slope.

One-dimensional (1-D) nanowire structures based on both organic and inorganic semiconductors have displayed greater mechanical flexibility and electrical performance than do the corresponding two-dimensional films24,25,26. In this regard, nanoscale size results in a reduction in undesirable defects and dislocations incorporated into the channel. Nanowires made by a bottom-up approach, however, present challenges in assembly and lack of controllability in size for mass production10. In contrast, a top-down (e.g., lithographic) approach allows precise sizing, alignment, and placement, but typical large-area nanoscale patterning by e-beam lithography is highly time-consuming and cost-intensive. Moreover, adequate dry/wet etching systems of AOSs are not yet mature compared to silicon ones, and flexible substrates can be easily damaged by various chemicals or plasma systems.

Herein, we establish a top-down approach to fabricate parallel and laterally oriented nanoribbons (NRs) based on nano-imprinting using a master, low-temperature sputtering and lift-off. As a-proof-of concept, we demonstrated uniform, low-cost, large-scale a-IGZO NR arrays with different sizes without using dry/wet etch-patterning systems on the NR materials. The NRs showed outstanding mobility (132 cm2/Vs) and their arrays showed better optical transmittance than bare glass, even after a low post-annealing processing temperature (85 °C) obtained by microwave annealing. This technology offers a simple method to make NRs of arbitrary inorganic materials that can be deposited by sputtering or vapor deposition.

Results and Discussion

Fabrication of NRs based on T-shape patterns

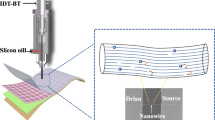

Typically, lift-off in device fabrication is made easier by undercut resist profiles and depositions that can be carried out directionally using evaporation sources (Fig. 2a). Unfortunately, lift-off is much less effective with sputtered films, especially for nanoscale patterning, since the sputtering systems tend to offer relatively good step coverage of undercut profiles owing to their random-angled delivery (Fig. 2b). Nevertheless, the most stable properties of AOSs are currently achieved by sputtering. By conferring a unique figure into the lift-off patterns, referred to as a “nanocavity” (under the T-shaped features of Fig. 2c), we have demonstrated a method for NR fabrication applicable to any sputtered or vapor-deposited material.

Procedures for a-IGZO NRs fabrication by lift-off. (a) Schematics of typical lift-off based on evaporation systems. The undercut area of the resist is not covered by directional deposition of material. (b) Challenges in lift-off of randomly angled sputtered films. The undercut area of the resist is covered by deposited material so solvent cannot react with the resist during the lift-off process. (c) The lift-off procedure based on T-shape pattern. (d–g) Cross sectional diagram and SEM images of lift-off NRs fabrication step. (d) Imprinted grating patterns from master stamp with 400 nm pitch, 70 nm spaces, and 120 nm height; and Ti hard mask formation by tilted depositions. (e) Tail creation on edge of resist by O2 ashing process. (f) a-IGZO deposition of 45 nm by sputtering on the lift-off patterns. (g) performing lift-off process using acetone. (h) Photograph and plan-view SEM images of the produced the same size of NR on PI substrate.

The sequence of the method is as follows: periodic grating patterns of ridges are imprinted in a resist coating silicon, glass, or polyimide (PI) substrates by a master stamp with a 70 nm space and a 400 nm pitch (Fig. 2d). The details regarding the formation of the imprinted grating pattern are depicted in Fig. S1. A 10-nm-thick titanium (Ti) cap is formed on the upper portions of the sidewalls as well as the tops of the resist ridges by tilted deposition at a 70° angle from the horizontal using an e-beam evaporator (Fig. 2d). The lower portion of the sides and the evolving underside of the resist with the Ti cap were uniformly etched using oxygen plasma, while forming the “nanocavity”, while not etching near the Ti-resist top interface (Fig. 2e), with the Ti acting as a hard mask. Sputtered atoms from IGZO target are deposited between the Ti caps (Fig. 2f) with the spaces between the caps defining the regions where NRs will remain. The caps and remaining resist ridges are lifted off using acetone under ultrasonication that can penetrate into the patterns very uniformly, removing all of the T-features but leaving NRs behind. Consequently, the NRs are very homogeneous over large areas (Fig. 2g) with a trapezoidal shape owing to some deposited atoms reaching areas under the caps during the initial stage of sputtering. Single NR width (W s )/thickness (T), and spacing (S) between adjacent NRs were estimated by SEM as 83/45 and 320 nm (Fig. 2g). W s /T/S can be controlled by modifying the grating patterns of the master stamp. A different larger NR (W s /T/S: 130/45/166 nm) array was made as shown in Fig. S2. Also, T-feature-patterned substrates allow any kind of sputtered materials to be lifted off uniformly and this technology is also applicable to large-area PI sheets by employing the same sequence (Fig. 2h).

Simulation of NR and planar TFTs

We estimated cross-sectional electron distribution of a-IGZO TFTs in planar (Fig. 3a) and NR channels (Fig. 3b) with the same thickness using technology computer-aided design (TCAD) simulation. Each simulated NR TFT had 10 NRs. Higher cross-sectional electron density was obtained from NRs because of stronger electric fields confined in smaller structures and fringing field effects on the edges of the NRs27. We compared the electron density of NRs of different sizes in Figs 3c and S3. Electron concentrations of NRs, represented by the red color, become higher as they shrink in size. The transfer curves show higher drain current (I D ) in larger NRs, but higher I D density in smaller NRs.

TCAD simulation of cross-sectional distribution of electron density in (a) planar and (b) NR channel with the same thickness viewed from the (source or drain) electrode. (c) Comparison in electron density distribution of the single NR in different sizes. Electron concentration increases as NRs shrink, as shown by the red color moving up.

Electrical performance of NR and planar TFTs

The electrical performance of the NRs was evaluated on Si/SiO2 substrates to avoid any non-ideal effects from more heterogeneous or polar dielectrics. Two different NR arrays were prepared: 67 NRs with each NR having W s /T/S: 130/45/166 nm (Type I) and 50 NRs with each NR having W s /T/S: 83/45/320 nm (Type II) within the device width (W D ) of 20 µm. To further identify size-dependent transport properties of NRs, we etched initial NRs with tetramethyl ammonium hydroxide (TMAH) under precisely controlled conditions. Simultaneously, 45-nm-thick films were etched under the same wet etching condition as reference. TMAH etching reduced both W s and T of the single NR at etching rates of 21.2 nm/min and 8.3 nm/min, respectively, and the thickness of planar films was etched at a rate of 6.5 nm/min. Total active width (W T ) excluding space between NRs was estimated by multiplying each W s by the number of NR within the 20 μm W D as shown in Fig. 4. In the etching process of planar films, total W T remained relatively unchanged while film thickness was reduced.

W T and thickness vs TMAH etching time of each substrate. The device width and length are 20 and 10 μm, respectively. Length is fixed to 10 um for all TFTs. 67 NRs (W s /T: 130/45 nm) and 50 NRs (W s /T: 83/45 nm) are made within the device width. W T was calculated by multiplying W s by the number of NR for each substrate.

Transfer curves for planar and NR TFTs under different TMAH etching times are shown in Fig. 5a,b,c. Cross-sectional I D density is approximated by dividing W D by cross-sectional area (W T × T) (Fig. 5d,e,f). After etching, I D levels for all TFTs are reduced because thinner or smaller sizes of channel lead to higher resistance. Cross-sectional I D density, however, shows a distinguishable behavior between NRs and planar films. NR TFTs reveal higher I D density with decreasing widths of NRs.

Representative transfer curves of (a) planar and (b,c) NR TFTs on Si substrate with respect to TMAH etching time. The Y-axis on the right side of each transfer curve shows the linear plot. I D levels decreased with additional etching. Cross-sectional current density of (d) planar and (e,f) NR TFTs. Cross-sectional I D density was estimated by dividing I D by active area (W T × T) of each channel. NR TFTs showed increased current density as NRs shrank, but the planar film TFTs did not.

For further analysis, maximum I D (Fig. 6a) and I D density (Fig. 6b) at 40 V gate voltage (V g ) were collected from each transfer curve. I D levels of planar TFTs are significantly dependent on etching time but the NR TFTs are relatively independent. In contrast, I D density increases greatly as the size of NRs shrinks (Fig. 6b), which corresponds to the simulation result in Fig. S4. At this point, the reduced thickness in the planar film simply increased channel resistance but the decreased size of NR yielded more I D from the fringing effect induced by much stronger electric fields on smaller NRs. Meanwhile, we could expect I D levels from the NR TFTs to increase for denser NRs within the W D (Fig. 6c) through the comparison of I D levels in similar size NRs made by different master stamps. Also, we calculated critical occupancy of NRs based on the experimental results in Fig. 6a, where the same I D levels as those of the planar TFTs were observed for the NR TFTs (Fig. 6d). The critical occupancy decreased in the smaller NRs from their higher I D density (orange). Denser NRs over critical occupancy can make much higher I D levels than the planar TFTs (gray).

Maximum I D (a) and I D density (b) with respect to TMAH etching time. Maximum I D was collected at V g of 40 V and V D of 10 V from each transfer curve. Occupancy, y-axis on the right side, was calculated by W T /W D . Cross-sectional I D density was estimated by dividing maximum I D by active region (W T × T). (c) Correlation of I D to the number of NRs. I D levels from similar size NRs were normalized by each thickness for comparison. (d) Occupancy of NRs within the W D depending on TMAH etching (blue). Critical occupancy of NRs that is required to obtain the same I D level of as planar TFT is shown in orange. Higher occupancies, shown in gray, will give I D greater than does the planar TFT.

The threshold voltage (V th ) and on/off current ratio distribution are presented in Figs S5a and S5b. V th of all devices shifted slightly to the positive regime after TMAH etching. On/off ratios of NR TFTs are over 107 showing a tendency of slight decrease in on/off ratio after being etched. Effective field-effect mobility (μ FE )was extracted using the following equation28:

where V D is drain voltage (set at 10 V), L is the device length (fixed as 10 μm), and C i is the gate capacitance per unit area. C i value is experimentally obtained by a metal-insulator-semiconductor capacitor of 34.5 nF/cm2 (Supplementary Fig. S6). The maximum figure of dI D /dV G was chosen in each transfer curve. μ FE values of planar TFTs are slightly reduced after being etched with TMAH (Fig. 7). In contrast, μ FE of NR increased up to 132 cm2/Vs as the size of the NRs decreased. While initial NRs made by our proposed method showed uniform electrical properties, μ FE values were more disperse when NRs were made by the wet etching process.

Corresponding to the improvement in mobility, the SS values also improved in a smaller size NR (Fig. 8a): Type II NR array shows 336 mV/dec on average for initial with best (lowest) value of 260 mV/dec and 199 mV/dec on average for TMAH 2 min with the best (lowest) value of 132 mV/dec. The planar TFTs showed a similar range of SS from 406 (initial) to 372 mV/dec (TMAH 2 min). Interface trap density (N t ) between the channel and the gate dielectric was calculated with the following equation29:

where q is the electron charge, k B is the Boltzmann constant, and T is the absolute temperature. The estimated N t values are lower in NRs than in planar films (Fig. 8b). Also, N t is gradually lowered while the size of the NRs shrinks with less interfaces area. Furthermore, electrical stability was evaluated by positive-biased stress (PBS) tests. Electric stability was improved with less interface area; larger NR (W/T: 130/45 nm) arrays and planar type IGZO showed larger V th shift under stress bias of 20 V for 1 hour (Fig. 8c). Both interface traps and the incorporation of bulk defects are highly decreased with reducing the size of NRs.

(a) SS and (b) interface trap density distribution of NR and planar TFTs. (c) The V th shift determined by the PBS stress tests, averaged over at least 10 NRs devices and planar TFTs. The V th shift is equal to the change between the initial value and the value obtained after a constant 20 V has been applied to the back gate electrode for 1 h. (d) Transmittance in the visible wavelength regime of bare glass, a-IGZO film, and NR structure on a glass substrate.

Full transparency is also recognized as a key property for flexible electronics; low loss and low reflection are both extremely desirable. By fabricating NRs and planar films on glass substrates, we were able to compare their optical transmittance, as shown in Fig. 8d; the transmittance values mentioned are relative figures, compared to air. The transmittance of the NRs reached to 92% at 550 nm that is given as greater than that of bare glass and a-IGZO/glass substrate thanks to anti-reflection effects on the surface eliminating stray light. This transmittance of our NR array is comparable to that of low dimensional materials such as grapheme (90%)30, carbon nanotube (92%)31, CuNW (84.4%)32, and AgNW (90.7%)33.

Conclusions

A major concern for flexible electronics is to achieve high levels of device electrical performance at low processing temperatures. In this study, we investigated a promising solution, based on NR geometries. We demonstrated that a-IGZO NRs showed superior electrical performance per unit of active area and optical transparency compared to planar films of the same material, because of the structural advantages from NRs. These a-IGZO NRs are desirable building blocks for flexible electronics in wide ranging areas such as sensors, thermoelectric devices, and displays. Also, our top-down approach in fabricating NRs is widely applicable for AOSs materials based on sputtering depositions. This technology should open the door to further applications of flexible electronics based on inorganic materials.

Methods

Process sequence in fabricating grating pattern by nanoimprint

The silicon master containing grating pattern that is used as mother stamp is fabricated by deep ultraviolet (ASML, PAS5500/700D KRF Scanner, 248 nm) lithography and deep reactive ion etching (RIE, LAM, TCP-9400DFM). One grating pattern of the silicon master has a width of 70 nm, a space 330 nm, a height of 120 nm in a period of 400 nm. Another grating pattern of the silicon master has a width of 150 nm, a space 150 nm, a height of 120 nm in a period of 300 nm. Self-assembled monolayer (SAM, trichlorosilane Sigma-Aldrich, 97%) is coated on the silicon master template. Poly carbonate (PC) film is contacted to the silicon master, and UV resin is filled into the master pattern by roll press force to the mold. PC film mold is replicated from the silicon master by UV (365 nm) curing at an intensity of 1 kW/cm2 for duration of 180 sec. UV light is emitted through the PC film and cures the resist in the process. Accordingly, SAM was coated on PC film mold for better separation between the mold and imprint resin. The replica mold is contacted to each silicon, polyimide, and glass substrate with thermally sensitive resist (Poly(methyl methacrylate (PMAA), mr-I PMAA 35 k). Thermal imprinting is performed at 130 °C in air ambient for 2 hours, and after cooling down to 90 °C, the replica mold is detached from the substrate. The schematic image in the process above is provided in Supplementary Fig. 1.

Fabrication of a-IGZO NRs TFT

A 10-nm-thick Ti cap is formed on the upper portions of the sidewalls as well as the tops of the resist ridges by tilted deposition at a 70° angle from the horizontal using an e-beam evaporator. The lower portion of the sides and the evolving underside of the resist with the Ti cap were uniformly etched using oxygen plasma using oxygen plasma at 300 W for 12 min in ambient Ar (300 ml/min). A 45-nm-thick a-IGZO was deposited by RF magnetron sputter at a power of 100 W and a working pressure of 6 mToor using Ar gas with a flow rate of 30 sccm (cm3/min). T-shape structures are lifted off using acetone under ultrasonication. The length and width of devices defined by photolithography that were 10 μm and 20 μm, respectively, and 50 nanoribbons were included in that width. Post deposition annealing was performed using a microwave annealing system at 1000 W for 10 min in ambient N2. The amorphous phase of our sputtered IGZO was maintained even after furnace annealing of ca. 400 °C30. In this work, the maximum internal temperature of the microwave annealing system, as detected by a thermocouple, was ca. 85 °C. Subsequently, a 10-nm-thick titanium layer and a 50-nm-thick indium tin oxide layer were deposited for the source/drain (S/D) electrode by an e-beam evaporator. S/D electrode needs to be formed in the direction perpendicular to that of NRs for the TFTs to operate (Fig. S7). A 100-nm-thick dielectric of SiO2 was deposited by sputtering for passivation. All electrical transport measurements were performed in air at room temperature using a shielded probe station with triaxial cable and connectors in order to minimize RF noise.

Additional Information

Process sequence in fabricating grating pattern by nanoimprint, SEM image of nanocavity and nanoribbons using a different mother mold, simulations of different size nanoribbons, transfer curve, on-current, threshold voltage, on/off current ratio, and SS distribution of TFTs with nanoribbons and planar channel, capacitance measurement of gate dielectric, and transfer curve made by different direction of NRs.

References

Schwartz, G. et al. Flexible polymer transistors with high pressure sensitivity for application in electronic skin and health monitoring. Nat. Commun. 4, 1859 (2013).

Benight, S. J., Wang, C., Tok, J. B. H. & Bao, Z. Stretchable and self-healing polymers and devices for electronic skin. Prog. Polym. Sci. 38(12), 1961–1977 (2013).

Correa, D. S., Medeiros, E. S., Oliveira, J. E., Paterno, L. G. & Mattoso, L. H. C. Nanostructured Conjugated Polymers in Chemical Sensors: Synthesis, Properties and Applications. J. Nanosci. Nanotechnol. 14(9), 6509–6527 (2014).

Zang, Y. P., Zhang, F., Di, C.-A. & Zhu, D. Advances of flexible pressure sensors toward artificial intelligence and health care applications. Mater. Horiz 2(2), 140–156 (2015).

Poehler, T. O. & Katz, H. E. Prospects for polymer-based thermoelectrics: state of the art and theoretical analysis. Energy Environ. Sci. 5(8), 8110–8115 (2012).

He, M., Qiu, F. & Lin, Z. Q. Towards high-performance polymer-based thermoelectric materials. Energy Environ. Sci. 6(5), 1352–1361 (2013).

Gelinck, G. H. et al. Flexible active-matrix displays and shift registers based on solution-processed organic transistors. Nat. Mater. 3, 106–110 (2004).

Gupta, S. K., Jha, P., Singh, A., Chehimi, M. M. & Aswal, D. K. Flexible organic semiconductor thin films. J. Mater. Chem. 3, 8468–8479 (2015).

Cheng, T., Zhang, Y. Z., Lai, W. Y. & Huang, W. Stretchable Thin-Film Electrodes for Flexible Electronics with High Deformability and Stretchability. Adv. Mater. 27, 3349–3376 (2015).

Liu, Z., Xu, J., Chen, D. & Shen, G. Z. Flexible electronics based on inorganic nanowires. Chem. Soc. Rev. 44, 161–192 (2015).

Lee, C. H., Kim, D. R. & Zheng, X. L. Transfer Printing Methods for Flexible Thin Film Solar Cells: Basic Concepts and Working Principles. ACS Nano 8, 8746–8756 (2014).

Sun, Y. & Rogers, J. A. Inorganic semiconductors for flexible electronics. Adv. Mater. 19, 1897–1916 (2007).

Kaltenbrunner, M. et al. An ultra-lightweight design for imperceptible plastic electronics. Nature 499, 458–463 (2013).

Grau, G., Kitsomboonloha, R., Swisher, S. L., Kang, H. & Subramanian, V. Printed Transistors on Paper: Towards Smart Consumer Product Packaging. Adv. Funct. Mater. 24, 5067–5074 (2014).

Sekitani, T., Zschieschang, U., Klauk, H. & Someya, T. Flexible organic transistors and circuits with extreme bending stability. Nat. Mater. 9, 1015–1022 (2010).

Kamiya, T. & Hosono, H. Material characteristics and applications of transparent amorphous oxide semiconductors. NPG Asia Mater 2, 15–22 (2010).

Jo, J. W. et al. Highly Stable and Imperceptible Electronics Utilizing Photoactivated Heterogeneous Sol-Gel Metal-Oxide Dielectrics and Semiconductors. Adv. Mater. 27, 1182–1188 (2015).

Salvatore, G. A. et al. Wafer-scale design of lightweight and transparent electronics that wraps around hairs. Nat. Commun. 5, 2982 (2014).

Kim, J. S. et al. Effects of low-temperature (120 degrees C) annealing on the carrier concentration and trap density in amorphous indium gallium zinc oxide thin film transistors. J. Appl. Phys. 116, 245302 (2014).

Petti, L. et al. Influence of Mechanical Bending on Flexible InGaZnO-Based Ferroelectric Memory TFTs. IEEE Trans. Electron Devices 61, 1085–1092 (2014).

Jeon, S. et al. Nanometer-Scale Oxide Thin Film Transistor with Potential for High-Density Image Sensor Applications. ACS Appl. Mater. Interfaces 3, 1–6 (2011).

Geng, D., Kang, D. H. & Jang, J. High-Performance Amorphous Indium-Gallium-Zinc-Oxide Thin-Film Transistor With a Self-Aligned Etch Stopper Patterned by Back-Side UV Exposure. IEEE Electron Device Lett. 32, 758–760 (2011).

Zan, H. W., Yeh, C. C., Meng, H. F., Tsai, C. C. & Chen, L. H. Achieving high field-effect mobility in amorphous indium-gallium-zinc oxide by capping a strong reduction layer. Adv. Mater. 24, 3509–3514 (2012).

Wen, B. M., Sader, J. E. & Boland, J. J. Mechanical Properties of ZnO Nanowires. Phys. Rev. Lett. 101, 175502 (2008).

Chen, P. C. et al. High-Performance Single-Crystalline Arsenic-Doped Indium Oxide Nanowires for Transparent Thin-Film Transistors and Active Matrix Organic Light-Emitting Diode Displays. ACS Nano 3, 3383–3390 (2009).

Xing, Y. et al. Facile One-Step Fabrication of Ordered Ultra-Long Organic Microwires Film for Flexible Near-Infrared Photodetectors. J. Nanosci. Nanotechnol. 15, 4450–4456 (2015).

De Michielis, L., Moselund, K. E., Selmi, L. & Ionescu, A. M. Corner Effect and Local Volume Inversion in SiNW FETs. Nanotechnology. IEEE Trans. Nanotechnol. 10, 810–816 (2011).

Lee, S., Shin, J. & Jang, J. Top Interface Engineering of Flexible Oxide Thin-Film Transistors by Splitting Active Layer. Adv. Funct. Mater. 27, 1604921 (2017).

Rolland, A., Richard, J., Kleider, J. P. & Mencaraglia, D. Electrical-Properties of Amorphous-Silicon Transistors and Mis-Devices - Comparative-Study of Top Nitride and Bottom Nitride Configurations. J. Electrochem. Soc. 140, 3679–3683 (1993).

Jang, H. J., Gu, J. G. & Cho, W. J. Sensitivity enhancement of amorphous InGaZnO thin film transistor based extended gate field-effect transistors with dual-gate operation. Sens. Act. B. 181, 880–884 (2013).

Chen, T., Peng, H., Durstock, M. & Dai, L. High-performance transparent and stretchable all-solid supercapacitors based on highly aligned carbon nanotube sheets. Sci. Rep. 4, 3612 (2014).

Han, S. et al. Fast plasmonic laser nanowelding for a Cu-nanowire percolation network for flexible transparent conductors and stretchable electronics. Adv. Mater. 26, 5808–5814 (2014).

Pyo, J. B. et al. Floating compression of Ag nanowire networks for effective strain release of stretchable transparent electrodes. Nanoscale 7, 16434–16441 (2015).

Acknowledgements

This research was supported by BioNano Health-Guard Research Center funded by the Ministry of Science, ICT & Future Planning (MSIP) of Korea as Global Frontier Project (Grant number H-GUARD_2013M3A6B2078950) and the Brain Research Program through the National Research Foundation of Korea, South Korea (NRF) funded by the Ministry of Science, ICT and Future Planning (2015M3C7A1029113) and the KRIBB Initiative Research Program (KRIBB, Korea). The TFT fabrication and simulation from Jo and Cho at KWU was supported by the Basic Science Research Program through the National Research Foundation of Korea (NRF) funded by the Ministry of Education, Science and Technology (No. 2016R1A2B4008754). The participation of Katz, and of Jang at JHU, was supported by the National Institute of Biomedical Imaging and Bioengineering of the National Institutes of Health under award number R21EB018426. The content is solely the responsibility of the authors and does not necessarily represent the official views of the National Institutes of Health. The authors appreciate Mr. Suchang Mun’s graphical artworks.

Author information

Authors and Affiliations

Contributions

The NRs TFT development was carried out by H.-J.J., K.L. and K.-W.J. SEM analysis was performed by K.L. The device performance was estimated by H.-J.J and K.-W.J. The manuscript was prepared and data interpreted by H.-J.J., H.E.K., W.-J.C., and Y.-B.S. All authors examined and commented on the manuscript. The project was guided by Y.-B.S.

Corresponding authors

Ethics declarations

Competing Interests

The authors declare that they have no competing interests.

Additional information

Publisher's note: Springer Nature remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

Electronic supplementary material

Rights and permissions

Open Access This article is licensed under a Creative Commons Attribution 4.0 International License, which permits use, sharing, adaptation, distribution and reproduction in any medium or format, as long as you give appropriate credit to the original author(s) and the source, provide a link to the Creative Commons license, and indicate if changes were made. The images or other third party material in this article are included in the article’s Creative Commons license, unless indicated otherwise in a credit line to the material. If material is not included in the article’s Creative Commons license and your intended use is not permitted by statutory regulation or exceeds the permitted use, you will need to obtain permission directly from the copyright holder. To view a copy of this license, visit http://creativecommons.org/licenses/by/4.0/.

About this article

Cite this article

Jang, HJ., Joong Lee, K., Jo, KW. et al. Top-down Fabrication and Enhanced Active Area Electronic Characteristics of Amorphous Oxide Nanoribbons for Flexible Electronics. Sci Rep 7, 5728 (2017). https://doi.org/10.1038/s41598-017-06040-2

Received:

Accepted:

Published:

DOI: https://doi.org/10.1038/s41598-017-06040-2

Comments

By submitting a comment you agree to abide by our Terms and Community Guidelines. If you find something abusive or that does not comply with our terms or guidelines please flag it as inappropriate.