Abstract

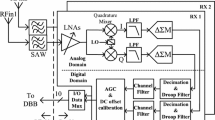

A 70-MHz continuous-time CMOS band-pass ΣΔ modulator for GSM receivers is presented. Impulse-invariant-transformation is used to transform a discrete-time loop-filter transfer function into continuous-time. The continuous-time loop-filter is implemented using a transconductor-capacitor (G m -C) filter. A latched-type comparator and a true-single-phase-clock (TSPC) D flip-flop are used as the quantizer of the ΣΔ modulator. Implemented in a MOSIS HP 0.5-μm CMOS technology, the chip area is 857 μm × 420 μm, and the total power consumption is 39 mW. At a supply voltage of 2.5 V, the maximum SNDR is measured to be 42 dB, which corresponds to a resolution of 7 bits.

Similar content being viewed by others

References

Norsworthy, S. R., Schreier, R. and Temes, G. C., “Delta-sigma data converters: Theory, design, and simulation.” IEEE Press, 1998.

Aziz, P. M., Sorensen, H. V. and Spiegel, J. V., “An overview of sigma-delta converters.” IEEE Signal Processing Magazine, pp.61–84, January 1996.

Singor, F. W. and Snelgrove, W. M., “Switched-capacitor bandpass delta-sigma A/D modulation at 10.7 MHz.” IEEE J. of Solid-State Circuits 30(3), pp. 184–192, March 1995.

Luh, L., Choma, J. and Draper, J., “A 50-MHz continuous-time switched-current ΣΔ modulator,” in Proceedings of IEEE International Symp. on Circuits & Systems, June 1998.

Bazarjani, S. and Snelgrove, M., “A 40 MHz IF fourth-order double-sampled SC bandpass ΣΔ modulator,” in Proceedings of IEEE International Symp. on Circuits & Systems, June 1997.

Ong, A. K. and Wooley, B. A., “A two-path bandpass sigma delta modulator for digital IF extraction at 20 MHz.” IEEE J. of Solid-State Circuits 32(12), pp. 1920–1934, December 1997.

Shoaei, O., “Continuous-time delta-sigma A/D converters for high-speed applications.” Ph.D. dissertation, Carleton Univ., Ottawa, Ont., Canada, February 1996.

Yukawa, A., “A CMOS 8-bit high-speed A/D converter IC.” IEEE J. of Solid-State Circuits SC-20(3), June 1985.

Ho, J. and Luong, H., “A 3-V 1.47 mW 120-MHz comparator for use in pipeline ADC,” in Proceedings of IEEE Asia-Pacific Conference on Circuits and Systems 96, pp.413–416, November 1996.

Piguet, C., “Logic circuit for bistable D-dynamic flip-flops.” US Patent 4,057,741.

Yuan, J. and Svensson, C., “High-speed CMOS circuit technique.” IEEE J. of Solid-State Circuits 24(2), pp. 62–70, 1989.

Chang, B., Park, J. and Kin, W., “A 1.2 GHz CMOS dual-modulus prescaler using new dynamic D-type flip-flops.” IEEE J. of Solid-State Circuits 31(5), pp. 749–752, May 1996.

Tao, H. and Khoury, J. M., “A 400-Ms/s frequency translating bandpass sigma-delta modulator.” IEEE J. of Solid-State Circuits 34(12), pp. 1741–1752, December 1999.

Gao, W. and Snelgrove, W. M., “A 950 MHz IF second-order integrated LC bandpass delta-sigma modulator.” IEEE J. of Solid-State Circuits 33(5), pp. 723–732, May 1998.

Author information

Authors and Affiliations

Rights and permissions

About this article

Cite this article

Hsu, I., Guo, C. & Luong, H.C. A 70-MHz Continuous-Time CMOS Band-Pass ΣΔ Modulator for GSM Receivers. Analog Integrated Circuits and Signal Processing 34, 189–199 (2003). https://doi.org/10.1023/A:1022597431615

Issue Date:

DOI: https://doi.org/10.1023/A:1022597431615