Abstract

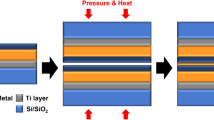

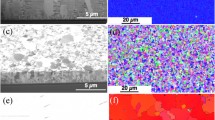

Diffusion of atoms across the boundary between two bonding layers is the key for achieving excellent thermocompression Wafer on Wafer bonding. In this paper, we demonstrate a novel mechanism to increase the diffusion across the bonding interface and also shows the CMOS in-line process flow compatible Sub 100 °C Cu–Cu bonding which is devoid of Cu surface treatment prior to bonding. The stress in sputtered Cu thin films was engineered by adjusting the Argon in-let pressure in such a way that one film had a compressive stress while the other film had tensile stress. Due to this stress gradient, a nominal pressure (2 kN) and temperature (75 °C) was enough to achieve a good quality thermocompression bonding having a bond strength of 149 MPa and very low specific contact resistance of 1.5 × 10−8 Ω-cm2. These excellent mechanical and electrical properties are resultant of a high quality Cu–Cu bonding having grain growth between the Cu films across the boundary and extended throughout the bonded region as revealed by Cross-sectional Transmission Electron Microscopy. In addition, reliability assessment of Cu–Cu bonding with stress engineering was demonstrated using multiple current stressing and temperature cycling test, suggests excellent reliable bonding without electrical performance degradation.

Similar content being viewed by others

References

Im, S., Banerjee, K.: Full chip thermal analysis of planar (2-D) and vertically integrated (3-D) high performance ICs. In: Electron Devices Meeting, pp. 727–730. IEEE (2000)

Xie, Y.: Processor architecture design using 3D integration technology. In: 23rd International Conference on VLSI Design, pp. 446–451. IEEE (2010)

Xu, Z., Lu, J.Q.: High-speed design and broadband modeling of through-strata-vias (TSVs) in 3D integration. IEEE Trans. Compon. Packag. Manuf. Technol. 1(2), 154–162 (2011)

Ko, C.T., Chen, K.N.: Wafer-level bonding/stacking technology for 3D integration. Microelectron. Reliab. 50(4), 481–488 (2010)

Save, D., Braud, F., Torres, J., Binder, F., Muller, C., Weidner, J.O., Hasse, W.: Electromigration resistance of copper interconnects. Microelectron. Eng. 33(1), 75–84 (1997)

Takagi, H., Kikuchi, K., Maeda, R., Chung, T.R., Suga, T.: Surface activated bonding of silicon wafers at room temperature. Appl. Phys. Lett. 68(16), 2222–2224 (1996)

Tan, C.S., Lim, D.F., Singh, S.G., Goulet, S.K., Bergkvist, M.: Cu–Cu diffusion bonding enhancement at low temperature by surface passivation using self-assembled monolayer of alkane-thiol. Appl. Phys. Lett. 95(19), 192108 (2009)

Ghosh, T., Krushnamurthy, K., Panigrahi, A.K., Dutta, A., Subrahmanyam, C., Vanjari, S.R.K., Singh, S.G.: Facile non thermal plasma based desorption of self assembled monolayers for achieving low temperature and low pressure Cu–Cu thermo-compression bonding. RSC Adv. 5(125), 103643–103648 (2015)

Huang, Y.P., Chien, Y.S., Tzeng, R.N., Shy, M.S., Lin, T.H., Chen, K.H., Chiu, C.T., Chiou, J.C., Chuang, C.T., Hwang, W., Tong, H.M., Chen, K.N.: Novel Cu-to-Cu bonding with Ti passivation at 180 °C in 3-D integration. IEEE Electron Device Lett. 34(12), 1551–1553 (2013)

Panigrahi, A.K., Bonam, S., Ghosh, T., Singh, S.G., Vanjari, S.R.K.: Ultra-thin Ti passivation mediated breakthrough in high quality Cu-Cu bonding at low temperature and pressure. Mater. Lett. 169, 269–272 (2016)

Huang, Y.P., Chien, Y.S., Tzeng, R.N., Chen, K.N.: Demonstration and electrical performance of Cu–Cu bonding at 150 °C with Pd passivation. IEEE Trans. Electron Devices 62(8), 2587–2592 (2015)

Panigrahi, A.K., Bonam, S., Ghosh, T., Vanjari, S.R.K., Singh, S.G.: High quality fine-pitch Cu–Cu wafer-on-wafer bonding with optimized Ti passivation at 160 °C. In: IEEE 66th Electronic Components and Technology Conference (ECTC), pp. 1791–1796 (2016)

Panigrahi, A.K., Ghosh, T., Vanjari, S.R.K., Singh, S.G.: Oxidation resistive, CMOS compatible copper based alloy ultrathin films as a superior passivation mechanism for achieving 150 °C Cu–Cu wafer on wafer thermocompression bonding. IEEE Trans. Electron Devices 64, 1239–1245 (2017)

Panigrahi, A.K., Ghosh, T., Vanjari, S.R.K., Singh, S.G.: Demonstration of Sub 150 °C Cu–Cu thermocompression bonding for 3D IC applications, utilizing an ultra-thin layer of Manganin alloy as an effective surface passivation layer. Mater. Lett. 194, 86–89 (2017)

Chua, C.L., Fork, D.K., Van Schuylenbergh, K., Lu, J.P.: Out-of-plane high-Q inductors on low-resistance silicon. J. Microelectromech. Syst. 12(6), 989–995 (2003)

Perry, J.L.: Effects of sputter deposition parameters on stress in tantalum films with applications to chemical mechanical planarization of copper (2014)

Agrawal, P.M., Rice, B.M., Thompson, D.L.: Predicting trends in rate parameters for self-diffusion on FCC metal surfaces. Surf. Sci. 515(1), 21–35 (2002)

Peng, L., Li, H.Y., Lim, D.F., Gao, S., Tan, C.S.: Thermal reliability of fine pitch Cu–Cu bonding with self assembled monolayer (SAM) passivation for Wafer-on-Wafer 3D-Stacking. In: IEEE 61st Electronic Components and Technology Conference (ECTC), pp. 22–26 (2011)

Enquist, P., Fountain, G., Petteway, C., Hollingsworth, A., Grady, H.: Low cost of ownership scalable copper direct bond interconnect 3D IC technology for three dimensional integrated circuit applications. In: IEEE International 3D Systems Integration Conference, pp. 1–6 (2009)

Beilliard, Y., Coudrain, P., Di Cioccio, L., Moreau, S., Sanchez, L., Montmayeul, B., Signamarcheix, T., Estevez, R., Parry, G.: Chip to wafer copper direct bonding electrical characterization and thermal cycling. In: IEEE 3D Systems Integration Conference (3DIC), pp. 1–7 (2013)

Acknowledgements

Authors are grateful for funding support from the Department of Electronics and Information Technology (DietY), Govt. of India and also characterization facilities through Indian Nano electronics User Program (INUP) program from Indian Institute of Technology-Bombay.

Author information

Authors and Affiliations

Corresponding author

Additional information

Asisa Kumar Panigrahi and Tamal Ghosh have contributed equally to this work.

Rights and permissions

About this article

Cite this article

Panigrahi, A.K., Ghosh, T., Kumar, C.H. et al. Direct, CMOS In-Line Process Flow Compatible, Sub 100 °C Cu–Cu Thermocompression Bonding Using Stress Engineering. Electron. Mater. Lett. 14, 328–335 (2018). https://doi.org/10.1007/s13391-018-0037-y

Received:

Accepted:

Published:

Issue Date:

DOI: https://doi.org/10.1007/s13391-018-0037-y