Abstract

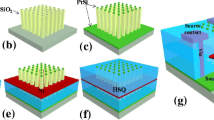

For the past four decades, the microelectronics industry has relied on silicon complementary MOS (metal oxide semiconductors). Because of their excellent characteristics, MOSFETs have become key components in VLSI. A new method for fabricating nano bridge arrays of various materials makes use of a sacrificial template structure: a suspended silicon nanowire array. This method produces nano bridge arrays of diverse materials. Energy harvesters such as thermoelectric micro/nano generators could be used to power Internet of Things sensors. According to the findings of this work, a planar micro/nano generator was constructed using silicon micromachining technologies and a thermoelectric material composed of silicon-germanium (SiGe) nanowire arrays. A top-down nanofabrication approach and electro-chemical lithography are utilised to produce silicon nanowires from SOI wafers using direct-write electron beam lithography (EBL). VLS (Vapor Liquid Solid Growth) was utilised to demonstrate monolithic integration of bottom-up nano wire arrays on pre-made micro platforms (CVD-VLS). It is demonstrated in this study that MacEtch may be used to manufacture Si NW arrays on vertically aligned Si wafers. Template-assisted manufacturing techniques have also been used to construct vertically aligned Si NW arrays with regulated diameter and number density.

Similar content being viewed by others

Data Availability

No supplementary materials.

References

Mallavarapu A et al (2021) Scalable fabrication and metrology of silicon nanowire arrays made by metal assisted chemical etch. IEEE Trans Nanotechnol 20:83–91. https://doi.org/10.1109/TNANO.2020.3047366

Yu J-M et al (2020) Quantitative analysis of high-pressure deuterium annealing effects on vertically stacked gate-all-around SONOS memory. IEEE Trans Electron Devices 67(9):3903–3907. https://doi.org/10.1109/TED.2020.3008882

Wendisch FJ et al (2020) Morphology-graded silicon nanowire arrays via chemical etching: Engineering optical properties at the nanoscale and macroscale. ACS Appl Mater Interfaces 12(11):13140–13147

Su Y, Lai J, Sun L (2020) Investigation of self-heating effects in vacuum gate dielectric gate-all-around vertically stacked silicon nanowire field effect transistors. IEEE Trans Electron Devices 67(10):4085–409. https://doi.org/10.1109/TED.2020.3017452

Wendisch FJ, Rey M, Vogel N, Bourret GR (2020) Large-scale synthesis of highly uniform silicon nanowire arrays using metal-assisted chemical etching. Chemistry of Materials, 32(21): 9425–9434

Chen S, Hellings G, Linten D, Mertens H, Mocuta A, Horiguchi N (2019) ESD protection diodes in bulk Si gate-all-around vertically stacked horizontal nanowire technology. IEEE Trans Device Mater Reliab 19(1):112–119. https://doi.org/10.1109/TDMR.2018.2886399

Sung P-J et al (2020) Fabrication of vertically stacked nanosheet junctionless field-effect transistors and applications for the CMOS and CFET inverters. IEEE Trans Electron Devices 67(9):3504–3509. https://doi.org/10.1109/TED.2020.3007134

de Oliveira AV, Veloso A, Claeys C, Horiguchi N, Simoen E (2020) Low–frequency noise in vertically stacked Si n–Channel Nanosheet FETs. IEEE Electron Device Lett 41(3):317–320. https://doi.org/10.1109/LED.2020.2968093

Chung CC-C, Ko C-M, Chao T-S (2019) Self-limited low-temperature trimming and fully silicided S/D for vertically stacked cantilever gate-all-around poly-Si junctionless nanosheet transistors. IEEE J Electron Devices Soc 7:959–963. https://doi.org/10.1109/JEDS.2019.2940606

Tsai M et al (2019) Fabrication and characterization of stacked poly-Si nanosheet with gate-all-around and multi-gate junctionless field effect transistors. IEEE J Electron Devices Soc 7:1133–1139. https://doi.org/10.1109/JEDS.2019.2952150

Lee VY, Henderson G, Karayiannis T (2019) Effect of inlet sub-cooling on flow boiling behaviour of HFE-7200 in a microchannel heat sink. In: Proc. 16th UK Heat Transf. Conf., pp 1–8

Park J-Y, Yun D-H, Kim S-Y, Choi Y-K (2019) Suppression of self-heating effects in 3-D V-NAND flash memory using a plugged pillar-shaped heat sink. IEEE Electron Device Lett 40(2):212–215

Kim H, Son D-K, Myeong I, Kang M, Shin H (2019) Analysis on self heating effect for a trenched source/drain structure in triplestacked nanowire FET. J Nanosci Nanotechnol 19(4):2281–2284

Ko H, Kang M, Jeon J, Shin H (2019) Device investigation of nanoplate transistor with spacer materials. IEEE Trans Electron Devices 66(1):766–770

Espineira G, Nagy D, Indalecio G, Garcia-Loureiro AJ, Kalna K, Seoane N (2019) Impact of gate edge roughness variability on FinFET and gate-all-around nanowire FET. IEEE Electron Device Lett 40(4):510–513

Chen S-H, Hellings G, Linten D, Mertens H, Mocuta A, Horiguchi N (2019) ESD protection diodes in bulk Si gate-all-around vertically stacked horizontal nanowire technology. IEEE Trans Device Mater Rel 19(1):112–119

Myeong I, Son D, Kim H, Kang M, Jeon J, Shin H (2019) Thermalaware shallow trench isolation design optimization for minimizing IOFF in various Sub-10-nm 3-D transistors. IEEE Trans Electron Devices 66(1):647–654

Zhang G et al (2019) Study on the thermal conductivity characteristics for ultra-thin body FD SOI MOSFETs based on phonon scattering mechanisms. Materials 12(16):2601

Li X, Park W, Wang Y, Chen YP, Ruan X (2019) Reducing interfacial thermal resistance between metal and dielectric materials by a metal interlayer. J Appl Phys 125(4), Art. no. 045302

Chung C-C, Lin HH, Wan WK, Yang M-T, Liu CW (2019) Thermal SPICE modeling of FinFET and BEOL considering frequency dependent transient response, 3-D heat flow, boundary/alloy scattering, and interfacial thermal resistance. IEEE Trans Electron Devices 66(6):2710–2714

Dutta M, Thirugnanam L, Fukata N (2018) Si nanowire solar cells: Principles, device types, future aspects, and challenges. Advances in Silicon Solar Cells. Springer, Cham, pp 299–329

Chung CC-C, Shen C-H, Lin J-Y, Chin C-C, Chao T-S (2018) Vertically stacked cantilever n-type poly-Si junctionless nanowire transistor and its series resistance limit. IEEE Trans Electron Devices 65(2):756–762. https://doi.org/10.1109/TED.2017.2780851

Subirats A et al (2018) Trap reduction and performances improvements study after high pressure anneal process on single crystal channel 3D NAND devices. In: IEDM Tech. Dig., San Francisco, CA, USA, pp 21–24 https://doi.org/10.1109/IEDM.2018.8614667

Capogreco E et al (2018) First demonstration of vertically stacked gate-all-around highly strained germanium nanowire pFETs. IEEE Trans Electron Devices 65(11):5145–5150. https://doi.org/10.1109/TED.2018.2871595

Cheng K (2017) (Invited) FinFET technology. ECS Trans 80(4):17–31

Duran JM, Sarangan A (2017) Fabrication of ultrahigh aspect ratio silicon nanostructures using self-assembled gold metal-assisted chemical etching. J Micro/Nanolithogr MEMS MOEMS 16(1):014502–014502

Al-Ameri T, Georgiev VP, Adamu-Lema F, Asenov A (2017) Simulation study of vertically stacked lateral Si nanowires transistors for 5-nm CMOS applications. IEEE J Electron Devices Soc 5(6):466–472. https://doi.org/10.1109/JEDS.2017.2752465

Li K et al (2017) Fabrication of hard x-ray zone plates with high aspect ratio using metal-assisted chemical etching. J Vac Sci Technol B Nanotechnol Microelectron 35(6), Art. no. 06G901

Park J-Y et al (2017) Investigation of self-heating effects in gate-all-around MOSFETs with vertically stacked multiple silicon nanowire channels. IEEE Trans Electron Devices 64(11):4393–4399. https://doi.org/10.1109/TED.2017.2749324

Bang T et al (2017) Low-frequency noise characteristics in SONOS flash memory with vertically stacked nanowire FETs. IEEE Electron Device Lett 38(1):40–43. https://doi.org/10.1109/LED.2016.2632182

Witters L et al (2017) Strained germanium gate-all-around pMOS device demonstration using selective wire release etch prior to replacement metal gate deposition. IEEE Trans Electron Devices 64(11):4587–4593. https://doi.org/10.1109/TED.2017.2756671

Prakash MD, Nihal SL, Ahmadsaidulu S, Swain R, Panigrahy AK (2022) Design and modelling of highly sensitive glucose biosensor for Lab-on-chip applications. Silicon. https://doi.org/10.1007/s12633-021-01543-0

Prakash MD, Nelam BG, Ahmadsaidulu S, Navaneetha A, Panigrahy AK (2021) Performance analysis of ion-sensitive field effect transistor with various oxide materials for biomedical applications. Silicon. https://doi.org/10.1007/s12633-021-01413-9

Prakash MD, Krsihna BV, Satyanarayana BVV, Vignesh NA, Panigrahy AK, Ahmadsaidulu S (2021) A study of an ultrasensitive label free silicon nanowire FET biosensor for cardiac Troponin I detection. Silicon. https://doi.org/10.1007/s12633-021-01352-5

Meriga C, Ponnuri RT, Satyanarayana BVV, Gudivada AAK, Panigrahy AK, Prakash MD (2021) A novel teeth junction less gate all around FET for improving electrical characteristics. Silicon. https://doi.org/10.1007/s12633-021-00983-y

Panigrahi AK, Ghosh T, Vanjari SRK, Singh SG (2017) Oxidation resistive, CMOS compatible copper-based alloy ultrathin films as a superior passivation mechanism for achieving 150 C Cu–Cu wafer on wafer thermocompression bonding. IEEE Trans Electron Devices 64(3):1239–1245

Krsihna BV, Chowdary GA, Ravi S, Reddy KV, Kavitha KR, Panigrahy AK, Prakash MD (2022) Tunnel field effect transistor design and analysis for biosensing applications. Silicon. https://doi.org/10.1007/s12633-022-01815-3

Deepa R, Devi MP, Vignesh NA, Kanithan S (2022) Implementation and performance evaluation of ferroelectric negative capacitance FET. Silicon. https://doi.org/10.1007/s12633-022-01722-7

Acknowledgements

The authors are thankful to Excel Engineering College, Namakkal, India for their cooperation and support during this research work.

Author information

Authors and Affiliations

Contributions

A Mohamedyaseen, P Suresh Kumar: Conceptualization; A Mohamedyaseen, P Suresh Kumar: investigation; A Mohamedyaseen, P Suresh Kumar, K. R. Kavitha, N. A. Vignesh: resources; A Mohamedyaseen, P Suresh Kumar: data curation; A Mohamedyaseen, P Suresh Kumar, K. R. Kavitha, N. A. Vignesh: writing—original draft preparation; A Mohamedyaseen, P Suresh Kumar, K. R. Kavitha, N. A. Vignesh: writing—review and editing; A Mohamedyaseen, P Suresh Kumar: visualization; P Suresh Kumar: supervision.

Corresponding author

Ethics declarations

Consent to Participate

Yes.

Conflict of Interest

The authors declare that they have no conflict of interest.

Research Involving Human Participants and/or Animals

This article does not contain any studies with human or animal subjects.

Consent for Publication

Author(s): A Mohamedyaseen.

Author’s signature:

Additional information

Publisher’s note

Springer Nature remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

Rights and permissions

About this article

Cite this article

Mohamedyaseen, A., Kumar, P.S., Kavitha, K.R. et al. Anisotropy Enhancing Vertically Aligned Silicon-Germanium Nanowire. Silicon 14, 12177–12184 (2022). https://doi.org/10.1007/s12633-022-01894-2

Received:

Accepted:

Published:

Issue Date:

DOI: https://doi.org/10.1007/s12633-022-01894-2