Abstract

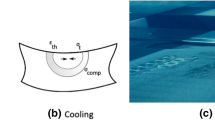

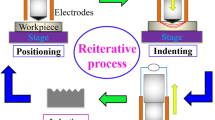

Grinding residual stresses of silicon wafers affect the performance of IC circuits. Based on the wafer rotation ultra-precision grinding machine, the residual stress distribution along grinding marks and ground surface layer depth of the ground wafers are investigated using Raman microspectroscopy. The results show that the ground wafer surfaces mainly present compressive stress. The vicinity of pile-ups between two grinding marks presents higher a compressive stress. The stress value of the rough ground wafer is the least because the material is removed by the brittle fracture mode. The stress of the semi-fine ground wafer is the largest because the wafer surface presents stronger phase transformations and elastic-plastic deformation. The stress of the fine ground wafer is between the above two. The strained layer depths for the rough, semi-fine, and fine ground wafers are about 7.6 μm, 2.6 μm, and 1.1 μm, respectively. The main reasons for generation of residual stresses are phase transformations and elastic-plastic deformation.

Similar content being viewed by others

References

Tönshoff H.K., Schmieden W.V., Inasakii I., König W., and Spur G., Abrasive machining of silicon, CIRP Ann. Manuf. Technol., 1990, 39(2): 621.

Pei Z.J. and Strasbaugh A., Fine grinding of silicon wafers: designed experiment, Int. J. Mach. Tool. Manuf., 2002, 42: 395.

Zarudi I. and Zhang L., Subsurface damage in single-crystal silicon due to grinding and polishing, J. Mater. Sci. Lett., 1996, 15: 586.

Chen J. and De Wolf I., Study of damage and stress induced by backgrinding in Si wafers, Semicond. Sci. Technol., 2003, 18: 261.

De Wolf I., Micro-Raman spectroscopy to study local mechanical stress in silicon integrated circuits, Semicond. Sci. Technol., 1996, 11: 139.

Chao C.L., Ma K.J., Chang Y., and Lin H.Y., Relieving the residual stress on machined silicon wafers: a comparison between rapid thermal annealing (RTA) and chemical etching processes, J. Chung Cheng Inst. of Technol., 2000, 29(1): 63.

Gogotsi Y., Zhou G.H., Ku S.S., and Cetinkunt S., Raman microspectroscopy analysis of pressure-induced metallization in scratching of silicon, Semicond. Sci. Technol., 2001, 16: 345.

Jardret V., Zahouani H., Loubet J.L., and Mathia T.G., Understanding and quantification of elastic and plastic deformation during a scratch test, Wear, 1998, 218: 8.

Zhang Y.X., Gao W., Kang R.K., and Guo D.M., Study on the hase transformations of the ground monocrystalline silicon wafers surfaces, Opt. Precis. Eng., 2008, 16(8): 1440.

Author information

Authors and Affiliations

Corresponding author

Rights and permissions

About this article

Cite this article

Zhang, Y., Wang, D., Gao, W. et al. Residual stress analysis on silicon wafer surface layers induced by ultra-precision grinding. Rare Metals 30, 278–281 (2011). https://doi.org/10.1007/s12598-011-0383-5

Received:

Revised:

Accepted:

Published:

Issue Date:

DOI: https://doi.org/10.1007/s12598-011-0383-5