Abstract

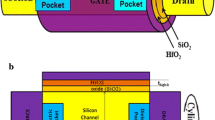

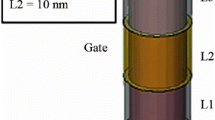

We report a systematic, quantitative investigation of analog and RF performance of cylindrical surrounding-gate (SRG) silicon MOSFET. To derive the model, a pseudo-two-dimensional (2-D) approach applying Gauss’s law in the channel region is extended for the cylindrical SRG MOSFET. Based on surface potential approach, expressions of drain current and differential capacitances are obtained analytically. Analog/RF figures of merit of SRG MOSFET are studied, including transconductance efficiency g m/I d, intrinsic gain, output resistance, cutoff frequency f T, maximum oscillation frequency f max and gain bandwidth product GBW. The trends related to their variations along the downscaling of dimension are provided. In order to validate our model, the modeled predictions have been extensively compared with the simulated characteristics obtained from the ATLAS device simulator and a nice agreement is observed with a wide range of geometrical parameters.

Similar content being viewed by others

References

ITRS.: International Technology Roadmap for Semiconductors. http://www.itrs.net (2009). Accessed 26 May 2009

Auth, C.P., Plummer, J.D.: Scaling theory for cylindrical, fully-depleted, surrounding-gate MOSFETs. IEEE Electron Device Lett. 18(2), 74–76 (1997)

Dupré, C., Ernst, T., Arvet, C., Aussenac, F., Deleonibus, S., Ghibaudo, G.: Stacked nanowires ΦFET with independent gates:novel device for ultra-dense low power applications. In: Proc. IEEE Int. SOI Conf. 2007, pp. 95–96. IEEE Press, New York (2007)

Weber, O., Faynot, O., Andrieu, F., Buj-Dufournet, C., Allain, F., Scheiblin, P., Foucher, J., Daval, N., Lafond, D., Tosti, L., Brevard, L., Rozeau, O., Fenouillet-Beranger, C., Marin, M., Boeuf, F., Delprat, D., Bourdelle, K., Nguyen, B.-Y., Deleonibus, S.: High immunity to threshold voltage variability in undoped ultra-thin FDSOI MOSFETs and its physical understanding. In: Proc. Electron Devices Meeting IEDM’08, pp. 1–4. IEEE Press, New York (2008)

Oh, S.H., Monore, D., Hergenrother, J.M.: Analytical description of short-channel effects in fully-depleted double-gate and cylindrical, surrounding-gate MOSFETs. IEEE Electron Device Lett. 21(9), 445–447 (2000)

Yang, F.L., et al.: 5 nm-Gate nanowire FinFET. Proc. VLSI Symp. Tech. Dig. 5, 196–197 (2004)

Paul, B.C., Raychowdhury, A., Roy, K.: Device optimization for digital subthreshold logic operation. IEEE Trans. Electron Devices 52(2), 237–247 (2005)

Vittoz, E., Fellrath, J.: CMOS analog integrated circuits based on weak inversion operation. IEEE J. Solid-State Circuits SC-12(1), 224–231 (1977)

Wang, R., Zhuge, J., Huang, R., Tian, Y., Xiao, H., Zhang, L., Li, C., Zhang, X., Wang, Y.: Analog/RF performance of Si nanowire MOSFETs and the impact of process variation. IEEE Trans. Electron Devices 54(6), 1288–1294 (2007)

Iniguez, B., Jimenez, D., Roig, J., Hamid, H.A., Marsal, L.F., Pallares, J.: Explicit continuous model for long-channel undoped surrounding gate MOSFETs. IEEE Trans. Electron Devices 52(8), 1868–1873 (2005)

Jang, S.L., Liu, S.S.: An analytical surrounding gate MOSFET model. Solid-State Electron. 42(5), 721–728 (1998)

Jimenez, D., Iniguez, B., Sune, J., Marsal, L.F., Pallares, J., Roig, J., Flores, D.: Continuous analytic current–voltage model for surrounding-gate MOSFETs. IEEE Electron Device Lett. 25(8), 571–573 (2004)

Cheralathan, M., Cerdeira, A., Iniguez, B.: Compact model for long-channel cylindrical surrounding-gate MOSFETs valid from low to high doping concentrations. Solid-State Electron. 55(1), 13–18 (2011)

Cousin, B., Reyboz, M., Rozeau, O., Jaud, M., Ernst, T., Jomaah, J.: A unified short-channel compact model for cylindrical surrounding-gate MOSFET. Solid-State Electron. 56(1), 40–46 (2011)

Yu, B., Yuan, Y., Song, J., Taur, Y.: A two-dimensional analytical solution for short-channel effects in nanowire MOSFETs. IEEE Trans. Electron Devices 56(10), 2357–2362 (2009)

Moldovan, O., Iniguez, B., Jimenez, D., Roig, J.: Analytical charge and capacitance models of undoped cylindrical surrounding-gate MOSFETs. IEEE Trans. Electron Devices 54(1), 162–165 (2007)

Jimenez, D., Saenz, J.J., Iniguez, B., Sune, J., Marsal, L.F., Pallares, J.: Modeling of nanoscale gate-all-around MOSFETs. IEEE Electron Device Lett. 25(5), 314–316 (2004)

He, J., Zhang, X., Zhang, G., Chan, M.: A carrier-based DCIV model for long channel undoped cylindrical surrounding-gate MOSFETs. Solid-State Electron. 50(3), 416–421 (2006)

Pao, H.C., Sah, C.T.: Effects of diffusion current on characteristics of metal-oxide (insulator)-semiconductor transistors. Solid-State Electron. 9, 927 (1966)

Kranti, A., Haldar, R.S., Gupta, R.S.: Optimization for improved short channel performance of surrounding/cylindrical gate MOSFETs. Electron. Lett. 37(12), 533–534 (2001)

Bian, W., He, J., Tao, Y., Fang, M., Feng, J.: An analytical potential-based model for undoped nanoscale surrounding-gate MOSFETs. IEEE Trans. Electron Devices 54(9), 2293–2303 (2007)

Borli, H., Kolberg, S., Fjeldly, T.A., Iniguez, B.: Precise modeling framework for short-channel double-gate and gate-all-around MOSFETs. IEEE Trans. Electron Devices 55(10), 2678–2686 (2008)

Kranti, A., Haldar, S., Gupta, R.S.: Analytical model for threshold voltage and I–V characteristics of fully depleted short channel cylindrical/surrounding gate MOSFET. Microelectron. Eng. 56, 241–259 (2001)

Kumar, M.J., Orouji, A.A., Dhakad, H.: New dual-material surrounding gate nanoscale MOSFET: analytical threshold voltage model. IEEE Trans. Electron Devices 53(4), 920–923 (2006)

Sarkar, A., De, S., Dey, A., Sarkar, C.K.: A new analytical subthreshold model of SRG MOSFET with analogue performance investigation. Int. J. Electron. 99(2), 267–283 (2012)

Baishya, S., Mallik, A., Sarkar, C.K.: A subthreshold surface potential model for short-channel MOSFET taking into account the varying depth of channel depletion layer due to source and drain Junctions. IEEE Trans. Electron Devices 53(3), 507–514 (2006)

Lundstrom, M.S., Guo, J.: Nanoscale Transistors: Device Physics, Modeling and Simulation. Springer, New York (2006)

Woerlee, P.H., Knitel, M.J., Langevelde, R.V., Klaassen, D.B.M., Tiemeijer, L.F., Scholten, A.J., Zegers-van Duijnhoven, A.T.A.: RF CMOS performance trends. IEEE Trans. Electron Devices 48(8), 1776–1782 (2001)

Momose, H.S., Monfuzi, E., Yoshitomi, T., Ohguro, T., Saito, M., Morimoto, T., Katsumata, Y., Iwai, H.: High frequency AC characteristics of 1.5-nm gate oxide MOSFETs. In: Proc. Electron Devices Meeting IEDM’96, pp. 105–107. IEEE Press, New York (1996)

Lazaro, A., Iniguez, B.: RF and noise model of gate-all-around MOSFETs. Semicond. Sci. Technol. 23(7), 075022 (2008)

Nae, B., Lazaro, A., Iniguez, B.: High frequency and noise model of gate-all-around metal-oxide-semiconductor field-effect transistors. J. Appl. Phys. 105(7), 074505 (2009)

Device simulator ATLAS user manual.: Silvaco Int., Santa Clara, CA. http://www.silvaco.com. Accessed 26 May 2011

Corless, R.M., Gonnet, G.H., Hare, D.E.G., Jeffrey, D.J., Knuth, D.E.: On the Lambert W function. Adv. Comput. Math. 5, 329–359 (1996)

Pala, M.G., Buran, C., Poli, S., Mouis, M.: Full quantum treatment of surface roughness effects in Silicon nanowire and double gate FETs. J. Comput. Electron. 8(3–4), 374–381 (2009)

Cerdeira, A., Iñiguez, B., Estrada, M.: Compact model for short channel symmetric doped double-gate MOSFETs. Solid-State Electron. 52(7), 1064–1070 (2008)

Yamaguchi, K.: A mobility model for carriers in the MOS inversion layer. IEEE Trans. Electron Devices 30(6), 658–663 (1983)

Ghosh, P., Haldar, S., Gupta, R.S., Gupta, M.: An analytical drain current model for dual material engineered cylindrical/surrounded gate MOSFET. Microelectron. J. 43, 17–24 (2012)

Ward, D.E., Dutton, R.W.: A charge-oriented model for MOS transistor capacitances. IEEE J. Solid-State Circuits SSC-13(5), 703–708 (1978)

Pailloncy, G., Raynaud, C., Vanmackelberg, M., Danneville, F., Lepilliet, S., Raskin, J.P., Dambrine, G.: Impact of downscaling on high-frequency noise performance of bulk and SOI MOSFETs. IEEE Trans. Electron Devices 51(10), 1605–1612 (2004)

Mohankumar, N., Syamal, B., Sarkar, C.K.: Influence of channel and gate engineering on the analog and RF performance of DG MOSFETs. IEEE Trans. Electron Devices 57(4), 820–826 (2010)

Enz, C.C., Vittoz, E.A.: Charge-Based MOS Transistor Modeling: The EKV Model for Low-Power and RF IC Design. Wiley, New York (2006)

Lim, T.C., Bernard, E., Rozeau, O., Ernst, T., Guillaumot, B., Vulliet, N., Buj-Dufournet, C., Paccaud, M., Lepilliet, S., Dambrine, G., Danneville, F.: Analog/RF performance of multichannel SOI MOSFET. IEEE Trans. Electron Devices 56(7), 1473–1482 (2009)

Kim, S.-H., Fossum, J.G., Yang, J.-W.: Modeling and significance of fringing capacitance in nonclassical CMOS devices with gate source/drain underlap. IEEE Trans. Electron Devices 53(9), 2143–2150 (2006)

Dambrine, G., Raynaud, C., Lederer, D., Dehan, M., Rozeaux, O., Vanmackelberg, M., Danneville, F., Lepilliet, S., Raskin, J.P.: What are the limiting parameters of deep-submicron MOSFETs for high frequency applications. IEEE Electron Device Lett. 24(3), 189–191 (2003)

Mohney, S.E., Wang, Y., Cabassi, M.A., Lew, K.K., Dey, S., Redwing, J.M., Mayer, T.S.: Measuring the specific contact resistance of contacts to semiconductor nanowires. Solid-State Electron. 49, 227–232 (2005)

Shenoy, R.S., Saraswat, K.C.: Optimization of extrinsic source/ drain resistance in ultrathin body double-gate FETs. IEEE Trans. Nanotechnol. 2(4), 265–270 (2003)

Zhuge, J., Wang, R., Huang, R., Zhang, X., Wang, Y.: Investigation of parasitic effects and design optimization in silicon nanowire MOSFETs for RF applications. IEEE Trans. Electron Devices 55(8), 2142–2147 (2008)

Jin, X., Ou, J.J., Chen, C.H., Liu, W., Deen, M.J., Gray, P.R., Hu, C.: An effective gate resistance model for CMOS RF and noise modeling. In: Proc. Electron Devices Meeting IEDM’98, p. 9. IEEE Press, New York (1998)

Wernersson, L.-E., Thelander, C., Lind, E., Samuelson, L.: III–V Nanowires—extending a narrowing road. Proc. IEEE 98(12), 2047–2060 (2010)

Dupré, C., Ernst, T., Maffini-Alvaro, V., Delaye, V., Hartmann, J.-M., Borel, S., Vizioz, C., Faynot, O., Ghibaudo, G., Deleonibus, S.: 3D nanowire gate-all-around transistors: Specific integration and electrical features. Solid-State Electron. 52(4), 813–816 (2008)

Singh, N., Buddharaju, K.D., Manhas, S.K., Agarwal, A., Rustagi, S.C., Lo, G.Q., Balasubramanian, N., Kwong, D.-L.: Si, SiGe nanowire devices by top–down technology and their applications. IEEE Trans. Electron Devices 55(11), 3107–3118 (2008)

Cui, Y., Zhong, Z., Wang, D., Wang, W.U., Lieber, C.M.: High performance silicon nanowire field effect transistors. Nano Lett. 3(2), 149–152 (2003)

Zou, J., Xu, Q., Luo, J., Wang, R., Huang, R., Wang, Y.: Predictive 3-D modeling of parasitic gate capacitance in gate-all-around cylindrical silicon nanowire MOSFETs. IEEE Trans. Electron Devices 58(10), 3379–3387 (2011)

Wei, L., Lan, D.J., Wong, H.-S.P.: Effect, 1-D and 2-D devices performance comparison including parasitic gate capacitance and screening. Proc. Int. Elec. Dev. Meeting 741–744 (2007)

Deng, J., Wong, H.-S.P.: Modeling and analysis of planar-gate electrostatic capacitance of 1-D FET with multiple cylindrical conducting channels. IEEE Trans. Electron Devices 54(9), 2377–2385 (2007)

Wei, L., Deng, J., Chang, L.-W., Kim, K., Chuang, C.-T., Wong, H.-S.P.: Selective device structure scaling and parasitic engineering: A way to extend the technology roadmap. IEEE Trans. Electron Devices 56(2), 312–320 (2009)

Acknowledgement

The authors would like to thank the DST, Govt. of India for its financial assistance in carrying out research activities.

Author information

Authors and Affiliations

Corresponding author

Rights and permissions

About this article

Cite this article

Sarkar, A., De, S., Dey, A. et al. Analog and RF performance investigation of cylindrical surrounding-gate MOSFET with an analytical pseudo-2D model. J Comput Electron 11, 182–195 (2012). https://doi.org/10.1007/s10825-012-0396-9

Published:

Issue Date:

DOI: https://doi.org/10.1007/s10825-012-0396-9